Устройство ультразвуковой томографии

Иллюстрации

Показать всеИспользование: для визуализации ультразвуковой дефектоскопии трехмерного изделия. Сущность изобретения заключается в том, что устройство ультразвуковой томографии содержит антенную решетку с n приемно-передающими элементами, каждый из которых соединен с выходом соответствующего генератора импульсов и входом соответствующего усилителя, n аналого-цифровых преобразователей соединены с соответствующими входами блока памяти реализации, количество выходов которого - N определено формулой N=n·(n+1)/2. Выходы блока памяти реализации соединены с соответствующими входами вычислительного блока, связанного с индикатором через блок памяти изображений и с блоком накопительной памяти. Входы синхронизации каждого генератора импульсов, блока памяти реализаций, вычислительного блока и блока памяти изображений соединены с соответствующими выходами блока синхронизации. Блок временной регулировки чувствительности соединен с блоком синхронизации и всеми усилителями. Блок мультипликативной обработки соединен с вычислительным блоком и блоком накопительной памяти. К выходу каждого усилителя подключен детектор, выход которого связан с аналого-цифровым преобразователем. Технический результат: улучшение четкости визуализации полученного изображения контролируемого изделия за счет увеличения разрешающей способности. 5 ил., 1 табл.

Реферат

Изобретение относится к области анализа с помощью ультразвуковых волн материалов или изделий из металлов, керамики, пластмасс и может быть использовано в промышленности для контроля дефектов внутри деталей, для дефектоскопии различных материалов, а также в медицине для диагностики внутренних органов.

Известно устройство формирования акустического изображения контролируемого объекта [RU 2246723 С1, МПК7 G01N29/04, опубл. 20.02.2005], содержащее первый генератор, выход которого соединен со входом первого передающего пьезопреобразователя, второй генератор, выход которого соединен со входом второго передающего пьезопреобразователя, первый приемный пьезопреобразователь, выход которого соединен с первым приемным устройством, второй приемный пьезопреобразователь, выход которого соединен с вторым приемным устройством. Выходы первого и второго приемных устройств соединены с первым и вторым входами запоминающего устройства, выход которого подключен ко входу электронно-вычислительного блока, к первому и второму выходам которого подключены, соответственно, входы первого и второго генераторов. Передающие пьезопреобразователи размещены на поверхности контролируемого объекта. Приемные пьезопреобразователи выполнены с возможностью их перемещения по поверхности контролируемого объекта.

Недостатком этого устройства является необходимость последовательного расположения в различных точках на поверхности контролируемого объекта первого и второго приемных пьезопреобразователей и сложность сравнения каждой из М пар предварительных изображений.

Известно устройство ультразвуковой томографии [RU 2458342 МПК G01N29/06 (2006.01), опубл. http://www.fips.ru/cdfi/fips.dll?ty=29&docid=2458342&cl=9&path=http://195.208.85.248/Archive/PAT/2012FULL/2012.08.10/DOC/RUNWC1/000/000/002/458/342/document.pdf" \], выбранное в качестве прототипа, содержащее антенную решетку с n приемно-передающими элементами, каждый из которых соединен с выходом соответствующего генератора импульсов и входом соответствующей цепочки последовательно соединенных усилителя и аналого-цифрового преобразователя, выход каждой из n указанных цепочек соединен с соответствующим входом памяти реализаций, количество выходов которой N определяется формулой:

N=n·(n+1)/2,

выходы памяти реализаций соединены с соответствующими входами вычислительного блока, который связан с блоком накопительной памяти и с дисплеем через память изображения. Входы синхронизации каждого генератора импульсов, памяти реализаций, вычислительного блока и памяти изображения соединены с соответствующими выходами синхронизатора.

Недостатком известного устройства является низкая разрешающая способность, определяемая шириной главного лепестка синтезированной диаграммы направленности антенной решетки, состоящей из n приемно-передающих элементов, разная чувствительность на разных глубинах объекта контроля, определяемая коэффициентом усиления усилителя, низкое отношение сигнал/шум и ограничение по использованию только при ультразвуковой диагностике плоских металлоконструкций определенной толщины.

Задачей изобретения является улучшение четкости визуализации полученного изображения контролируемого изделия за счет увеличения разрешающей способности.

Поставленная задача решена за счет того, что устройство ультразвуковой томографии, также как в прототипе, содержит антенную решетку с n приемно-передающими элементами, каждый из которых соединен с выходом соответствующего генератора импульсов и входом соответствующего усилителя, n аналого-цифровых преобразователей соединены с соответствующими входами блока памяти реализации, количество выходов которого - N определено формулой

N=n·(n+1)/2,

выходы блока памяти реализации соединены с соответствующими входами вычислительного блока, связанного с индикатором через блок памяти изображений и с блоком накопительной памяти, при этом входы синхронизации каждого генератора импульсов, блока памяти реализаций, вычислительного блока и блока памяти изображений соединены с соответствующими выходами блока синхронизации.

Согласно изобретению блок временной регулировки чувствительности соединен с блоком синхронизации и всеми усилителями, а блок мультипликативной обработки соединен с вычислительным блоком и блоком накопительной памяти, при этом к выходу каждого усилителя подключен детектор, выход которого связан с аналого-цифровым преобразователем.

За счет использования блока временной регулировки чувствительности обеспечивается компенсация затухания ультразвукового сигнала по мере распространения в объекте контроля и соответственно поддерживается одинаковая чувствительность на разных глубинах объекта контроля. Использование блока мультипликативной обработки, в котором производится когерентное умножение сигналов без переотражений от донной и внешней поверхности объекта контроля, позволяет сузить ширину главного лепестка синтезированной диаграммы направленности антенной решетки. Это улучшает четкость визуализации полученного изображения объекта контроля за счет увеличения разрешающей способности, при которой возможна раздельная визуализация нескольких рядом расположенных дефектов, а также увеличивает отношение сигнал/шум.

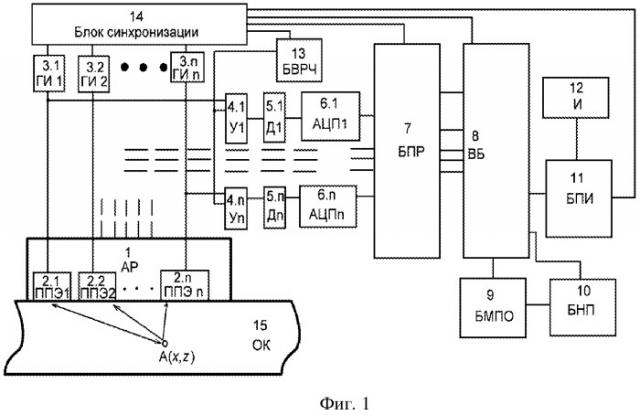

На фиг. 1 представлена функциональная схема устройства ультразвуковой томографии.

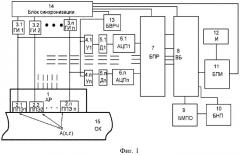

На фиг. 2 представлена функциональная схема устройства блока мультипликативной обработки.

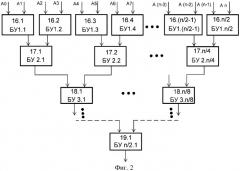

На фиг. 3 представлена функциональная схема устройства блока перемножения двух чисел.

На фиг. 4 показаны результаты визуализации ультразвуковой дефектоскопии колесной оси, полученные с использованием: а - прототипа, б - заявляемого устройства, где на а и б слева представлено томографическое изображение продольного сечения колесной оси по диаметру, а справа - поперечное сечение колесной оси.

На фиг. 5 представлены результаты визуализации ультразвуковой дефектоскопии двух точечных дефектов, расположенных на расстоянии 2,4 мм друг от друга, полученные с использованием: а - прототипа, б - предлагаемого устройства.

В таблице 1 представлен пример перемножения двух чисел.

Устройство ультразвуковой томографии (фиг. 1) содержит антенную решетку 1 (АР), которая состоит из n приемно-передающих элементов 2.1 (ППЭ1), …, 2.n (ППЭn), каждый из которых соединен с выходом соответствующего генератора импульсов 3.1 (ГИ1), …, 3.n (ГИn) и входом соответствующей цепочки последовательно соединенных усилителя 4.1 (У1), детектора 5.1 (Д1) и аналого-цифрового преобразователя 6.1 (АЦП1), …, усилителя 4.n (Уn), детектора 5.n (Дn) и аналого-цифрового преобразователя 6.n (АЦПn).

Выход каждого аналогово-цифрового преобразователя 6.1 (АЦП1), …., 6.n (АЦПn) соединен с соответствующим входом блока памяти реализаций 7 (БПР), количество выходов которого определяется формулой N=n·(n+1)/2. Выходы блока памяти реализаций 7 (БПР) соединены с соответствующими входами вычислительного блока 8 (ВБ), связанного с входом блока мультипликативной обработки 9 (БМПО), выход которого подключен к блоку накопительной памяти 10 (БНП). Вычислительный блок 8 (ВБ) соединен с выходом блока накопительной памяти 10 (БНП) и с входом блока памяти изображений 11 (БПИ), который соединен с индикатором 12 (И). Входы каждого генератора импульсов 3.1 (ГИ1), …, 3.n (ГИn), блока памяти реализаций 7 (БПР), вычислительного блока 8 (ВБ), блока памяти изображений 11 (БПИ) и блока временной регулировки чувствительности 13 (БВРЧ) соединены с блоком синхронизации 14 (БС). Выход блока временной регулировки чувствительности 13 (БВРЧ) подключен к каждому усилителю 4.1 (У1), …, 4.n (Уn). Антенная решетка 1 (АР) установлена на объекте контроля 15 (ОК).

Блок мультипликативной обработки 9 (БМПО) состоит из идентичных блоков умножения (фиг. 2), соединенных пирамидально, так что первый уровень содержит n/2 блоков умножения 16.1 (БУ1.1), …, 16.n/2 (БУ1.n/2), входы которых соединены с вычислительным блоком 8 (ВБ). Выходы двух блоков умножения первого уровня 16.1 (БУ1.1) и 16.2 (БУ1.2) связаны с входами одного блока умножения второго уровня 17.1 (БУ2.1). Выходы двух блоков умножения первого уровня 16.3 (БУ1.3) и 16.4 (БУ1.4) связаны с входами одного блока умножения второго уровня 17.2 (БУ2.2). Выходы двух блоков умножения первого уровня 16.(n/2-1) (БУ1.(n/2-1)) и 16.n/2 (БУ1.n/2) связаны с входами одного блока умножения второго уровня 17.n/4 (БУ2.n/4). Выходы двух блоков умножения второго уровня 17.1 (БУ2.1) и 17.2 (БУ2.2) связаны с входами одного блока умножения третьего уровня 18.1 (БУ3.1) и т.д. Выходы блоков умножения третьего уровня 18.1 (БУ3.1) и 18.n/8 (БУ3.n/8) связаны с входом блока умножения n-го уровня 19.1 (БУn/2.1), выход которого является выходом блока мультипликативной обработки 9 (БМПО).

Структурная схема всех блоков умножения 16.1 (БУ1.1), …, 16.n/2 (БУ1.n/2), 17.1 (БУ2.1), …, 17.n/2 (БУ2.n/4), 18.1 (БУ3.1), …, 18.n/8 (БУ3.n/8), …, 19.1 (БУn/2.1) одинакова (фиг. 3). Например, в блоке умножения 16.1 (БУ1.1) вход регистра первого числа 20 связан с вычислительным блоком 8 (ВБ), а первый выход регистра первого числа 20 соединен с входом первого регистра второго числа 21.1. Второй выход регистра первого числа 20 соединен с входом второго регистра второго числа 21.2, а n-й выход регистра первого числа 20 соединен с входом n-го регистра второго числа 21.n. Входы регистров второго числа 21.1, …, 21.n связаны с вычислительным блоком 8 (ВБ). Выходы регистров второго числа 21.1, …, 21.n соединены с входами сумматора 22. Выход сумматора 22 является выходом каждого блока умножения 16.1 (БУ1.1), …, 16.n/2 (БУ1.n/2), 17.1 (БУ2.1), …, 17.n/2 (БУ2.n/4), 18.1 (БУ3.1), …, 18.n/8 (БУ3.n/8), …, 19.1 (БУn/2.1).

Антенная решетка 1 (АР) является набором 16 или более приемно-передающих элементов, располагаемых линейно или матрично, например OLYMPUS 2L16-A1. Генераторы импульсов 3.1 (ГИ1), …, 3.n (ГИn) выполнены на микросхемах, имеющих импульсный ток коллектора не менее 2А и выходное напряжение 90 В, например STHV748. Усилители 4.1 (У1), …, 4.n (Уn) выполнены по типовой схеме, например на микросхемах AD603. Детекторы 5.1 (Д1), …, 5.n (Дn) выполнены по типовой схеме на операционном усилителе, например AD603. Аналого-цифровые преобразователи 6.1 (АЦП1), …., 6.n (АЦПn) выполнены по типовой схеме, например на микросхемах ADС9057. Блок памяти реализаций 7 (БПР), объемом не менее 64 Кб, выполнен на типовых микросхемах, например на микросхемах IDT72V293. Вычислительный блок 8 (ВБ) может быть выполнен на микроконтроллере, например ATMEGA64, фирмы ATMEL. Блок накопительной памяти 10 (БНП) и блок памяти изображений 11 (БПИ) объемом не менее 100 МГб могут быть выполнены, например, на модулях памяти, используемых в персональных компьютерах, 1ГБ DDR SDRAM PC3200, 400МГц. Индикатор 12 (И) может быть выполнен на матричной панели или на мониторе персонального компьютера, например BENQ G2320HDB. Блок временной регулировки чувствительности 13 (БВРЧ) может быть выполнен на цифро-аналоговом преобразователе, входящем в состав микроконтроллера, например ATMEGA64, фирмы ATMEL. Блок синхронизации 14 (БС) может быть выполнен на микроконтроллере, например ATMEGA64, фирмы ATMEL. Регистр первого числа 20 и регистры второго числа 21.1, …, 21.n выполнены на типовых микросхемах, например К1533ИР23, сумматор 22 может быть выполнен на типовых микросхемах сумматоров, например К1533ИМ3.

Устройство работает следующим образом.

При контроле, например, колесной оси размещали на ее торце антенную решетку 1 (АР), содержащую 32 приемно-передающих элемента 2.1 (ППЭ1), …, 2.32 (ППЭ32), расположенных матрично. По сигналу от блока синхронизации 14 (БС) первый генератор импульсов 3.1 (ГИ1) подавал импульс возбуждения на первый приемо-передающий элемент 2.1 (ППЭ1) антенной решетки 1 (АР). В объект контроля 15 (ОК) излучался зондирующий импульс. В этот момент все приемо-передающие элементы 2.1 (ППЭ1), …, 2.32 (ППЭ32) антенной решетки 1 (АР) начинают принимать ультразвуковые (УЗ) колебания из объекта контроля 15 (ОК). Одновременно блок временной регулировки чувствительности 13 (БВРЧ) начинает изменять коэффициент усиления усилителей 4.1 (У1), …, 4.32 (У32), компенсируя таким образом затухание ультразвуковой волны в объекте контроля 15 (ОК). Эти колебания, преобразованные в электрические колебания, усиливаются в усилителях 4.1 (У1), …, 4.32 (У32), детектируются детекторами 5.1 (Д1), …, 5.32 (Д32), оцифровываются в аналого-цифровых преобразователях 6.1 (АЦП1), …, 6.32 (АЦП32) и записываются в блоке памяти реализаций 7 (БПР) независимо друг от друга. Эти колебания записываются в интервале времени, равном времени распространения УЗ колебаний от первого приемо-передающего элемента 2.1 (ППЭ1) антенной решетки 1 (АР) к наиболее дальней визуализируемой точке объекта контроля 15 (ОК) и обратно - к самому удаленному от нее 32-му приемо-передающему элементу антенной решетки 1 (АР).

Далее генератор импульсов 3.2 (ГИ2), соединенный со вторым приемо-передающим элементом 2.2 (ППЭ2) антенной решетки 1 (АР), по сигналу от блока синхронизации 14 (БС) возбуждает второй приемо-передающий элемент 2.1 (ППЭ2) антенной решетки 1 (АР), который посылает в объект контроля 15 (ОК) зондирующий импульс. Снова происходит прием и запись принятых колебаний в блок памяти реализаций 7 (БПР). Но колебания, принятые первым приемо-передающим элементом 2.1 (ППЭ1) антенной решетки 1 (АР), в данном случае не записываются, т.к. реализация этих колебаний согласно принципу взаимности тождественна той, которая уже была принята вторым приемо-передающим элементом 2.2 (ППЭ2) антенной решетки 1 (АР) при посылке зондирующего импульса ее первым приемо-передающим элементом 2.1 (ППЭ1) антенной решетки 1 (АР) в предыдущем цикле зондирования-приема УЗ колебаний.

Затем в третьем цикле зондирования-приема УЗ колебаний все происходит аналогично изложенному выше, только зондирующий импульс в объект контроля 15 (ОК) посылает третий приемо-передающий элемент 2.3 (ППЭ3) антенной решетки 1 (АР), и колебания в блок памяти реализаций 7 (БПР) записываются от 32-х приемо-передающих элементов антенной решетки 1 (АР).

В последнем, 32-м цикле зондирования-приема 32-й приемо-передающий элемент 2.32 (ППЭ32) антенной решетки 1 (АР) исполняет роль излучателя и приемника УЗ колебаний, т.е. работает в совмещенном режиме. При этом в блок памяти реализаций 7 (БПР) записывается всего одна реализация принятых колебаний.

После выполнения всех этих циклов зондирования-приема УЗ колебаний, т.е. после того как все 32 приемо-передающих элемента антенной решетки 1 (АР) совершат по одной посылке зондирующего импульса, в блоке памяти реализаций 7 (БПР) окажутся записанными N=32·(32+1)/2=528 реализаций принятых колебаний.

После записи всех 528 реализаций в блок памяти реализаций 7 (БПР) начинается реконструкция изображения внутренней структуры объекта контроля 15 (ОК) поочередно для каждой визуализируемой точки. Количество визуализируемых точек в нашем примере было 6489600 при следующих размерах объекта контроля: длина - 900 мм, диаметр - 156 мм. Вычислительный блок 8 (ВБ) рассчитывал время распространения ультразвуковой волны до каждой визуализируемой точки в соответствии выражением:

где - координата приемо-передающего элемента антенной решетки 1 (АР), работающего в режиме излучения,

- координата приемо-передающего элемента антенной решетки 1 (АР), работающего в режиме приема;

x, z - координаты визуализируемой точки;

с - скорость распространения УЗ волн в материале объекта контроля 15 (ОК).

Затем в блоке мультипликативной обработки 9 (БМПО) перемножали цифровые коды, выбранные из блока памяти реализаций 7 (БПР) в соответствии со временем распространения от i-го приемо-передающего элемента антенной решетки 1 (АР), работающего в режиме излучения, до j-го приемо-передающего элемента антенной решетки 1 (АР), работающего в режиме приема, через точку визуализации c координатами (x,z) и сохраняли результат перемножения в блоке накопительной памяти 10 (БНП).

Мультипликативная обработка заключается в следующем. На вход блока мультипликативной обработки 9 (БМПО) из вычислительного блока 8 (ВБ) поступает одновременно n выбранных значений А0, …, Аn цифровых кодов (в нашем примере n=32), которые перемножаются попарно в блоках умножения первого уровня 16.1 (БУ1.1), …, 16.n/2 (БУ1.n/2), данные с выходов которых поступают на входы блоков умножения второго уровня 17.1 (БУ2.1), …, 17.n/4 (БУ2.n/4) и перемножаются. Данные с выходов блоков умножения второго уровня 17.1 (БУ2.1), …, 17.n/4 (БУ2.n/4) поступают на вход блоков умножения третьего уровня 18.1 (БУ3.1), …, 18.n/8 (БУ3.n/8) и перемножаются и т.д. Последнее перемножение осуществляется в блоке умножения n/2 уровня 19.1 (БУn/2.1). Блок умножения, например 16.1 (БУ1.1), работает следующим образом. В регистр первого числа 20 записывается первое число. На входы регистров второго числа 21.1, …, 21.n поступает второе число. Причем на вход первого регистра второго числа 21.1 поступает второе число без изменения, на вход второго регистра второго числа 21.2 поступает второе число, сдвинутое на один разряд влево, на вход третьего регистра второго числа 21.3 поступает второе число, сдвинутое на два разряда влево и т.д., на вход n-го регистра второго числа 21.n поступает второе число, сдвинутое на n разрядов влево (таблица 1). Запись данных в регистры второго числа 21.1, …, 21.n производится по единичным данным, записанным в регистр первого числа 20. Если в регистре первого числа 20 в каком-либо разряде будет ноль, то в соответствующий регистр второго числа 21.1, …, 21.n запись второго числа не произойдет. В таблице 1 показан пример сдвига пятиразрядного числа 11011 на входах регистров второго числа 21.1, …, 21.n. В столбце регистра первого числа приведено значение первого числа, в котором единицы имеются только в первом и пятом разрядах, поэтому запись второго числа произошла только в регистры 21.1 и 21.5. В остальных регистрах второго числа 21.2, 21.3, 21.4 записались нули. Пустые клеточки в таблице заполняются нулями.

Затем полученный результат из блока накопительной памяти 10 (БНП) пересылали в вычислительный блок 8 (ВБ), в котором полученному значению (числу) присваивали определенный цвет, который сохраняли в блоке памяти изображений 11 (БПИ). Индикатор 12 (И) отображал результат контроля в виде цветной картинки.

Сравнение результатов визуализации ультразвуковой дефектоскопии колесной оси, полученных с использованием прототипа (фиг. 4 а), и предлагаемого устройства (фиг. 4 б) показывает, что при использовании заявляемого устройства для визуализации ультразвуковой дефектоскопии трехмерного изделия увеличилось отношение сигнал/шум.

Сравнение результатов визуализации ультразвуковой дефектоскопии двух точечных дефектов колесной оси, расположенных на расстоянии 2,4 мм друг от друга, полученных с использованием прототипа (фиг. 5 а), и предлагаемого устройства (фиг. 5 б) показывает, что при использовании прототипа нельзя различить два дефекта раздельно, а предлагаемое устройство позволяет их видеть раздельно, что свидетельствует об увеличении разрешающей способности.

Устройство ультразвуковой томографии, содержащее антенную решетку с n приемно-передающими элементами, каждый из которых соединен с выходом соответствующего генератора импульсов и входом соответствующего усилителя, n аналого-цифровых преобразователей соединены с соответствующими входами блока памяти реализации, количество выходов которого - N определено формулойN=n·(n+1)/2,выходы блока памяти реализации соединены с соответствующими входами вычислительного блока, связанного с индикатором через блок памяти изображений и с блоком накопительной памяти, при этом входы синхронизации каждого генератора импульсов, блока памяти реализаций, вычислительного блока и блока памяти изображений соединены с соответствующими выходами блока синхронизации, отличающееся тем, что блок временной регулировки чувствительности соединен с блоком синхронизации и всеми усилителями, а блок мультипликативной обработки соединен с вычислительным блоком и блоком накопительной памяти, при этом к выходу каждого усилителя подключен детектор, выход которого связан с аналого-цифровым преобразователем.