Двоичный сумматор

Иллюстрации

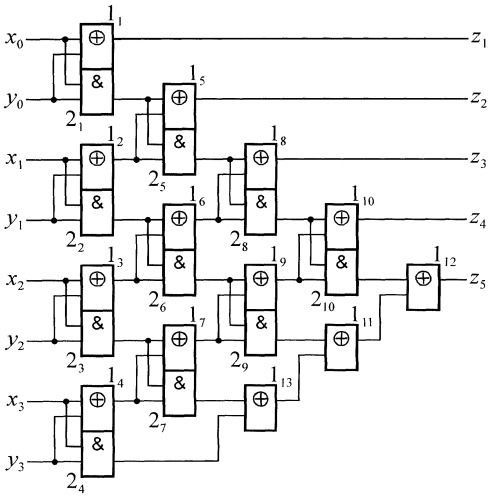

Показать всеИзобретение предназначено для сложения двух четырехразрядных двоичных чисел, задаваемых двоичными сигналами и может быть использовано в системах цифровой вычислительной техники как средство арифметической обработки дискретной информации. Техническим результатом является повышение однородности аппаратурного состава и увеличение быстродействия. Устройство содержит тринадцать элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (11,…,113) и десять элементов И (21,…,210). 1 ил., 1 табл.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны двоичные сумматоры (см., например, рис.6.966 на стр.525 в книге Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для втузов. - СПб.: Политехника, 1996 г.), которые выполняют сложение одноразрядных двоичных чисел, задаваемых двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных двоичных сумматоров, относятся неоднородный аппаратурный состав, образованный логическими элементами трех типов, и ограниченные функциональные возможности, обусловленные тем, что не выполняется сложение четырехразрядных двоичных чисел.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип двоичный сумматор (рис.6.97 на стр.525 в книге Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для втузов. - СПб.: Политехника, 1996 г.), который содержит логические элементы и формирует двоичный код s4s3s2s1s0 суммы S двух четырехразрядных двоичных чисел X=x3x2x1x0, Y=y3y2y1y0, задаваемых двоичными сигналами х0,…,х3, y0,…,у3 ∈ {0,1} так, что х0, y0 и х3, y3 есть младшие и старшие разряды соответственно.

При этом

s 0 = x 0 ⊕ y 0 ⊕ c 0 s 1 = x 1 ⊕ y 1 ⊕ c 1 s 2 = x 2 ⊕ y 2 ⊕ c 2 s 3 = x 3 ⊕ y 3 ⊕ c 3 s 4 = c 4 } ( 1 )

где c0=0;

c r = x r − 1 y r − 1 ∨ ( x r − 1 ⊕ y r − 1 ) c r − 1 , r = r = 1,4 ¯ ( 2 ) .

Здесь символами ⊕, ·, ∨ обозначены операции ИСКЛЮЧАЮЩЕЕ ИЛИ, И, ИЛИ.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся неоднородный аппаратурный состав и низкое быстродействие, обусловленные соответственно тем, что прототип содержит логические элементы трех типов (элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы И, элементы ИЛИ) и максимальное время задержки распространения сигнала в нем равно 9τЛЭ, где τЛЭ есть время задержки логического элемента.

Техническим результатом изобретения является увеличение быстродействия и повышение однородности аппаратурного состава при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в двоичном сумматоре, содержащем восемь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и восемь элементов И, у которых первый и второй входы i-го ( i = 1,8 ¯ ) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым входами i-го элемента И, особенность заключается в том, что в него дополнительно введены пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и два элемента И, причем первый и второй входы j-го ( j = 9,10 ¯ ) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым входами j-го элемента И, первый, второй входы k-го ( k = 5,7 ¯ ) и первый, второй входы m-го ( m = 8,9 ¯ ) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами (k-4)-го элемента И, (k-3)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами (m-3)-го элемента И, (m-2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй входы q-го (g ∈ {10,12}) и первый, второй входы одиннадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами (q-2)-го элемента И, (g-1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами девятого элемента И, тринадцатого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а первый, второй входы тринадцатого и первый, второй входы r-го ( r = 1,4 ¯ ) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами седьмого, четвертого элементов И и r-ым, (4+r)-ым входами двоичного сумматора, первый, второй, третий, четвертый и пятый выходы которого образованы соответственно выходами первого, пятого, восьмого, десятого и двенадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

На чертеже представлена схема предлагаемого двоичного сумматора.

Двоичный сумматор содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11,…,113 и элементы И 21,…,210, причем первый и второй входы элемента 2i ( i = 1,10 ¯ ) соединены соответственно с первым и вторым входами элемента 1k первый, второй входы элемента 1k ( k = 5,7 ¯ ) и первый, второй входы элемента 1m ( m = 8,9 ¯ ) соединены соответственно с выходами элементов 2k-4, 1k-3 и 2m-3, 1m-2, первый, второй входы элемента 1q(q ∈ {10,12}) и первый, второй входы элемента 111 соединены соответственно с выходами элементов 2q-2, 1q-1 и 29, 113, а первый, второй входы элемента 113 и первый, второй входы элемента 1r ( r = 1,4 ¯ ) соединены соответственно с выходами элементов 27, 24 и r-ым, (4+r)-ым входами двоичного сумматора, первый, второй, третий, четвертый и пятый выходы которого образованы соответственно выходами элементов 11 15, 18, 110 и 112.

Работа предлагаемого двоичного сумматора осуществляется следующим образом. На его первый,…,четвертый и пятый,…,восьмой входы подаются соответственно двоичные сигналы х0,…,х3 ∈ {0,1} и y0,…,y3 ∈ {0,1}. Тогда сигналы на выходах предлагаемого сумматора будут определяться выражениями

z1=x0⊕y0;

z2=x1⊕y1⊕x0y0;

z3=x2⊕y2⊕x1y1⊕(x1⊕y1)x0y0;

z4=x3⊕y3⊕x2y2⊕(x2⊕y2)x1y1⊕(x2⊕y2⊕x1y1)((x1⊕y1)x0y0)=

=x3⊕y3⊕x2y2⊕x1x2y1⊕x1y1y2⊕x0x1x2y0⊕

⊕x0x1y0y2⊕x0x2y0y1⊕x0y0y1y2;

z5=x3y3⊕(x3⊕y3)x2y2⊕(x3⊕y3⊕x2y2)((x2⊕y2)x1y1)⊕

⊕(x3⊕y3⊕x2y2⊕(x2⊕y2)x1y1)((x2⊕y2⊕x1y1)((x1⊕y1)x0y0))=

=x3y3⊕x2x3y2⊕x2y2y3⊕x1x2x3y1⊕x1x2y1y3⊕x1x3y1y2⊕

⊕x1y1y2y3⊕x0x1x2x3y0⊕x0x1x3y0y2⊕x0x2x3y0y1⊕

⊕x0x1y0y2y3⊕x0x2y0y1y3⊕x0x3y0y1y2⊕x0y0y1y2y3.

Рассмотрим таблицу

| xr-1 | yr-1 | cr-1 | cr | xr-1yr-1⊕(xr-1⊕yr-1)cr-1 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 |

в которой значения cr вычислены согласно (2). Из анализа таблицы следует, что cr=xr-1yr-1⊕(xr-1⊕yr-1)c-1. Подставляя последнее равенство в выражения (1), получим

s0=x0⊕y0⊕0=x0⊕y0;

s1=x1⊕y1⊕c1=x1⊕y1⊕x0y0;

s2=x2⊕y2⊕c2=x2⊕y2⊕x1y1⊕(x1⊕y1)x0y0;

s3=x3⊕y3⊕c3=x3⊕y3⊕x2y2⊕(x2⊕y2)(x1y1⊕(x1⊕y1)x0y0)=

=x3⊕y3⊕x2y2⊕x1x2y1⊕x1y1y2⊕x0x1x2y0⊕

⊕x0x1y0y2⊕x0x2y0y1⊕x0y0y1y2;

s4=c4=x3y3⊕(x3⊕y3)(x2y2⊕(x2⊕y2)(x1y1⊕(x1⊕y1)x0y0))=

=x3y3⊕x2x3y2⊕x2y2y3⊕x1x2x3y1⊕x1x2y1y3⊕x1x3y1y2⊕

⊕x1y1y2y3⊕x0x1x2x3y0⊕x0x1x2y0y3⊕x0x1x3y0y2⊕x0x2x3y0y1⊕

⊕x0x1y0y2y3⊕x0x2y0y1y3⊕x0x3y0y1y2⊕x0y0y1y2y3.

Сравнив полученные соотношения с выражениями для z1,…,z5, имеем z1=s0, z2=s1, z3=s2, z4=s3, z5=s4. Таким образом, на выходах предлагаемого сумматора получим пятиразрядное двоичное число S=s4s3s2s1s0=X+Y, где Х=х3х2х1х0, Y=y3y2y1y0 - четырехразрядные двоичные числа, задаваемые входными двоичными сигналами х0,…,х3, y0,…,y3 так, что х0, y0 и х3, y3 есть младшие и старшие разряды соответственно.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый двоичный сумматор формирует двоичный код суммы двух четырехразрядных двоичных чисел, задаваемых двоичными сигналами, и имеет более однородный по сравнению с прототипом аппаратурный состав и более высокое быстродействие, поскольку содержит логические элементы двух типов (элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы И) и максимальное время задержки распространения сигнала в нем равно 5 тτЛЭ, где τЛЭ есть время задержки логического элемента.

Двоичный сумматор, содержащий восемь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и восемь элементов И, у которых первый и второй входы i-го ( i = 1,8 ¯ ) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым входами i-го элемента И, отличающийся тем, что в него дополнительно введены пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и два элемента И, причем первый и второй входы j-го ( j = 9,10 ¯ ) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым входами j-го элемента И, первый, второй входы k-го ( k = 5,7 ¯ ) и первый, второй входы m-го ( m = 8,9 ¯ ) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами (k-4)-го элемента И, (k-3)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами (m-3)-го элемента И, (m-2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй входы q-го (q ∈ {10,12}) и первый, второй входы одиннадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами (q-2)-го элемента И, (q-1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами девятого элемента И, тринадцатого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а первый, второй входы тринадцатого и первый, второй входы r-го ( r = 1,4 ¯ ) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами седьмого, четвертого элементов И и r-м, (4+r)-м входами двоичного сумматора, первый, второй, третий, четвертый и пятый выходы которого образованы соответственно выходами первого, пятого, восьмого, десятого и двенадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.