Вычислительная система

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано при построении многомашинных, многопроцессорных вычислительных систем (ВС) высокой производительности и надежности. Технический результат заключается в обеспечении возможности управления работой нескольких ЭВМ системы при возникновении различных нештатных ситуаций за счет перераспределения ресурсов системы. Вычислительная система содержит пять электронных вычислительных машин (ЭВМ), три канала ввода-вывода, три внешних абонента и устройство управления, причем соответствующие входы-выходы ЭВМ соединены шинами с соответствующими входами-выходами устройства управления, блок основной общей памяти (ОД) и блок резервной ОП, соответствующие входы-выходы которых соединены шинами с соответствующими входами-выходами устройства управления, первые три ЭВМ используются как универсальные, четвертая ЭВМ используется в качестве управляющей, а пятая ЭВМ является резервной, входы-выходы каждого соответствующего абонента соединены шинами входами-выходами соответствующего канала ввода-вывода, входы-выходы которых соединены шинами с соответствующими входами-выходами устройства управления. 7 з.п. ф-лы, 2 табл., 9 ил.

Реферат

Изобретение модель относится к вычислительной технике и может быть использовано при построении многомашинных, многопроцессорных вычислительных систем (ВС) высокой производительности и надежности.

Известна резервированная двухпроцессорная вычислительная система [РФ №2264648 C1, G06F 11/20, 27.05.2005 г.], содержащая два идентичных канала, в каждом из которых первый выход процессора подключен к первому входу коммутатора, системный генератор, выход которого подключен к первому входу процессора первого канала, схему начальной установки, выход которой подключен ко второму входу процессора первого канала, импульсный генератор, элемент ИЛИ, временной анализатор исправности, счетчик сбоев, триггер, элемент ИЛИ-НЕ, выход которого подключен ко второму входу коммутатора, второй выход процессора через элемент ИЛИ подключен к первому входу триггера и ко второму входу временного анализатора исправности, выход триггера подключен к первому входу элемента ИЛИ-НЕ, второй вход процессора соединен со вторым входом элемента ИЛИ и вторым входом счетчика сбоев, выход импульсного генератора через временной анализатор исправности подключен к первому входу счетчика сбоев и ко второму входу триггера, второй выход счетчика сбоев подключен ко второму входу элемента ИЛИ-НЕ, а также введены системный генератор, выход которого подключен к первому входу процессора второго канала, схема начальной установки, выход которой подключен ко второму входу процессора второго канала, и схема сравнения, первый вход которой подключен к первому выходу счетчика сбоев первого канала, второй вход схемы сравнения подключен к первому выходу счетчика сбоев второго канала, первый выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ первого канала, второй выход схемы сравнения подключен к третьему входу элемента ИЛИ-НЕ второго канала, выходы коммутаторов соединены и являются выходом системы.

Недостатком известной системы является то, что она может использоваться только при построении надежных вычислительно систем за счет резервирования каналов.

Наиболее близкой к заявляемой является вычислительная система [АС №873804 А1, G06F 15/16, 15.06.19941, содержащая N цифровых вычислительных машин (ЦВМ), N каналов ввода-вывода, N блоков электропитания, N групп устройств сопряжения, N*M внешних абонентов (М - число внешних абонентов в группе) и блок управления, причем первый вход-выход ЦВМ соединен с соответствующим входом-выходом блока управления, второй вход-выход ЦВМ соединен с первым входом-выходом соответствующего канала ввода-вывода, первый выход ЦВМ соединен с входом соответствующего блока электропитания, второй вход-выход канала ввода-вывода соединен с первым входом-выходом устройств сопряжения соответствующей группы, второй вход-выход устройства сопряжения соединен с входами-выходами внешних абонентов соответствующей группы, отличающаяся тем, что с целью повышения быстродействия она содержит N адаптеров, N блоков приоритета и N коммутаторов, причем один вход-выход адаптера соединен со вторым входом-выходом соответствующего канала ввода-вывода, другие входы-выходы одного адаптера соединены с соответствующими входами-выходами других адаптеров, запускающий вход блока приоритета соединен с выходом соответствующего канала ввода-вывода, запросные входы блока приоритета соединены с выходами устройств сопряжения соответствующей группы, выходы блока приоритета соединены с первыми входами устройств сопряжения соответствующей группы, вторые входы которых соединены с выходами соответствующего коммутатора, выход блока электропитания и второй выход ЦВМ соединены с входами соответствующего коммутатора, а каждый вход-выход группы входов-выходов блока управления соединен со вторым входом-выходом соответствующего устройства сопряжения.

Недостатком данной системы являются отсутствие возможности управления работой нескольких ЭВМ системы при возникновении различных нештатных ситуаций за счет перераспределения ресурсов системы.

Техническим результатом является обеспечение возможности управления работой нескольких ЭВМ системы при возникновении различных нештатных ситуаций за счет перераспределения ресурсов системы.

Технический результат достигается тем, что в вычислительную систему, содержащую пять электронных вычислительных машин (ЭВМ), три канала ввода-вывода, три внешних абонента и устройство управления, причем соответствующие входы входы-выходы ЭВМ соединены шинами с соответствующими входами-выходами устройства управления, дополнительно введены блок основной общей памяти (ОП) и блок резервной ОП, соответствующие входы-выходы которых соединены шинами с соответствующими входами-выходами устройства управления, первые три ЭВМ используются как универсальные, четвертая ЭВМ используется в качестве управляющей, а пятая ЭВМ является резервной, входы-выходы каждого соответствующего абонента соединены шинами входами-выходами соответствующего канала ввода-вывода, входы-выходы которых соединены шинами с соответствующими входами-выходами устройства управления, причем устройство управления содержит два блока элементов ИЛИ, блок элементов ИЛИ, состоящий из N элементов ИЛИ, где N равно количеству разрядов передаваемой информации, блок управления системой при записи и считывания контрольной точки универсальных ЭВМ, блок управления системой при возникновении неисправности одной из универсальных ЭВМ, блок связи всех ЭВМ системы с внешними абонентами, блок управления системой при возникновении неисправности ЗУ универсальных ЭВМ, блок управления системой при возникновении неисправности в ОП и четыре элемента ИЛИ, с первого по тридцать третий входы устройства соединены соответственно с первого по тридцать третий входы первого блока элементов ИЛИ, с тридцать четвертого по шестьдесят восьмой входы устройства соединены соответственно с первого по тридцать пятый входы второго блока элементов ИЛИ, с первого по четвертый выходы первого блока элементов ИЛИ соединены соответственно с первого по четвертый входами блока управления системой при записи и считывания контрольной точки универсальных ЭВМ, пятый вход которого соединен с выходом блока элементов ИЛИ, второй вход блока управления системой при записи и считывания контрольной точки универсальных ЭВМ соединен с объединенными первыми входами, блока управления системой при возникновении неисправности одной из универсальных ЭВМ, блока управления системой при возникновении неисправности ЗУ универсальных ЭВМ и четвертым входом блока связи всех ЭВМ системы с внешними абонентами, с пятого по двенадцатый входы первого блока элементов ИЛИ соединены соответственно с шестого по тринадцатый входами блока управления системой при записи и считывания контрольной точки универсальных ЭВМ, с тринадцатого по пятнадцатый входы первого блока элементов ИЛИ соединены соответственно с третьего по пятый блока управления системой при возникновении неисправности одной из универсальных ЭВМ, с первого по пятый входы второго блока элементов ИЛИ соединены соответственно с десятого по четырнадцатый блока управления системой при возникновении неисправности одной из универсальных ЭВМ, второй вход которого соединен с третьим входом блока связи всех ЭВМ системы с внешними абонентами и седьмым выходом второго блока элементов ИЛИ, шестой выход которого соединен со вторым входом блока связи всех ЭВМ системы с внешними абонентами, первый вход которого соединен с третьим входом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, четвертый вход которого соединен с шестым входом блока связи всех ЭВМ системы с внешними абонентами, пятый вход которого соединен с восьмым выходом второго блока элементов ИЛИ, с девятого по четырнадцатый выходы которого соединены соответственно с седьмого по двенадцатый входами блока связи всех ЭВМ системы с внешними абонентами, с тринадцатого по пятнадцатый входы которого соединены соответственно каждый с объединенными с первого по третий входами блока элементов ИЛИ, с пятого по седьмой входами блока управления системой при возникновении неисправности ЗУ универсальных ЭВМ, с четвертого по шестой входами блока управления системой при возникновении неисправности в ОП и с двадцать первого по двадцать третий выходами второго блока элементов ИЛИ, пятнадцатый и шестнадцатый выходы которого соединены каждый соответственно с третьим и четвертым входами блока управления системой при возникновении неисправности ЗУ универсальных ЭВМ, восьмой вход которого соединен с шестым входом блока управления системой при записи и считывания контрольной точки универсальных ЭВМ, восьмой вход которого соединен с пятнадцатым входом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, восьмой вход которого соединен с седьмым входом блока управления системой при записи и считывания контрольной точки универсальных ЭВМ, одиннадцатый вход которого соединен с седьмым входом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, девятый вход которого соединен с тринадцатым входом блока управления системой при записи и считывания контрольной точки универсальных ЭВМ, двенадцатый вход которого соединен с шестым входом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, пятый вход которого соединен со вторым входом блока управления системой при возникновении неисправности ЗУ универсальных ЭВМ, девятый вход которого соединен с семнадцатым выходом второго блока элементов ИЛИ, с восемнадцатого по двадцатый выходы которого соединены соответственно с первого по третий входами блока управления системой при возникновении неисправности в ОП, седьмой и восьмой входы которого соединены соответственно с девятнадцать четвертым и двадцать пятым выходами второго блока элементов ИЛИ, с первого по десятый выходы блока управления системой при возникновении неисправности ЗУ универсальных ЭВМ соединены соответственно с двадцать девятого по тридцать восьмой выходами устройства, с тридцать девятого по сорок пятый выходы которого соединены соответственно с первого по седьмой выходами блока управления системой при возникновении неисправности в ОП, с третьего по восьмой выходы блока управления системой при записи и считывания контрольной точки универсальных ЭВМ соединены соответственно со второго по седьмой выходами устройства, первый выход которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен одиннадцатым выходом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, первый выход которого соединен со вторым входом второго элемента ИЛИ, первый вход которого соединен со вторым выходом блока управления системой при записи и считывания контрольной точки универсальных ЭВМ, первый выход которого соединен с первым входом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с восьмым выходом устройства, девятый выход которого соединен со вторым выходом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, с шестого по десятый выходы которого соединены соответственно с одиннадцатого по пятнадцатый выходами устройства, десятый выход которого соединен с четвертым выходом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, третий выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с первым выходом блока связи всех ЭВМ системы с внешними абонентами, а выход соединен с семнадцатым выходом устройства, шестнадцатый выход которого соединен с двенадцатым выходом блока управления системой при возникновении неисправности одной из универсальных ЭВМ, пятый выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с восьмым выходом блока связи всех ЭВМ системы с внешними абонентами, а выход соединен с двадцать восьмым выходом устройства, с восемнадцатого по двадцать третий выходы которого соединены соответственно со второго по седьмой выходами блока связи всех ЭВМ системы с внешними абонентами, с девятого по двенадцатый выходы которого соединены соответственно с двадцать четвертого по двадцать седьмой выходами устройства, причем первый блок элементов ИЛИ содержит девять элементов ИЛИ, с первого по третий входы блока соединены соответственно с первого по третий входами первого элемента ИЛИ, выход которого соединен с первым выходом блока, второй выход которого соединен с четвертым входом блока, с пятого по седьмой входы которого соединены с первого по третий входами второго элемента ИЛИ, выход которого соединен с третьим выходом блока, с восьмого по десятый входы которого соединены с первого по третий входами третьего элемента ИЛИ, выход которого соединен с четвертым выходом блока, с одиннадцатого по тринадцатый входы которого соединены с первого по третий входами четвертого элемента ИЛИ, выход которого соединен с пятым выходом блока, четырнадцатый и пятнадцатый входы которого соединены соответственно с его шестым и седьмым выходами, с шестнадцатого по восемнадцатый входы которого соединены с первого по третий входами пятого элемента ИЛИ, выход которого соединен с восьмым выходом блока, с девятнадцатого по двадцать первый входы которого соединены с первого по третий входами шестого элемента ИЛИ, выход которого соединен с девятым выходом блока, двадцать второй, двадцать третий и двадцать четвертый входы которого соединены соответственно с десятым, одиннадцатым и двенадцатым выходами блока, с двадцать пятого по двадцать седьмой входы которого соединены с первого по третий входами седьмого элемента ИЛИ, выход которого соединен с тринадцатым выходом блока, с двадцать восьмого по тридцатый входы которого соединены с первого по третий входами восьмого элемента ИЛИ, выход которого соединен с четырнадцатым выходом блока, с тридцать первого по тридцать третий входы которого соединены с первого по третий входами девятого элемента ИЛИ, выход которого соединен с пятнадцатым выходом блока, причем второй блок элементов ИЛИ содержит пять элементов ИЛИ с первого по пятый входы блока соединены соответственно каждый с первого по пятый его выходами, с шестого по восьмой входы которого соединены с первого по третий входами первого элемента ИЛИ, выход которого соединен с шестым выходом блока, девятый вход которого соединен с седьмым выходом блока, с десятого по двенадцатый входы которого соединены с первого по третий входами второго элемента ИЛИ, выход которого соединен с восьмым выходом блока, с тринадцатого по пятнадцатый входы которого соединены с первого по третий входами третьего элемента ИЛИ, выход которого соединен с девятым выходом блока, с шестнадцатого по двадцатый входы блока соединены соответственно каждый с десятого по четырнадцатый его выходами, с двадцать первого по двадцать третий входы которого соединены с первого по третий входами четвертого элемента ИЛИ, выход которого соединен с пятнадцатым выходом блока, с двадцать четвертого по двадцать шестой входы которого соединены с первого по третий входами пятого элемента ИЛИ, выход которого соединен с шестнадцатым выходом блока, с двадцать седьмого по тридцать пятый входы блока соединены соответственно каждый с семнадцатого по двадцать пятый его выходами, причем блок управления системой при записи и считывания контрольной точки универсальных ЭВМ содержит дешифратор, формирователь адреса, триггер, четыре блока элементов И, состоящих из N элементов И каждый, два буферных запоминающих блока и три блока элементов И, состоящих из N элементов И каждый, выходы которых соединены соответственно с шестым, седьмым и восьмым выходами блока, первый вход которого соединен с его первым выходом, второй вход блока соединен с входом дешифратора, первый, второй и третий выходы которого соединены с первыми входами соответственно первого второго и третьего блоков элементов И и соответственно с первым, вторым и третьем входами формирователя адреса, выход которого соединен со вторым выходом блока, третий выход которого соединен с нулевым входом триггера и четвертым входом блока, третий вход которого соединен с единичным входом триггера, единичный выход которого соединен с первым входом первого блока элементов И, второй вход которого соединен с пятым входом блока, шестой вход которого соединен с первым входом четвертого блока элементов И и с третьим входом первого блока элементов И, выход которого соединен с входом первого буферного запоминающего блока, выход которого соединен с первым входом второго блока элементов И, выход которого соединен с четвертым выходом блока, седьмой вход которого соединен с первым входом третьего блока элементов И и вторым входом второго блока элементов И, третий вход которого соединен с восьмым входом блока, девятый вход которого соединен с его пятым выходом, десятый вход блока соединен со вторым входом четвертого блока элементов И, третий вход которого соединен с выходом второго буферного запоминающего блока, вход которого соединен с выходом третьего блока элементов И, второй и третий входы которого соединены соответственно с одиннадцатым и двенадцатым входами блока, тринадцатый вход которого соединен с четвертым входом четвертого блока элементов И, выход которого соединен с объединенными вторыми входами первого второго и третьего блоков элементов И, причем блок управления системой при возникновении неисправности одной из универсальных ЭВМ содержит дешифратор, формирователь адреса, триггер, три блока элементов И, состоящих из N элементов И, четыре блока элементов И, состоящих из N элементов И каждый, блок элементов ИЛИ, состоящий из N элементов, буферный запоминающий блок и элемент И, выход которого соединен с четвертым выходом блока, первый вход которого соединен с входом дешифратора, первый, второй и третий выходы которого соединены с первыми входами соответственно первого второго и третьего блоков элементов И и соответственно с первым, вторым и третьем входами формирователя адреса, выход которого соединен с первым выходом блока, второй вход которого соединен с объединенными первыми входами первого и второго блоков элементов И, первым входом элемента И и вторым выходом блока, третий вход которого соединен с его третьим выходом, вторым входом элемента И и единичным входом триггера, единичный выход которого соединен с объединенными вторыми входами первого, второго, третьего и четвертого блоков элементов И, а нулевой вход триггера соединен с четвертым входом блока и объединенными его пятым и шестым выходами, пятый вход блока соединен с объединенными вторыми входами первого, второго и третьего блоков элементов И, выходы которых соединены соответственно с седьмым, восьмым и девятым выходами блока, шестой и седьмой входы которого соединены соответственно с третьим и четвертым входами третьего блока элементов И, пятый вход которого соединен с четвертым входом четвертого блока элементов И и восьмым входом блока, девятый и десятый входы которого соединены соответственно с четвертым и пятым входами второго блока элементов И, шестой вход которого соединен с четвертым входом третьего блока элементов И и одиннадцатым входом блока, двенадцатый вход которого соединен с его одиннадцатым выходом, тринадцатый и четырнадцатый входы блока соединены соответственно с первым и третьим входами третьего блока элементов И, выход которого соединен со вторым входом блока элементов ИЛИ, первый вход которого соединен с выходом первого блока элементов И, а выход соединен с входом буферного запоминающего блока, выход которого соединен с объединенными третьим входом второго блока элементов И и первым входом четвертого блока элементов И, третий вход которого соединен с пятнадцатым входом блока, а выход соединен с двенадцатым выходом блока, десятый выход которого соединен с выходом второго блока элементов И, причем блок связи всех ЭВМ системы с внешними абонентами содержит два дешифратора, триггер, пять элементов ИЛИ, элемент НЕ, шестнадцать блоков элементов И, состоящих из N элементов И каждый, и пять блоков элементов ИЛИ, состоящих из N элементов И каждый, первый и второй входы блока соединены соответственно с его первым и вторым выходами и первым и вторым входами первого элемента ИЛИ, выход которого соединен с единичным входом триггера, единичный выход которого соединен с объединенными вторыми входами второго, третьего, десятого и одиннадцатого блоков элементов И, а нулевой выход триггера соединен с объединенными первыми входами седьмого И, восьмого И, девятого И, четырнадцатого И, пятнадцатого И и шестнадцатого И блоков элементов И, третий вход блока соединен с объединенными первым входом второго И, третьим входом десятого И блоков элементов И и входом элемента НЕ, выход которого соединен с объединенными первым входом третьего И, третьим входом одиннадцатого И блоков элементов И, четвертый вход блока соединен с входом первого дешифратора, первый, второй и третий выходы которого соединены с первыми входами соответственно второго, третьего и четвертого элементов ИЛИ, вторые входы которых соединены с соответственно с первым, вторым и третьим выходами второго дешифратора, вход которого соединен с пятым входом блока, шестой и седьмой входы которого соединены соответственно с его восьмым и девятым выходами и соответственно с первым и вторым входами пятого элемента ИЛИ, выход которого соединен с нулевым входом триггера, восьмой, девятый и десятый входы блока соединены со вторыми входами соответственно первого, второго и третьего блоков элементов И, выходы которых соединены с соответствующими входами первого блока элементов ИЛИ, выход которого соединен с объединенными третьими входами второго и третьего блоков элементов И, выходы которых соединены соответственно с третьим и четвертым выходами блока, одиннадцатый и двенадцатый входы которого соединены с первыми входами соответственно десятого и одиннадцатого блоков элементов И, выходы которых соединены соответственно с первым и вторым входами второго блока элементов ИЛИ, выход которого соединен с объединенными вторыми входами четвертого, пятого и шестого блоков элементов И, выходы которых соединены с первыми входами соответственно третьего, четвертого и пятого блоков элементов ИЛИ, вторые входы которых соединены с выходами соответственно седьмого, восьмого и девятого блоков элементов И, вторые входы которых соединены соответственно с тринадцатым, четырнадцатым и пятнадцатым входами блока, десятый одиннадцатый и двенадцатый выходы которого соединены с выходами соответственно третьего, четвертого и пятого блоков элементов ИЛИ, пятый, шестой и седьмой выходы блока соединены с выходами соответственно четырнадцатого И, пятнадцатого И и шестнадцатого И блоков элементов И, вторые входы которых соединены со вторыми входами соответственно первого, второго и третьего блоков элементов И, первые входы которых соединены с выходами соответственно второго, третьего и четвертого элемента ИЛИ, причем блок управления системой при возникновении неисправности ЗУ универсальных ЭВМ содержит дешифратор, формирователь адреса, триггер, три элемента И, восемь блоков элементов И, состоящих из N элементов И каждый, и блок элементов ИЛИ, выход которого соединен со вторым входом четвертого блока элементов И, выход которого соединен с седьмым выходом блока, первый вход которого соединен с входом дешифратора, первый выход которого соединен с объединенными первыми входами первого элемента И, первого и шестого блоков элементов И и формирователя адреса, второй вход которого соединен с объединенными первыми входами второго элемента И, второго и седьмого блоков элементов И и вторым выходом дешифратора, третий выход которого соединен с объединенными первыми входами третьего элемента И, третьего и восьмого блоков элементов И и третьим входом формирователя адреса, выход которого соединен с первым выходом блока, второй, третий и четвертый выходы которого соединены с выходами соответственно первого, второго и третьего элементов И, вторые входы которых объединены и соединены со вторым входом блока, третий вход которого соединен с его пятым выходом и единичным входом триггера, единичный выход которого соединен с объединенными первыми входами четвертого и пятого элементов И, а нулевой вход триггера соединен с объединенными четвертым входом и шестым выходом блока, пятый, шестой и седьмой входы которого соединены со вторыми входами соответственно первого, второго и третьего блоков элементов И, выходы которых соединены соответственно с первым, вторым, и третьим входами элемента ИЛИ, восьмой вход блока соединен с объединенными третьими входами четвертого и пятого элементов И, девятый вход блока соединен со вторым входом пятого элемента И, выход которого соединен с объединенными вторыми входами шестого, седьмого и восьмого блоков элементов И, выходы которых соединены соответственно с восьмым, девятым и десятым выходами блока, причем блок управления системой при возникновении неисправности в ОП содержит дешифратор, триггер, десять блоков элементов И, состоящих из N элементов И каждый, и два блока элементов ИЛИ, состоящие из N элементов ИЛИ, первый вход блока соединен с его первым выходом и единичным входом триггера, нулевой вход которого соединен со вторым входом блока и его вторым выходом, третий вход блока соединен с входом дешифратора, первый выход которого соединен с объединенными первыми входами первого и шестого блоков элементов И, второй выход дешифратора соединен с объединенными первыми входами второго и седьмого блоков элементов И, третий выход дешифратора соединен с объединенными первыми входами третьего и восьмого блоков элементов И, четвертый, пятый и шестой входы блока соединены со вторыми входами соответственно первого, второго и третьего блоков элементов И, выходы которых соединены соответственно с первым, вторым и третьим входами первого блока элементов ИЛИ, выход которого соединен с объединенными вторыми входами четвертого и пятого блоков элементов И, выходы которых соединены соответственно с третьим и четвертым выходами блока, пятый, шестой и седьмой выходы которого соединены с выходами соответственно шестого, седьмого и восьмого блоков элементов И, вторые входы которых объединены и соединены с выходом второго блока элементов ИЛИ, первый и второй входы которого соединены с выходами соответственно девятого и десятого блоков элементов И, вторые входы которых соединены соответственно с седьмым и восьмым входами блока, единичный выход триггера соединен с объединенными первыми входами четвертого и девятого блоков элементов И, а нулевой выход триггера соединен с объединенными первыми входами пятого и десятого блоков элементов И.

Введение указанных дополнительных элементов и последовательности их подключения позволяют обеспечить возможность управления работой нескольких ЭВМ системы при возникновении различных нештатных ситуаций за счет перераспределения ресурсов системы.

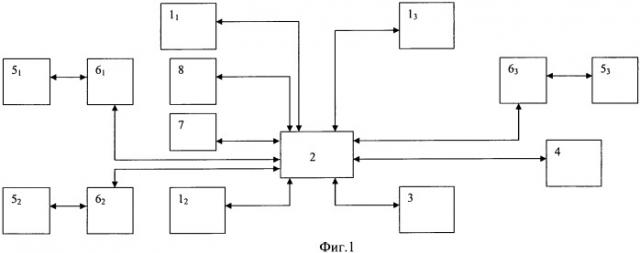

На фиг.1 - представлена функциональная схема вычислительной системы.

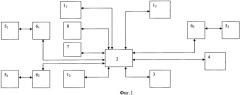

На фиг.2 - представлена функциональная схема устройства управления.

На фиг.3 - представлена функциональная схема первого блока элементов ИЛИ.

На фиг.4 - представлена функциональная схема второго блока элементов ИЛИ.

На фиг.5 - представлена функциональная схема блока управления системой при записи и считывания контрольной точки универсальных ЭВМ.

На фиг.6 - представлена функциональная схема блока управления системой при возникновении неисправности универсальных ЭВМ.

На фиг.7 - представлена функциональная схема блока связи всех ЭВМ системы с внешними абонентами.

На фиг.8 - представлена функциональная схема блока управления системой при возникновении неисправности запоминающих устройств (ЗУ) универсальных ЭВМ.

На фиг.9 - представлена функциональная схема блока управления системой при возникновении неисправности в общей памяти (ОП).

Система (фиг.1) содержит три 11-13 универсальных ЭВМ, устройство управления системой 2, универсальную резервную ЭВМ 3, управляющую ЭВМ 4, три внешних абонента 51-53, три устройства ввода-вывода 61-63, блок 7 основной ОП и блок 8 резервной ОП.

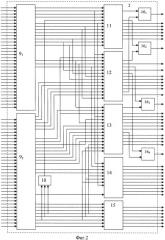

Устройство управления 2 (фиг.2) содержит два блока элементов ИЛИ 91-92, блок 10, состоящий из N элементов ИЛИ, где N равно количеству разрядов передаваемой информации, блок 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, блок 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, блок 13 связи всех ЭВМ системы с внешними абонентами, блок 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ, блок 15 управления системой при возникновении неисправности в ОП и четыре элемента ИЛИ 161-164.

Первый блок элементов ИЛИ 91 (фиг.3) содержит девять элементов ИЛИ 171-179.

Второй блок элементов ИЛИ 92 (фиг.4) содержит пять элементов ИЛИ 181-185.

Блок управления системой при записи и считывания контрольной точки универсальных ЭВМ 11 (фиг.5) содержит дешифратор 19, формирователь адреса 20, триггер 21, четыре блока элементов И 221-224, состоящих из N элементов И каждый, два буферных запоминающих блока 231-232 и три блока элементов И 241-243, состоящих из N элементов И каждый.

Блок управления системой при возникновении неисправности одной из универсальных ЭВМ 12 (фиг.6) содержит дешифратор 25, формирователь адреса 26, триггер 27, три блока элементов И 281-283, состоящих из N элементов И, четыре блока элементов И 291-294, состоящих из N элементов И каждый, блок элементов ИЛИ 30, состоящий из N элементов, буферный запоминающий блок 31 и элемент И 32.

Блок связи всех ЭВМ системы с внешними абонентами 13 (фиг.7) содержит два дешифратора 331-355, триггер 34, пять элементов ИЛИ 351-355, элемент НЕ 36, шестнадцать блоков элементов И 371-3716, состоящих из N элементов И каждый, и пять блоков элементов ИЛИ 381-385, состоящих из N элементов И каждый.

Блок управления системой при возникновении неисправности ЗУ универсальных ЭВМ 14 (фиг.8) содержит дешифратор 39, формирователь адреса 40, триггер 41, три элемента И 421-423, восемь блоков элементов И 431-438, состоящих из N элементов И каждый, и блок элементов ИЛИ 44.

Блок управления системой при возникновении неисправности в ОП 15 (фиг.9) содержит дешифратор 45, триггер 46, десять блоков элементов И 471-4710, состоящих из N элементов И каждый, и два блока элементов ИЛИ 481-482, состоящие из N элементов ИЛИ.

Система (фиг.1 - Фиг.9) содержит пять электронных вычислительных машин (ЭВМ) 1, 3 и 4, три канала ввода-вывода 6, три внешних абонента 5 и устройство управления 2, причем соответствующие входы входы-выходы ЭВМ соединены шинами с соответствующими входами-выходами устройства управления, блок 7 основной общей памяти (ОП) и блок 8 резервной ОП, соответствующие входы-выходы которых соединены шинами с соответствующими входами-выходами устройства управления, первые три ЭВМ используются как универсальные 11-13, четвертая ЭВМ используется в качестве управляющей 4, а пятая ЭВМ 5 является резервной, входы-выходы каждого соответствующего абонента соединены шинами входами-выходами соответствующего канала ввода-вывода, входы-выходы которых соединены шинами с соответствующими входами-выходами устройства управления 2, причем устройство управления 2 содержит два блока элементов ИЛИ 91-92, блок 10 элементов ИЛИ, состоящий из N элементов ИЛИ, где N равно количеству разрядов передаваемой информации, блок 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, блок 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, блок 13 связи всех ЭВМ системы с внешними абонентами, блок 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ, блок 15 управления системой при возникновении неисправности в ОП и четыре элемента ИЛИ 161-164, с первого по тридцать третий входы устройства соединены соответственно с первого по тридцать третий входы первого блока элементов ИЛИ 91, с тридцать четвертого по шестьдесят восьмой входы устройства соединены соответственно с первого по тридцать пятый входы второго блока элементов ИЛИ 92, с первого по четвертый выходы первого блока элементов ИЛИ 91 соединены соответственно с первого по четвертый входами блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, пятый вход которого соединен с выходом блока 10 элементов ИЛИ, второй вход блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ соединен с объединенными первыми входами, блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, блока 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ и четвертым входом блока 13 связи всех ЭВМ системы с внешними абонентами, с пятого по двенадцатый входы первого блока элементов ИЛИ 91 соединены соответственно с шестого по тринадцатый входами блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, с тринадцатого по пятнадцатый входы первого блока элементов ИЛИ 91 соединены соответственно с третьего по пятый блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, с первого по пятый входы второго блока элементов ИЛИ 92 соединены соответственно с десятого по четырнадцатый блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, второй вход которого соединен с третьим входом блока 13 связи всех ЭВМ системы с внешними абонентами и седьмым выходом второго блока элементов ИЛИ 92, шестой выход которого соединен со вторым входом блока 13 связи всех ЭВМ системы с внешними абонентами, первый вход которого соединен с третьим входом блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, четвертый вход которого соединен с шестым входом блока 13 связи всех ЭВМ системы с внешними абонентами, пятый вход которого соединен с восьмым выходом второго блока элементов ИЛИ 92, с девятого по четырнадцатый выходы которого соединены соответственно с седьмого по двенадцатый входами блока 13 связи всех ЭВМ системы с внешними абонентами, с тринадцатого по пятнадцатый входы которого соединены соответственно каждый с объединенными с первого по третий входами блока 10 элементов ИЛИ, с пятого по седьмой входами блока 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ, с четвертого по шестой входами блока 15 управления системой при возникновении неисправности в ОП и с двадцать первого по двадцать третий выходами второго блока элементов ИЛИ 92, пятнадцатый и шестнадцатый выходы которого соединены каждый соответственно с третьим и четвертым входами блока 14 управления системой при возникновении неисправности ЗУ универсальных ЭВМ, восьмой вход которого соединен с шестым входом блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, восьмой вход которого соединен с пятнадцатым входом блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, восьмой вход которого соединен с седьмым входом блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, одиннадцатый вход которого соединен с седьмым входом блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, девятый вход которого соединен с тринадцатым входом блока 11 управления системой при записи и считывания контрольной точки универсальных ЭВМ, двенадцатый вход которого соединен с шестым входом блока 12 управления системой при возникновении неисправности одной из универсальных ЭВМ, пятый вход которого соединен со вторым входом блока 14 управления системой при возникновении