Табличное суммирующе-множительное устройство

Иллюстрации

Показать всеРеферат

253442

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сотое Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 11.1.1968 (№ 1209247/18-24) Кл. 42птз, 7/50

42тпз, 7152 с присоединением заявки №

Приоритет

Опубликовано 30.1Х.1969. Бюллетень № 30

Дата опубликования описания 25.II.1970

МПК G 06f

G 06(УДК 681.325.54:681.325..575 (088.8) Комитет по девам изобретений и открытий при Совете Министров

СССР

Авторы изобретения А. П. Кондратьев, Р. М. Асцатуров, Н. А. Мальцев и Ю. В. Тихович

Заявитель

ТАБЛИЧНОЕ т".УММИРУ1ОЩЕ-МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к области цифровой вычислительной техники и может быть применено в электронных цифровых вычислительных машинах с двоично-десятичным представлением чисел (код 8 — 4 — 2 — 1) и последовательной (посимвольной) обработкой информации, .

Известны табличные сум миру юще-мно;кительные устройства, содержащие запоминающее устройство, схему формирования адресов таблиц, регистры первого и второго операндов и устройство управления.

В известных устройствах запоминающее устройство, предназначенное для хранения таблиц, имеет значительный объем.

Предлагаемое устройство отличается тем, что оно содержит блок выдачи результата и блок анализа, входы которого подключены к выходам регистров первого и второго операндов, выходы блока анализа операндов подсоединены через схемы «И» ко входам первой и второй схем «ИЛИ» блока выдачи результата, выход первой схемы «ИЛИ» блока выдачи результата соединен со входом схемы опроса регистра второго операнда, выход которой подключен к триггерам регистра второго сперанда, выход второй схемы «ИЛИ» блока выдачи результата соединен со входом схемы опроса регистра первого операнда, выход которой подключен к триггерам регистра перmoro опер аида.

Это позволяет упростить устройство и сократить время выполнения операций.

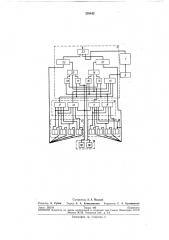

На чертеже изображена схема предлагае того устройства.

Оно содержит запоминающее устройство 1, схему 2 формирования адресов таблиц, блок

8 выдачи результата, блок 4 анализа операндов, регистр 5 первого операнда, регисгр б второго операнда и устройство 7 управления.

10 Нулевые выходы триггеров первого, второго, третьего и четвертого разрядов регистра 5 первого операнда соединены со входами схемы «И» 8, а эти же выходы регистра б второго операнда — со входами схемы «И» 9 блока

15 анализа операндов.

Нулевые выходы триггеров второго, третьего, четвертого разрядов, единичный выход триггера первого разряда регистра 5 первого операнда и выход источника 10 сигнала

20 «умножение» устройства управления соединены со входами схемы «И» 11, а эти же выходы регистра б второго операнда и источника

10 сигнала «умножение» вЂ” со входами схемы

«И» 12 блока анализа операндов.

Выходы схем «И» 8, 9, 11, 12 блока анализа операндов соединены со входами первой схемы «ИЛИ» 18 блока выдачи результата, выход которой соединен с запрещающим входом

ЗО схемы 2 формирования адресов таблиц, 253442

Выход схемы «И» 9 блока анализа операндов и выход источника 14 сигнала «сложение» устройства управления. соединены со входами схемы «И» 15 блока выдачи результата.

Выход схемы «И» 8 блока анализа операндов и выход источника 10 сигнала «умножение» устройства управления соединены со входами схемы «И» 1б блока выдачи результата.

Выход схемы «И» 9 блока анализа операндов и выход источника 10 сигнала «умножение» устройства управления соединены со входами схемы «И» 17 блока выдачи результата, Выход схемы «И» 8 блока анализа операндов и выход источника 14 сигнала «сложение» устройства управления соединены со входами четвертой схемы «И» 18 блока выдачи резул ьт ат а.

Выходы схем «И» 15, 1б блока выдачи операндов и схемы «И» 12 блока анализа операндов соединены со входами схемы «ИЛИ» 19 блока выдачи результата.

Выходы схем «И» 17, 18 блока выдачи результата и схемы «И» 11 блока анализа < перандов соединены со входами схемы «ИЛИ»

20 блока выдачи результата.

Выход схемы «ИЛИ» 19 блока выдачи ðåзультата соединен с разрешающим входом схемы опроса регистра 21 первого операнда этого же блока.

Выход схемы «ИЛИ» 20 блока выдачи результата соединен с разрешающим входом схемы опроса регистра 22 второго операнда этого же блока.

Выходы схем опроса регистров 21, 22 операндов блока выдачи результата и выход апоминающего устройства соединены со входами схемы «ИЛИ» 28 блока выдачи результата.

Операнды, участвующие в операциях, находятся в регистре б первого операнда и в регистре 5 второго операнда.

Если первый (второй) операнд равен нулю, то на выходе схемы «И» 8 (9) появится сигнал, который через схему «ИЛИ» 13 запретит формирование адреса таблиц, а значит и обращение к запоминающему устройству за суммой или произведением операндов, находящихся в регистрах 5 и б. В этом случае, при выполнении суммирования, на выходе схемы

«И» 18 (15) появится сигнал, который через схему «ИЛИ» 20 (19) разрешит выдачу на кодовые шины результата содержимого регисгра второго (первого) опер аида; при выполнении умножения сигнал появится на выходе схем

«И» 1б(17), который через схему «ИЛИ»

19(20) разрешит выдачу на кодовые шины результата содержимого первого (второго) регистра, т. е. код нуля.

Если первый (второй) сомножитель равен

«1», то на выходе схемы «И» 11(12) появится сигнал, также запрещающий через схему

«ИЛИ» 18 обращение за результатом умножения к запоминающему устройству. Этот же сигнал через схему «ИЛИ» 20(19) разрешит выдачу на кодовые шины результата содержимого регистра второго (первого) операнда.

В случае равенства нулю обоих операндов при умножении и суммировании или равенстве единице при умножении, на кодовые шины результата выдается содержимое обоих операндов.

Предмет изобретения

Табличное суммирующе-множительное усгройство, содержащее запоминающее устройство, схему формирования адресов таблиц, регистры первого и второго операндов и устройство управления, отличающееся тем,. что, с целью упрощения устройства и сокращения времени выполнения операций, оно содержит блок выдачи результата и блок анализа, входы которого подключены к выходам регистоов первого и второго операндов, выходы блока анализа операндов подсоединены через схемы

«И» ко входам первой и второй схем «ИЛИ» блока выдачи результата, выход первой схемы «ИЛИ» блока выдачи результата соединен со входом схемы опроса регистра второго операнда, выход которой подключен к триггерам регистра второго операнда, выход второй схемы «ИЛИ» блока выдачи результата соединен со входом схемы опроса регистра первого операнда, выход которой подключен к триггерам регистра первого операнда.

253442

Составитель А. А. Плащий

Редактор Э. Рубан Техред А. А. Камышникова Корректор С. А. Кузовенковй

Заказ 282/18 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва Ж-35, Раушская наб., д. 4 5

Типография, пр. Сапунова, 2