Псевдоморфный гетеростуктурный модулировано-легированный полевой транзистор

Иллюстрации

Показать всеИзобретение относится к электронной технике, а именно к полупроводниковым приборам, предназначенным для усиления СВЧ-электромагнитных колебаний. Гетероструктурный модулировано-легированный полевой транзистор содержит фланец, пьедестал, гетероэпитаксиальную структуру, буферный слой, исток, затвор, сток и омические контакты. Пьедестал имеет толщину по меньшей мере равную 150 мкм и изготовлен из теплопроводящего слоя CVD поликристаллического алмаза, выполненного с имплантированным Ni и отожженным. Поверх пьедестала расположена базовая подложка из GaAs, буферный слой, гетероэпитаксиальная гетероструктура на основе GaAs/AlGaAs/InGaAs, а на поверхности гетероэпитаксиальной структуры, между истоком, затвором и стоком, последовательно размещены дополнительные слои теплопроводящего поликристаллического алмаза, барьерный слой из двуокиси гафния и дополнительный барьерный слой из оксида металла, при этом барьерные слои выполнены с суммарной толщиной 1,0-4,0 нм. В области затвора барьерные слои размещены под затвором, непосредственно на эпитаксиальной структуре в виде градиентного слоя из GaAs n-типа проводимости. Технический результат заключается в повышении теплоотвода от пьедестала и активной области транзистора, обеспечении минимальных утечек тока затвора и достижении наименьшего коэффициента шума в ГГц-диапазоне частот. 4 з.п. ф-лы, 5 ил., 2 табл.

Реферат

Изобретение относится к электронной технике, а именно к полупроводниковым приборам, предназначенным для усиления СВЧ-электромагнитных колебаний.

Гетероструктурные полевые транзисторы с модулированным легированием (ПТМЛ, MODFET) на основе соединений полупроводниковых материалов групп AIIIBV в настоящее время являются самыми быстродействующими полевыми транзисторами, позволяя одновременно достигать наименьшие коэффициенты шума в ГГц-диапазоне частот. Высокое быстродействие достигается за счет эффекта увеличения дрейфовой скорости электронов, образующих двумерный электронный газ у интерфейса модулировано-легированной гетероструктуры (МЛГС).

Из "Уровня техники" известен полевой СВЧ-транзистор, содержащий подложку, на которой сформирован буферный слой из широкозонного полупроводника, на котором расположен активный слой из узкозонного полупроводника с электродами истока, стока и затвора. Кроме того, активный слой под электродом затвора выполнен неравномерно-легированным. При этом концентрация легирующей примеси в направлении электрод истока - электрод стока монотонно возрастает от значения, соответствующего концентрации остаточных примесей, до значения, соответствующего концентрации примесей в буферном слое, а концентрация примесей в буферном слое на 4-5 порядков превышает концентрацию остаточных примесей в активном слое (см. А.С. СССР №1118245, опубл. 19.06.1995).

Недостатками известного устройства являются низкое значение СВЧ-мощности, низкое значение теплоотвода от активной части транзистора и наличие низкочастотных шумов.

Кроме того, известен полевой транзистор на основе нитридов галлия и алюминия, структура которого последовательно включает: подложку, слой GaN, барьерный слой, выполненный из двух подслоев: Al0,2Ga0,8N, на нем GaN. На структуре выполнены контакты: сток, исток и затвор с соответствующими промежутками между ними; далее выполнено диэлектрическое покрытие из MgO, Sc2O3 или SiNx. Между контактами диэлектрическое покрытие находится на барьерном слое и служит для защиты открытых поверхностей барьерного слоя от внешних воздействий, см. B. Luo et al. The role of cleaning conditions and epitaxial layer structure on reliability of Sc2O3 and MgO passivation on AlGaN/GaN HEMTS, Solid-State Electronics, 46, pp.2185-2190, 2002.

Недостатком известного устройства является высокий уровень деградации, обусловленный низким значением теплоотвода от активной части транзистора.

Задачей настоящего изобретения является устранение всех вышеуказанных недостатков.

Технический результат заключается в повышении теплоотвода от пьедестала и активной области транзистора, обеспечении минимальных утечек тока затвора и достижении наименьшего коэффициента шума в ГГц-диапазоне частот.

Технический результат обеспечивается тем, что гетероструктурный модулированно-легированный полевой транзистор содержит фланец, пьедестал, гетероэпитаксиальную структуру, буферный слой, исток, затвор, сток и омические контакты. Пьедестал имеет толщину по меньшей мере равную 150 мкм и изготовлен из теплопроводящего слоя CVD поликристаллического алмаза, выполненного с имплантированным Ni и отожженным. Поверх пьедестала расположена базовая подложка из GaAs, буферный слой, гетероэпитаксиальная гетероструктура на основе GaAs/AlGaAs/InGaAs, а на поверхности гетероэпитаксиальной структуры, между истоком, затвором и стоком, последовательно размещены дополнительные слои теплопроводящего поликристаллического алмаза, барьерный слой из двуокиси гафния и дополнительный барьерный слой из оксида металла, при этом, барьерные слои выполнены с суммарной толщиной 1,0-4,0 нм. Кроме того, в области затвора барьерные слои размещены под затвором, непосредственно на эпитаксиальной структуре в виде градиентного слоя из GaAs n-типа проводимости.

В соответствии с частными случаями выполнения устройство имеет следующие особенности.

Дополнительный барьерный слой может быть выполнен из Al2O3, или из ZrO2, или из La2O3, или из Y2O3.

Сущность настоящего изобретения поясняется следующими иллюстрациями:

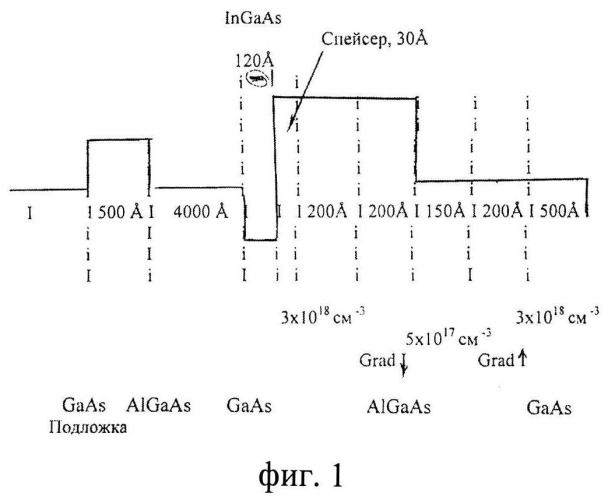

фиг.1 - схематическое изображение энергетических зон у модулированно-легированного гетероперехода n-AlGaAs/GaAs;

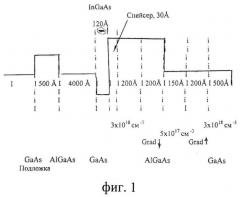

фиг.2 - отображает кристалл транзистора;

фиг.3 - отображает зависимость доли DX-центров в общем числе введенных доноров от уровня легирования слоя AlXGa1-XAs:Si в МЛГС AlGaAs/GaAs;

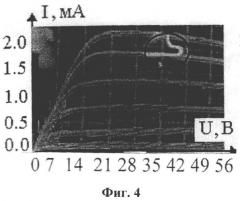

фиг.4 - приведены вольтамперные характеристики мощного транзистора СВЧ без дополнительных слоев на поверхности кристалла транзистора;

фиг.5 - приведены вольтамперные характеристики мощного транзистора СВЧ с дополнительными слоями.

На фиг.2 отображены следующие конструктивные элементы:

1 - базовая подложка из полуизолирующего GaAs;

2 - первый буферный слой;

3 - второй буферный слой из GaAs;

4 - сверхрешетка из AlXGa1-XAs/GaAs;

5 - третий буферный слой;

6 - сильнолегированный n-AlXGa1-XAs;

7 - спейсер AlXGa1-XAs;

8 - сглаживающий слой;

9 - канал InyGa1-yAs;

10 - сглаживающий слой;

11 - спейсер AlXGa1-XAs;

12 - сильнолегированный слой n-типа;

13 - барьерный слой;

14 - барьерный слой n-GaAs;

15 - градиентный слой;

16 - контактный слой;

17 - исток;

18 - затвор;

19 - сток;

20 - омические контакты;

21 - дополнительный теплопроводящий слой CVD полиалмаза;

22 - дополнительный барьерный слой из двуокиси гафния;

23 - дополнительный барьерный слой из двуокиси металла.

Кристалл транзистора крепят на подслой из AuGe, который размещают на пьедестале из теплопроводящего слоя CVD полиалмаза, подвергнутого отжигу после имплантации Ni в его приповерхностные слои. На другой стороне пьедестала размещают слой припоя AuSn. Затем вся структура размещается на фланец.

СВЧ-транзистор разработан на основе эпитаксиальной гетероструктуры GaAs/AlGaAs/InGaAs. Конструкция гетероструктуры приведена в таблице №1, а в таблице №2 представлены основные электрофизические параметры гетеростуктур.

| Таблица 1 | |||

| Слой транзисторной гетероструктуры, Назначение | Состав x, y | Толщина | УровеньЛегирования,см-3 |

| базовая подложка из полуизолирующего GaAs | 625±25 мкм | ||

| первый буферный слой | 200 нм | Нелегированный | |

| второй буферный слой из GaAs | 200 нм | Нелегированный | |

| сверхрешетка из AlXGa1-XAs/GaAs | 0,22/0,00 | (2 нм/2 нм)×10 | Нелегированный |

| третий буферный слой | 0,22 | 100 нм | Нелегированный |

| сильнолегированный n-AlXGa1-XAs | 0,22 | 4,5 нм | 3×1018 |

| спейсер AlXGa1-XAs | 0,22 | 2 нм | Нелегированный |

| сглаживающий слой | 3 нм | Нелегированный | |

| канал InyGa1-yAs | 0,16-0,18 | 12 нм | Нелегированный |

| сглаживающий слой | 1,5 нм | Нелегированный | |

| спейсер AlXGa1-XAs | 0,22 | 2 нм | Нелегированный |

| сильнолегированный слой n-типа | 0,22 | 16 нм | 3×1018 |

| барьерный слой n-типа | 0,22 | 13 нм | 5×1016 |

| барьерный слой n-GaAs | 15 нм | 5×1016 | |

| градиентный слой n-типа | 20 нм | 5×1016- 4×1018 | |

| контактный слой n-типа | 50 нм | 4×1018 |

| Таблица 2 | ||

| Температура, K | Слоевая концентрация носителей заряда в канале не менее, см-2 | Подвижность носителей заряда в канале не менее, см2/(B*c) |

| 77 | 3,0*1012 | 1,3*104 |

| 300 | 3,0*1012 | 5,0*103 |

Изготовление многослойных наногетероструктур твердых растворов GaAs/AlGaAs/InGaAs осуществлялось молекулярно-пучковой эпитаксией.

Настоящее устройство производят следующим образом.

На фланце марки МД-40 толщиной 1600 мкм размещают слой припоя состава AuSn толщиной 25 мкм, затем в заготовленный в качестве пьедестала слой теплопроводящего CVD поликристаллического алмаза толщиной ~170 мкм, в обе приповерхностные области которого, предварительно, способом имплантации введен никель и проведен отжиг. Затем после размещения на поверхности теплопроводящего слоя CVD поликристаллического алмаза размещают подслой из AuGe с содержанием Ge до 12%, толщиной ~25 мкм. Затем на поверхности подслоя AuGe устанавливают кристалл транзистора (фиг.3). Кристалл транзистора содержит последовательно размещенные базовую подложку 1, состоящую из полуизолирующего GaAs толщиной 625 мкм, первый нелегированный буферный слой 2, толщиной 200 нм, второй нелегированный буферный слой 3 из GaAs толщиной 200 нм, сверхрешетку 4 AlXGa1-XAs/GaAs - нелегированный слой толщиной (2 нм/2 нм)*10, третий нелегированный буферный слой 5 толщиной 100 нм, сильнолегированный слой 6 AlXGa1-XAs n-типа концентрацией 3*108 см-3, толщиной 4,5 нм, спейсер 7 AlXGa1-XAs, нелегированный, толщиной 2 нм, нелегированный сглаживающий слой 8 толщиной 3 нм, канал 9 из InyGa1-yAs, нелегированный, толщиной 12 нм, нелегированный сглаживающий слой 10 толщиной 15 нм, спейсер 11 AlXGa1-XAs, нелегированный, толщиной 2 нм, сильнолегированный слой 12 Hs AlXGa1-XAs толщиной 16 нм, барьерный слой 13 толщиной 13 нм, барьерный слой 14 из GaAs n-типа толщиной 15 нм, градиентный слой 15 из GaAs n-типа толщиной 20 нм, низкоомный локальный контактный слой 16 n-типа толщиной 50 нм, исток 17, затвор 18, сток 19, омические контакты 20. Кроме того, устройство снабжают дополнительными слоями, размещенными между истоком 17, затвором 18 и стоком 19. Дополнительные слои выполняют в виде теплопроводящего CVD поликристаллического алмаза 21, барьерного слоя из двуокиси гафния 22 и дополнительного барьерного слоя из оксида металла 23, в качестве которого может быть использован Al2O3, или ZrO2, или La2O3, или Y2O3. При этом барьерные слои 22, 23 выполнены с суммарной толщиной около 4,0 нм. В области затвора 18 барьерные слои 22, 23 размещены под затвором 18, непосредственно на эпитаксиальной структуре в виде градиентного слоя 15 из GaAs n-типа проводимости.

Преимуществами настоящего устройства являются:

1) снижение плотности ростовых дефектов и улучшение электрической изоляции между каналом транзистора и подложкой за счет выполнения дополнительного буферного слоя в виде короткопериодной сверхрешетки AlXGa1-XAs/GaAs;

2) улучшение ограничения носителей в канале короткозатворного транзистора;

3) обеспечение оптимизации отвода тепла из активной области кристалла транзистора и минимизации утечек.

4) отсутствие трудоемких операций при изготовлении;

5) увеличение пробивного напряжения транзистора на по меньшей мере 30%.

На фигурах 4 и 5 приведены вольт-амперные характеристики: фиг.4 - без слоя изолирующего поликристаллического алмаза, на поверхности кристалла СВЧ транзистора, между истоком, затвором и стоком и дополнительных барьерных слоев под затвором; 5) - со слоями изолирующего поликристаллического алмаза на поверхности кристалла транзистора, между истоком, затвором и стоком, а также дополнительными слоями из двуокиси гафния и оксида алюминия под затвором транзистора и поверхизолирующего поликристаллического алмаза.

Размещение слоя изолирующего поликристаллического алмаза на поверхности кристалла СВЧ-транзистора, между истоком, затвором и стоком, уменьшает тепловое сопротивление транзисторной структуры более чем в 1.5 раза и благодаря наличию на поверхности кристалла транзистора слоя теплопроводящего поликристаллического алмаза одновременно с барьерными слоями двуокиси гафния и оксида алюминия, размещенных под затвором, повышает величину пробивного напряжения на более 30%, что обеспечивает повышение эффективности предложенного изобретения.

Все вышеперечисленные преимущества позволяют создавать твердотельные СВЧ-блоки и модули с улучшенными параметрами, предназначенные для антенных фазированных решеток и других радиоэлектронных систем.

1. Гетероструктурный модулированно-легированный полевой транзистор, содержащий фланец, пьедестал, гетероэпитаксиальную структуру, буферный слой, исток, затвор, сток и омические контакты, отличающийся тем, что пьедестал имеет толщину по меньшей мере равную 150 мкм и изготовлен из теплопроводящего слоя CVD поликристаллического алмаза, выполненного с имплантированным Ni и отожженным, поверх пьедестала расположена базовая подложка из GaAs, буферный слой, гетероэпитаксиальная гетероструктура на основе GaAs/AlGaAs/InGaAs, а на поверхности гетероэпитаксиальной структуры, между истоком, затвором и стоком, последовательно размещены дополнительные слои теплопроводящего поликристаллического алмаза, барьерный слой из двуокиси гафния и дополнительный барьерный слой из оксида металла, при этом барьерные слои выполнены с суммарной толщиной 1,0-4,0 нм, кроме того, в области затвора барьерные слои размещены под затвором, непосредственно на эпитаксиальной структуре в виде градиентного слоя из GaAs n-типа проводимости.

2. Транзистор по п.1, отличающийся тем, что дополнительный барьерный слой выполнен из Al2O3.

3. Транзистор по п.1, отличающийся тем, что дополнительный барьерный слой выполнен из ZrO2.

4. Транзистор по п.1, отличающийся тем, что дополнительный барьерный слой выполнен из La2O3.

5. Транзистор по п.1, отличающийся тем, что дополнительный барьерный слой выполнен из Y2O3.