Устройство хранения и передачи данных с исправлением ошибок в двух байтах информации

Иллюстрации

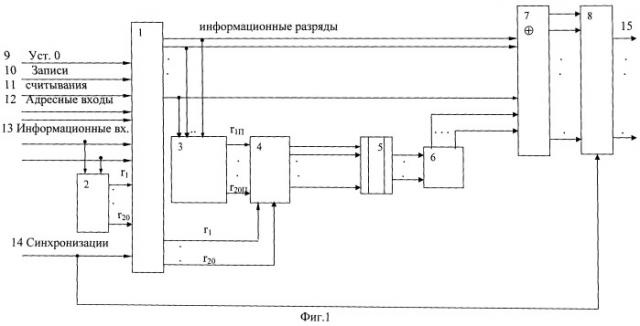

Показать всеИзобретение относится к области телемеханики, автоматики и вычислительной техники и может быть использовано в устройствах хранения и передачи информации. Техническим результатом является повышение отказоустойчивости устройства за счет коррекции ошибок в двух байтах информации. Устройство содержит узел памяти, входной блок кодирования, выходной блок кодирования, блок вычисления синдрома ошибки, дешифратор, блок хранения векторов ошибок, корректор, блок элементов И. 1 ил., 1 табл., 1 прилож.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для повышения достоверности функционирования запоминающих устройств.

Известно самокорректирующееся устройство [1], использующее корректирующий код (наиболее часто используется код Хемминга, корректирующий одиночную ошибку и обнаруживающий двойную ошибку).

Недостатком устройства является низкая обнаруживающая способность кода, так как обнаруживаются только двойные ошибки.

Наиболее близким по техническому решению является устройство хранения и передачи данных с исправлением ошибок в байте информации и обнаружением ошибок в байтах информации [2], содержащее узел памяти, входной блок кодирования, выходной блок кодирования, блок вычисления синдрома ошибки, дешифратор, коммутатор, блок коммутаторов, корректор, блок корректоров, первый блок элементов ИЛИ, второй блок элементов ИЛИ, инвертор, элемент И, блок элементов И, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, двадцатичетырехразрядные информационные входы, вход синхронизации, информационные выходы, выход сигнала «ошибка», вход установки в нулевое состояние, вход записи, вход считывания, адресные входы подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, вход синхронизации подключен к пятому входу узла памяти и к первому входу блока элементов И, информационные входы подключены к шестым входам узла памяти и к входам входного блока кодирования, который формирует значения контрольных разрядов r1 r2, r3, r4, r5, r6, r7, r8 путем сложения по модулю 2 информационных символов x1, x2 x3, z1 z2 z3, a1 a2 a3, c1 c2 c3, e1 e2 e3, f1 f2 f3, g1 g2 g3, h1 h2 h3, поступающих на входы входного блока кодирования, в соответствии с правилом: r1x1⊕z1⊕a1⊕c1⊕e1⊕f1⊕g1⊕h1; r2=x2⊕z2⊕a2⊕c2⊕e2⊕f2⊕g2⊕h2; r3=x3⊕z3⊕a3⊕c3⊕e3⊕f3⊕g3⊕h3; r4=x1⊕z3⊕a2⊕c2⊕e1⊕e3⊕f1⊕f2⊕g1⊕g2⊕g3; r5=x2⊕x3⊕z1⊕a3⊕c1⊕c3⊕e1⊕e2⊕f2⊕g1⊕g2⊕g3; r6=x3⊕z2⊕z3⊕a1⊕c1⊕c2⊕e2⊕f1⊕f3⊕g1⊕g2⊕g3; r7=x3⊕z3⊕a1⊕a3⊕c2⊕e1⊕f2⊕g1⊕g2⊕g3; r8=x1⊕x2⊕z2⊕a2⊕a3⊕c3⊕e3⊕f2⊕f3⊕g1⊕g2⊕g3, которые поступают на седьмые входы узла памяти, информационные выходы узла памяти подключены соответственно к первым входам корректора, блока корректоров и к входам выходного блока кодирования, который формирует значения проверочных контрольных разрядов r1П, r2П, r3П, r4П, r5П, r6П r7П r8П путем сложения по модулю 2 информационных символов x1Пx2Пx3П, z1Пz2Пz3П, a1Пa2Пa3П, c1Пc2Пc3П, e1Пe2Пe3П, f1Пf2Пf3П, g1Пg2Пg3П, h1Пh2Пh3П, поступающих на входы входного блока кодирования с информационных выходов узла памяти, в соответствии с правилом:: r1П=x1П⊕z1П⊕a1П⊕c1П⊕e1П⊕f1П⊕g1П⊕h1П; r2П=x2П⊕z2П⊕a2П⊕c2П⊕e2П⊕f2П⊕g2П⊕h2П; r3П=x3П⊕z3П⊕a3П⊕c3П⊕e3П⊕f3П⊕g3П⊕h3П; r4П=x1П⊕z3П⊕a2П⊕a3П⊕c2П⊕e1П⊕e3П⊕f1П⊕f2П⊕g1П⊕g2П⊕g3П; r5П=x2П⊕x3П⊕z1П⊕a3П⊕c1П⊕c3П⊕e1П⊕e2П⊕f2П⊕g1П⊕g2П⊕g3П; r6П=x3П⊕z2П⊕z3П⊕a1П⊕c1П⊕c2П⊕e2П⊕f1П⊕f3П⊕g1П⊕g2П⊕g3П; r7П=x3П⊕z3П⊕a1П⊕a3П⊕c2П⊕e1П⊕f2П⊕g1П⊕g2П⊕g3П; r8П=x1П⊕x2П⊕z2П⊕a2П⊕a3П⊕c3П⊕e3П⊕f2П⊕f3П⊕g1П⊕g2П⊕g3П, выходы выходного блока кодирования подключены к первым входам блока вычисления синдрома ошибки, к вторым входам которого подключены выходы контрольных разрядов узла памяти, первые выходы блока вычисления синдрома ошибки подключены к первым входам дешифратора, к первым входам коммутатора, к входам первого блока элементов ИЛИ и к первым входам блока коммутаторов, вторые выходы блока вычисления синдрома ошибки подключены к вторым входам дешифратора и к вторым входам первого блока элементов ИЛИ, выходы дешифратора подключены к входам второго блока элементов ИЛИ, при этом первый выход дешифратора подключен к второму входу коммутатора, а вторые выходы подключены к вторым входам блока коммутаторов, выход второго блока элементов ИЛИ через инвертор подключен к первому входу элемента И, второй вход которого подключен к выходу первого блока элементов ИЛИ, выход элемента И является выходом сигнала «ошибка», выходы коммутатора подключены к вторым входам корректора, выходы блока коммутаторов подключены к вторым входам блока корректоров, выходы корректора и блока корректоров подключены к вторым входам блока элементов И, выходы которого являются информационными выходами устройства.

Недостатком устройства является низкая корректирующая способность ошибок, так как корректируются только одиночные байты ошибок.

Целью изобретения является повышение отказоустойчивости устройства за счет коррекции ошибок в двух байтах информации.

Поставленная цель достигается тем, что устройство, содержащие узел памяти, входной блок кодирования, выходной блок кодирования, блок вычисления синдрома ошибки, дешифратор, корректор, блок элементов И, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, отличающееся тем, что дополнительно содержит блок хранения векторов ошибок, вход установки в нулевое состояние, вход записи, вход считывания, адресные входы подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, вход синхронизации подключен к пятому входу узла памяти и к первому входу блока элементов И, информационные входы подключены к шестым входам узла памяти и к входам входного блока кодирования, который формирует значения контрольных разрядов r 1 f , r 2 f , r 3 f , r 4 f , r 5 f , r 6 f , r 7 f , r 8 f , r 9 g , r 10 g , r 11 g , r 12 g , r 13 g , r 14 g , r 15 g , r 16 g , r 17 g , r 18 g , r 19 g , r 20 g , путем сложения по модулю 2 информационных символов a0a1a2a3, b0b1b32b3, c0c1c2c3, d0d1d2d3, e0e1e2e3, f0f1f2f3, g0g1g2g3, h0h1h2h3, i0i1i2i3, j0j1j2j3, k0k1k2k3, l0l1l2l3, m0m1m2m3, n0n1n2n3, o0o1o2o3, p0p1p2p3, поступающих на входы входного блока кодирования, в соответствии с правилом:

r 1 f = a 0 ⊕ b 0 ⊕ c 0 ⊕ d 0 ⊕ e 0 ⊕ f 0 ⊕ g 0 ⊕ h 0 ⊕ i 0 ⊕ j 0 ⊕ k 0 ⊕ l 0 ⊕ m 0 ⊕ n 0 ⊕ o 0 ;

r 2 f = a 1 ⊕ b 1 ⊕ c 1 ⊕ d 1 ⊕ e 1 ⊕ f 1 ⊕ g 1 ⊕ h 1 ⊕ i 1 ⊕ j 1 ⊕ k 1 ⊕ l 1 ⊕ m 1 ⊕ n 1 ⊕ o 1 ;

r 3 f = a 2 ⊕ b 2 ⊕ c 2 ⊕ d 2 ⊕ e 2 ⊕ f 2 ⊕ g 2 ⊕ h 2 ⊕ i 2 ⊕ j 2 ⊕ k 2 ⊕ l 2 ⊕ m 2 ⊕ n 2 ⊕ o 2 ;

r 4 f = a 3 ⊕ b 3 ⊕ c 3 ⊕ d 3 ⊕ e 3 ⊕ f 3 ⊕ g 3 ⊕ h 3 ⊕ i 3 ⊕ j 3 ⊕ k 3 ⊕ l 3 ⊕ m 3 ⊕ n 3 ⊕ o 3 ;

r 5 f = b 0 ⊕ c 0 ⊕ d 0 ⊕ e 0 ⊕ f 0 ⊕ g 0 ⊕ h 0 ⊕ i 0 ⊕ j 0 ⊕ k 0 ⊕ l 0 ⊕ m 0 ⊕ n 0 ⊕ o 0 ⊕ p 0 ;

r 6 f = b 1 ⊕ c 1 ⊕ d 1 ⊕ e 1 ⊕ f 1 ⊕ g 1 ⊕ h 1 ⊕ i 1 ⊕ j 1 ⊕ k 1 ⊕ l 1 ⊕ m 1 ⊕ n 1 ⊕ o 1 ⊕ p 1 ;

r 7 f = b 2 ⊕ c 2 ⊕ d 2 ⊕ e 2 ⊕ f 2 ⊕ g 2 ⊕ h 2 ⊕ i 2 ⊕ j 2 ⊕ k 2 ⊕ l 2 ⊕ m 2 ⊕ n 2 ⊕ o 2 ⊕ p 2 ;

r 8 f = b 3 ⊕ c 3 ⊕ d 3 ⊕ e 3 ⊕ f 3 ⊕ g 3 ⊕ h 3 ⊕ i 3 ⊕ j 3 ⊕ k 3 ⊕ l 3 ⊕ m 3 ⊕ n 3 ⊕ o 3 ⊕ p 3 ;

r 9 g = a 2 ⊕ a 3 ⊕ b 2 ⊕ c 2 ⊕ c 3 ⊕ d 0 ⊕ d 1 ⊕ e 1 ⊕ e 3 ⊕ f 1 ⊕ f 2 ⊕ g 2 ⊕ g 3 ⊕ h 0 ⊕ i 0 ⊕ i 3 ⊕ j 0 ⊕ j 2 ⊕ k 0 ⊕ k 2 ⊕ k 3 ⊕ l 0 ⊕ l 1 ⊕ m 0 ⊕ m 1 ⊕ m 3 ⊕ n 0 ⊕ n 1 ⊕ n 2 ⊕ o 0 ⊕ o 1 ⊕ o 3

r 10 g = a 2 ⊕ b 3 ⊕ c 1 ⊕ d 1 ⊕ d 3 ⊕ e 1 ⊕ e 2 ⊕ f 1 ⊕ f 2 ⊕ f 3 ⊕ g 0 ⊕ g 3 ⊕ h 0 ⊕ h 3 ⊕ i 0 ⊕ i 2 ⊕ j 0 ⊕ j 2 ⊕ j 3 ⊕ k 0 ⊕ k 1 ⊕ l 1 ⊕ l 3 ⊕ m 0 ⊕ m 1 ⊕ m 2 ⊕ n 0 ⊕ n 1 ⊕ n 3 ⊕ p 3 ;

r 11 g = a 1 ⊕ b 1 ⊕ b 2 ⊕ b 3 ⊕ c 1 ⊕ c 2 ⊕ d 1 ⊕ d 2 ⊕ e 0 ⊕ f 0 ⊕ f 3 ⊕ g 0 ⊕ g 2 ⊕ h 0 ⊕ h 2 ⊕ h 3 ⊕ i 0 ⊕ i 1 ⊕ j 0 ⊕ j 1 ⊕ j 3 ⊕ k 1 ⊕ k 2 ⊕ l 0 ⊕ l 1 ⊕ l 2 ⊕ m 3 ⊕ n 3 ⊕ o 2 ⊕ p 2 ⊕ p 3 ;

r 12 g = a 0 ⊕ a 3 ⊕ b 0 ⊕ b 3 ⊕ c 0 ⊕ c 2 ⊕ d 0 ⊕ d 2 ⊕ d 3 ⊕ e 0 ⊕ e 1 ⊕ e 3 ⊕ f 0 ⊕ f 1 ⊕ f 3 ⊕ g 0 ⊕ g 1 ⊕ g 2 ⊕ h 0 ⊕ h 1 ⊕ h 2 ⊕ h 3 ⊕ j 3 ⊕ k 0 ⊕ k 2 ⊕ k 3 ⊕ l 2 ⊕ l 3 ⊕ m 1 ⊕ n 1 ⊕ n 3 ⊕ ⊕ o 1 ⊕ o 2 ⊕ p 1 ⊕ p 2 ⊕ p 3 ;

r 13 g = a 0 ⊕ b 2 ⊕ b 3 ⊕ c 0 ⊕ c 2 ⊕ c 3 ⊕ d 0 ⊕ d 3 ⊕ e 1 ⊕ e 2 ⊕ f 0 ⊕ f 2 ⊕ g 0 ⊕ g 1 ⊕ h 0 ⊕ h 1 ⊕ h 2 ⊕ h 3 ⊕ i 0 ⊕ i 1 ⊕ j 1 ⊕ j 2 ⊕ k 1 ⊕ l 0 ⊕ l 2 ⊕ m 1 ⊕ m 2 ⊕ m 3 ⊕ n 0 ⊕ n 2 ⊕ n 3 ⊕ ⊕ o 0 ⊕ o 1 ⊕ o 3 ⊕ p 0 ⊕ p 1 ⊕ p 2 ;

r 14 g = a 2 ⊕ a 3 ⊕ b 0 ⊕ b 3 ⊕ c 0 ⊕ c 3 ⊕ d 1 ⊕ d 2 ⊕ e 3 ⊕ f 2 ⊕ g 3 ⊕ h 1 ⊕ h 2 ⊕ h 3 ⊕ i 0 ⊕ i 2 ⊕ j 0 ⊕ j 1 ⊕ j 3 ⊕ k 2 ⊕ k 3 ⊕ l 1 ⊕ l 2 ⊕ l 3 ⊕ m 1 ⊕ m 3 ⊕ n 0 ⊕ o 0 ⊕ o 1 ⊕ o 2 ⊕ p 0 ⊕ p 2 ⊕ p 3 ;

r 15 g = a 0 ⊕ a 1 ⊕ a 2 ⊕ a 3 ⊕ b 0 ⊕ b 3 ⊕ c 0 ⊕ c 2 ⊕ c 3 ⊕ d 0 ⊕ d 1 ⊕ e 0 ⊕ e 1 ⊕ e 2 ⊕ f 2 ⊕ f 3 ⊕ g 1 ⊕ g 3 ⊕ h 0 ⊕ i 0 ⊕ i 3 ⊕ j 0 ⊕ j 2 ⊕ k 1 ⊕ l 0 ⊕ l 1 ⊕ l 2 ⊕ m 0 ⊕ m 1 ⊕ n 0 ⊕ n 1 ⊕ n 3 ⊕ ⊕ o 0 ⊕ o 1 ⊕ o 2 ⊕ o 3 ⊕ p 3 ;

r 16 g = a 0 ⊕ a 3 ⊕ b 1 ⊕ b 2 ⊕ b 3 ⊕ c 0 ⊕ c 1 ⊕ c 2 ⊕ d 3 ⊕ e 2 ⊕ e 3 ⊕ f 0 ⊕ f 2 ⊕ f 3 ⊕ g 2 ⊕ g 3 ⊕ h 1 ⊕ i 0 ⊕ i 2 ⊕ i 3 ⊕ j 1 ⊕ j 2 ⊕ j 3 ⊕ k 0 ⊕ k 2 ⊕ l 0 ⊕ l 1 ⊕ m 0 ⊕ m 3 ⊕ n 3 ⊕ o 0 ⊕ o 2 ⊕ p 1 ⊕ p 2 ;

r 17 g = a 0 ⊕ a 1 ⊕ a 2 ⊕ c 0 ⊕ c 1 ⊕ c 2 ⊕ c 3 ⊕ d 0 ⊕ d 1 ⊕ d 3 ⊕ e 0 ⊕ e 1 ⊕ e 3 ⊕ f 1 ⊕ f 2 ⊕ g 0 ⊕ g 1 ⊕ g 2 ⊕ g 3 ⊕ h 0 ⊕ h 1 ⊕ i 0 ⊕ i 1 ⊕ i 2 ⊕ j 1 ⊕ j 2 ⊕ j 3 ⊕ k 2 ⊕ l 1 ⊕ l 3 ⊕ m 0 ⊕ n 1 ⊕ n 2 ⊕ n 3 ⊕ o 0 ⊕ o 1 ⊕ o 2 ⊕ p 0 ⊕ p 1 ⊕ p 3 ;

r 18 g = a 0 ⊕ a 2 ⊕ a 3 ⊕ b 2 ⊕ b 3 ⊕ c 3 ⊕ d 0 ⊕ d 1 ⊕ d 3 ⊕ e 1 ⊕ e 2 ⊕ f 3 ⊕ g 2 ⊕ h 1 ⊕ i 1 ⊕ i 2 ⊕ i 3 ⊕ j 1 ⊕ j 2 ⊕ k 0 ⊕ k 1 ⊕ l 0 ⊕ l 1 ⊕ l 2 ⊕ l 3 ⊕ n 1 ⊕ n 3 ⊕ o 0 ⊕ o 1 ⊕ p 0 ⊕ p 1 ⊕ p 2 ;

r 19 g = a 0 ⊕ a 1 ⊕ a 3 ⊕ b 1 ⊕ b 3 ⊕ c 0 ⊕ d 0 ⊕ d 2 ⊕ d 3 ⊕ e 0 ⊕ e 1 ⊕ f 0 ⊕ f 2 ⊕ g 1 ⊕ g 2 ⊕ g 3 ⊕ h 1 ⊕ h 3 ⊕ i 0 ⊕ i 2 ⊕ j 0 ⊕ j 3 ⊕ k 0 ⊕ k 2 ⊕ l 1 ⊕ m 0 ⊕ m 1 ⊕ m 2 ⊕ n 0 ⊕ n 1 ⊕ o 0 ⊕ o 2 ⊕ o 3 ⊕ p 0 ⊕ p 2 ⊕ p 3 ;

r 20 g = a 1 ⊕ a 2 ⊕ b 0 ⊕ b 3 ⊕ c 0 ⊕ c 1 ⊕ c 3 ⊕ d 0 ⊕ d 1 ⊕ d 2 ⊕ e 3 ⊕ f 2 ⊕ f 3 ⊕ g 0 ⊕ g 2 ⊕ g 3 ⊕ h 0 ⊕ h 2 ⊕ h 3 ⊕ i 1 ⊕ i 3 ⊕ j 1 ⊕ j 3 ⊕ k 0 ⊕ k 2 ⊕ k 3 ⊕ l 0 ⊕ l 2 ⊕ m 0 ⊕ m 3 ⊕ n 0 ⊕ n 3 ⊕ o 0 ⊕ o 3 ⊕ p 0 ⊕ p 1 ⊕ p 3 ,

выходы входного блока кодирования подключены к седьмым входам узла памяти, информационные выходы узла памяти подключены соответственно к первым входам корректора и к входам выходного блока кодирования, который формирует значения проверочных контрольных разрядов r 1 П f , r 2 П f , r 3 П f , r 4 П f , r 5 П f , r 6 П f , r 7 П f , r 8 П f , r 9 П g , r 10 П g , r 11 П g , r 12 П g , r 13 П g , r 14 П g , r 15 П g , r 16 П g , r 17 П g , r 18 П g , r 19 П g , r 20 П g , путем сложения по модулю 2 информационных символов a0Пa1Пa2Пa3П, b0Пb1Пb2Пb3П, c0Пc1Пc2Пc3П, d0Пd1Пd2Пd3П, e0Пe1Пe2Пe3П, f0Пf1Пf2Пf3П, g0Пg1Пg2Пg3П, h0Пh1Пh2Пh3П, i0Пi1Пi2Пi3П, j0Пj1Пj2Пj3П, k0Пk1Пk2Пk3П, l0Пl1Пl2Пl3П, m0Пm1Пm2Пm3П, n0Пn1Пn2Пn3П, o0Пo1Пo2Пo3П, p0Пp1Пp2Пp3П, поступающих на входы входного блока кодирования с информационных выходов узла памяти, в соответствии с правилом:

r 1 П f = a 0 П ⊕ b 0 П ⊕ c 0 П ⊕ d 0 П ⊕ e 0 П ⊕ f 0 П ⊕ g 0 П ⊕ h 0 П ⊕ i 0 П ⊕ j 0 П ⊕ k 0 П ⊕ l 0 П ⊕ m 0 П ⊕ n 0 П ⊕ o 0 П ;

r 2 П f = a 1 П ⊕ b 1 П ⊕ c 1 П ⊕ d 1 П ⊕ e 1 П ⊕ f 1 П ⊕ g 1 П ⊕ h 1 П ⊕ i 1 П ⊕ j 1 П ⊕ k 1 П ⊕ l 1 П ⊕ m 1 П ⊕ n 1 П ⊕ o 1 П ;

r 3 П f = a 2 П ⊕ b 2 П ⊕ c 2 П ⊕ d 2 П ⊕ e 2 П ⊕ f 2 П ⊕ g 2 П ⊕ h 2 П ⊕ i 2 П ⊕ j 2 П ⊕ k 2 П ⊕ l 2 П ⊕ m 2 П ⊕ n 2 П ⊕ o 2 П ;

r 4 П f = a 3 П ⊕ b 3 П ⊕ c 3 П ⊕ d 3 П ⊕ e 3 П ⊕ f 3 П ⊕ g 3 П ⊕ h 3 П ⊕ i 3 П ⊕ j 3 П ⊕ k 3 П ⊕ l 3 П ⊕ m 3 П ⊕ n 3 П ⊕ o 3 П ;

r 5 П f = b 0 П ⊕ c 0 П ⊕ d 0 П ⊕ e 0 П ⊕ f 0 П ⊕ g 0 П ⊕ h 0 П ⊕ i 0 П ⊕ j 0 П ⊕ k 0 П ⊕ l 0 П ⊕ m 0 П ⊕ n 0 П ⊕ o 0 П ⊕ p 0 П ;

r 6 П f = b 1 П ⊕ c 1 П ⊕ d 1 П ⊕ e 1 П ⊕ f 1 П ⊕ g 1 П ⊕ h 1 П ⊕ i 1 П ⊕ j 1 П ⊕ k 1 П ⊕ l 1 П ⊕ m 1 П ⊕ n 1 П ⊕ o 1 П ⊕ p 1 П ;

r 7 П f = b 2 П ⊕ c 2 П ⊕ d 2 П ⊕ e 2 П ⊕ f 2 П ⊕ g 2 П ⊕ h 2 П ⊕ i