Операционный усилитель с парафазным выходом

Иллюстрации

Показать всеИзобретение относится к области радиотехники. Технический результат заключается в повышении стабильности операционного усилителя на постоянном токе. Устройство содержит входной дифференциальный каскад с токовыми выходами, согласованный с первой шиной источника питания, первое и второе токовые зеркала, согласованные со второй шиной источника питания, первый и второй токостабилизирующие двухполюсники, первый и второй токовые выходы входного дифференциального каскада связаны с эмиттером первого, второго, третьего и четвертого дополнительных транзисторов противоположного типа проводимости, базы первого и третьего дополнительных транзисторов объединены и подключены к источнику вспомогательного напряжения, коллектор первого дополнительного транзистора соединен со входом первого токового зеркала, коллектор третьего дополнительного транзистора соединен со входом второго токового зеркала, первый вспомогательный выход устройства связан с объединенными базами второго и четвертого дополнительных транзисторов через первый дополнительный резистор, второй вспомогательный выход устройства связан с объединенными базами второго и четвертого дополнительных транзисторов через второй дополнительный резистор. 3 з.п. ф-лы, 5 ил.

Реферат

Предлагаемое изобретение относится к области радиотехники, электромеханики и может использоваться в мостовых усилителях мощности с малым напряжением питания, фазорасщепителях, активных RC-фильтрах, драйверах дифференциальных линий связи и системах управления маломощными электродвигателями постоянного тока и т.п.

В задачах усиления и преобразования сигналов широко используются операционные усилители (ОУ) с парафазным Rail-to-rail выходом [1-17], при котором выходные напряжения ОУ изменяются от «шины питания Е п ( + ) » до «шины питания Е п ( − ) ».

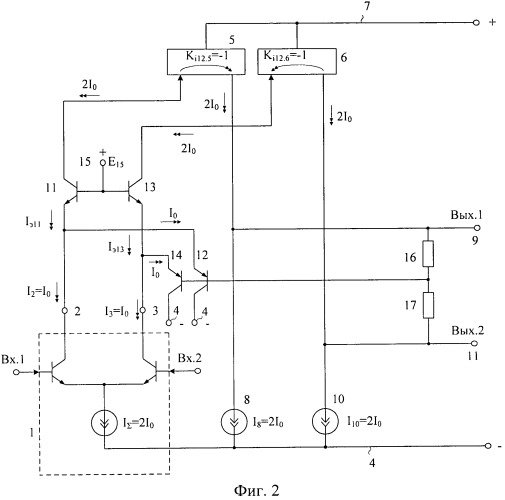

Ближайшим прототипом заявляемого устройства является Rail-to-rail операционный усилитель, представленный в патентной заявке US 2006/0006910 fig.1. Он содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, согласованный с первой 4 шиной источника питания, первое 5 и второе 6 токовые зеркала, согласованные со второй 7 шиной источника питания, первый 8 токостабилизирующий двухполюсник, связанный с выходом первого 5 токового зеркала и первым 9 вспомогательным выходом устройства, второй 10 токостабилизирующий двухполюсник, связанный с выходом второго 6 токового зеркала и вторым 11 вспомогательным выходом устройства.

Существенный недостаток известного операционного усилителя-прототипа состоит в том, что при больших сопротивлениях первого 8 и второго 10 токостабилизирующих двухполюсников, которые для повышения коэффициента усиления (Ку) часто заменяются на источники опорного тока, в нем не обеспечивается стабильный статический режим.

Основная задача предполагаемого изобретения состоит в создании условий, при которых схема ОУ имеет (при повышенном Ку) высокую стабильность на постоянном токе и взаимосвязанные парафазные выходы, статическое напряжение на которых равно потенциалу общей шины.

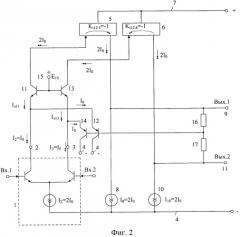

Поставленная задача решается тем, что в операционном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, согласованный с первой 4 шиной источника питания, первое 5 и второе 6 токовые зеркала, согласованные со второй 7 шиной источника питания, первый 8 токостабилизирующий двухполюсник, связанный с выходом первого 5 токового зеркала и первым 9 вспомогательным выходом устройства, второй 10 токостабилизирующий двухполюсник, связанный с выходом второго 6 токового зеркала и вторым 11 вспомогательным выходом устройства, предусмотрены новые элементы и связи - первый 2 токовый выход входного дифференциального каскада 1 связан с эмиттером первого 11 и второго 12 дополнительных транзисторов противоположного типа проводимости, второй 3 токовый выход входного дифференциального каскада 1 связан с эмиттером третьего 13 и четвертого 14 дополнительных транзисторов противоположного типа проводимости, базы первого 11 и третьего 13 дополнительных транзисторов объединены и подключены к источнику вспомогательного напряжения 15, коллектор первого 11 дополнительного транзистора соединен со входом первого 5 токового зеркала, коллектор третьего 13 дополнительного транзистора соединен со входом второго 6 токового зеркала, первый 9 вспомогательный выход устройства связан с объединенными базами второго 12 и четвертого 14 дополнительных транзисторов через первый дополнительный резистор 16, второй 11 вспомогательный выход устройства связан с объединенными базами второго 12 и четвертого 14 дополнительных транзисторов через второй дополнительный резистор 17, причем коллекторы второго 12 и четвертого 14 дополнительных транзисторов связаны с первой 4 шиной источника питания.

На чертеже фиг.1 представлена схема усилителя-прототипа, а на чертеже фиг.2 - схема заявляемого устройства в соответствии с пп.1-2 формулы изобретения.

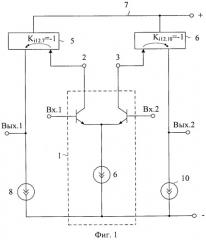

На чертеже фиг.3 представлена схема заявляемого устройства в соответствии с пп.3-4 формулы изобретения.

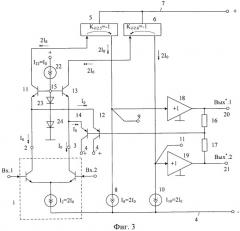

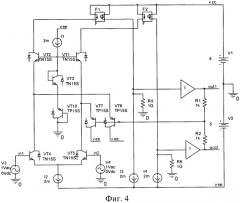

На чертеже фиг.4 представлена схема фиг.3 в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На чертеже фиг.5 приведена зависимость коэффициента усиления по напряжению от частоты ОУ фиг.4 при R1=R2=1 ком. Выходное синфазное напряжение ОУ в этом случае близко к нулю: Uвых.с=2 мВ.

Операционный усилитель с парафазным выходом фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, согласованный с первой 4 шиной источника питания, первое 5 и второе 6 токовые зеркала, согласованные со второй 7 шиной источника питания, первый 8 токостабилизирующий двухполюсник, связанный с выходом первого 5 токового зеркала и первым 9 вспомогательным выходом устройства, второй 10 токостабилизирующий двухполюсник, связанный с выходом второго 6 токового зеркала и вторым 11 вспомогательным выходом устройства. Первый 2 токовый выход входного дифференциального каскада 1 связан с эмиттером первого 11 и второго 12 дополнительных транзисторов противоположного типа проводимости, второй 3 токовый выход входного дифференциального каскада 1 связан с эмиттером третьего 13 и четвертого 14 дополнительных транзисторов противоположного типа проводимости, базы первого 11 и третьего 13 дополнительных транзисторов объединены и подключены к источнику вспомогательного напряжения 15, коллектор первого 11 дополнительного транзистора соединен со входом первого 5 токового зеркала, коллектор третьего 13 дополнительного транзистора соединен со входом второго 6 токового зеркала, первый 9 вспомогательный выход устройства связан с объединенными базами второго 12 и четвертого 14 дополнительных транзисторов через первый дополнительный резистор 16, второй 11 вспомогательный выход устройства связан с объединенными базами второго 12 и четвертого 14 дополнительных транзисторов через второй дополнительный резистор 17, причем коллекторы второго 12 и четвертого 14 дополнительных транзисторов связаны с первой 4 шиной источника питания.

На чертеже фиг.2, в соответствии с п.2 формулы изобретения, первый 9 вспомогательный выход устройства связан с объединенными базами второго 12 и четвертого 14 дополнительных транзисторов через последовательно соединенные первый буферный усилитель 18 и первый 16 дополнительный резистор, а второй 11 вспомогательный выход устройства связан с объединенными базами второго 12 и четвертого 14 дополнительных транзисторов через последовательно соединенные второй 19 буферный усилитель и второй 17 дополнительный резистор.

На чертеже фиг.3, в соответствии с п.3 формулы изобретения, в качестве основных выходов устройства 20 и 21 используются выходы соответствующих первого 18 и второго 19 буферный усилителей.

На чертеже фиг.3, в соответствии с п.4 формулы изобретения, источник вспомогательного напряжения 15 реализован на основе последовательно включенных вспомогательного токостабилизирующего двухполюсника 22 и двух р-n переходов 23, 24.

Рассмотрим работу схемы фиг.2.

Статический режим по току транзисторов ОУ фиг.2 и токи выходов 2 (I2) и 3 (I3) устанавливаются источником опорного тока входного дифференциального каскада 1 (IΣ=2I0) и токостабилизирующими двухполюсниками 8 и 10:

I 2 = I 3 = I 0 , ( 1 )

I ý11 = I 2 + I ý12 = I 8 = 2I 0 , (2)

I ý13 = I 3 + I ý14 = I 10 = 2I 0 , (3)

где Iэi - токи эмиттеров i-го транзистора.

За счет выбора соотношения токов IΣ, I8, I10 устанавливается заданный уровень эмиттерных токов транзисторов 12 и 14, которые рекомендуется выбирать с учетом неравенства Iэ12=1э14≤I0.

Уровень выходных статических синфазных напряжений на выходах 9 и 11 определяются следующим уравнением

U в ы х .9 = E 15 − U э б 11 − U э б 12 + I б 12 R 16 ≈ E 15 − 1,4 B , ( 4 )

U в ы х .10 = E 15 − U э б 13 − U э б 14 + I б 14 R 17 ≈ E 15 − 1,4 B , ( 5 )

где Uэб≈0,7 B - статическое напряжение эмиттер-база транзисторов 11, 12, 13, 14;

Е15 - напряжение источника вспомогательного напряжения 15.

При выборе E15=1,4 В из (4) и (5) получаем, что выходное статическое синфазное напряжение ОУ близко к нулю.

Если на входы ОУ подается дифференциальный сигнал, то это вызывает противофазные изменения эмиттерных и коллекторных токов транзисторов 11, 13, которые через токовые зеркала 5 и 6 передаются в цепь нагрузки, роль которой выполняют резисторы 16 и 17. Поэтому коэффициент усиления по напряжению схемы

К у = u в ы х .1 − u в ы х .2 u в х .1 − u в х .2 = R 16 + R 17 2 ϕ т I 0 , ( 6 )

где φт≈25 мВ - температурный потенциал.

Замечательная особенность схемы фиг.2 - широкий диапазон изменения напряжения на выходах 9 и 11. При типовом построении токовых зеркал 5 и 6 и токостабилизирующих двухполюсников 8 и 10 амплитуда положительного ( U m ( + ) ) и отрицательного ( U m ( − ) ) выходного сигнала ОУ может достигать суммы напряжений положительного E п ( + ) и отрицательного Е п ( − ) источников питания:

U m ( + ) = U m ( − ) ≈ E п ( + ) + Е п ( − ) .

Это весьма существенно для схем с низковольтным питанием.

Для получения больших мощностей и токов нагрузки в схеме фиг.3 введены буферные усилители 18 и 19.

Результаты моделирования схемы фиг.4 подтверждают высокую стабильность статического режима при больших значениях коэффициента усиления (фиг.5), что обеспечивается общей отрицательной обратной связью по синфазному сигналу.

Таким образом, предлагаемое схемотехническое решение ОУ характеризуется высокой стабильностью статического режима при повышенном Ку и широким диапазоном изменения выходного напряжения, что является его существенным преимуществом в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.590.455 fig.1

2. Патент US 6.069.534 fig.6

3. Патент US 6.801.084

4. Патент US 6.218.905

5. Патент US 6.639.477 fig.3В

6. Патент US 6.809.594 fig.1

7. Патент US 5.714.909 fig.2

8. Патент US 7.042.295

9. Патент US 4.511.857 fig.3а

10. Патент US 5.345.073 fig.3

11. Патент US 7.486.140 fig.1, fig.6

12. Патент ЕР 1351381 fig.2

13. Патентная заявка US 2011/0012678

14. Патентная заявка US 2006/0139098

15. Патент US 7.649.418 fig.3А

16. Патент US 6.657.465 fig.2

17. Патент JP 58-31768

1. Операционный усилитель с парафазным выходом, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, согласованный с первой (4) шиной источника питания, первое (5) и второе (6) токовые зеркала, согласованные со второй (7) шиной источника питания, первый (8) токостабилизирующий двухполюсник, связанный с выходом первого (5) токового зеркала и первым (9) вспомогательным выходом устройства, второй (10) токостабилизирующий двухполюсник, связанный с выходом второго (6) токового зеркала и вторым (11) вспомогательным выходом устройства, отличающийся тем, что первый (2) токовый выход входного дифференциального каскада (1) связан с эмиттером первого (11) и второго (12) дополнительных транзисторов противоположного типа проводимости, второй (3) токовый выход входного дифференциального каскада (1) связан с эмиттером третьего (13) и четвертого (14) дополнительных транзисторов противоположного типа проводимости, базы первого (11) и третьего (13) дополнительных транзисторов объединены и подключены к источнику вспомогательного напряжения (15), коллектор первого (11) дополнительного транзистора соединен со входом первого (5) токового зеркала, коллектор третьего (13) дополнительного транзистора соединен со входом второго (6) токового зеркала, первый (9) вспомогательный выход устройства связан с объединенными базами второго (12) и четвертого (14) дополнительных транзисторов через первый дополнительный резистор (16), второй (11) вспомогательный выход устройства связан с объединенными базами второго (12) и четвертого (14) дополнительных транзисторов через второй дополнительный резистор (17), причем коллекторы второго (12) и четвертого (14) дополнительных транзисторов связаны с первой (4) шиной источника питания.

2. Операционный усилитель с парафазным выходом по п.1, отличающийся тем, что первый (9) вспомогательный выход устройства связан с объединенными базами второго (12) и четвертого (14) дополнительных транзисторов через последовательно соединенные первый буферный усилитель (18) и первый (16) дополнительный резистор, а второй (11) вспомогательный выход устройства связан с объединенными базами второго (12) и четвертого (14) дополнительных транзисторов через последовательно соединенные второй (19) буферный усилитель и второй (17) дополнительный резистор.

3. Операционный усилитель с парафазным выходом по п.1, отличающийся тем, что в качестве основных выходов устройства (20) и (21) используются выходы соответствующих первого (18) и второго (19) буферный усилителей.

4. Операционный усилитель с парафазным выходом по п.1, отличающийся тем, что источник вспомогательного напряжения (15) реализован на основе последовательно включенных вспомогательного токостабилизирующего двухполюсника (22) и двух р-n переходов (23), (24).