Цифровой синтезатор для формирования сигналов многочастотной телеграфии

Иллюстрации

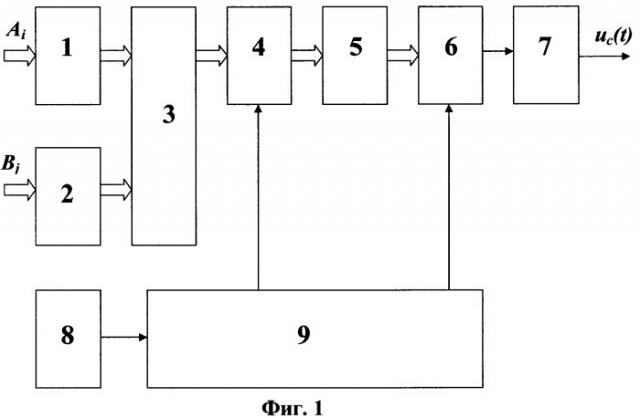

Показать всеИзобретение относится к электронно-вычислительной технике и радиотехнике, предназначено для синтеза сигналов многочастотной телеграфии и может быть использовано в современных адаптивных системах связи. Достигаемый технический результат - возможность формирования сигналов для многочастотной телеграфии и повышение быстродействия. Цифровой синтезатор для формирования сигналов многочастотной телеграфии содержит первый регистр памяти 1, второй регистр памяти 2, сумматор 3, цифровой накопитель 4, преобразователь кодов 5, цифроаналоговый преобразователь (ЦАП) 6, фильтр нижних частот (ФНЧ) 7, опорный генератор 8 и блок формирования и задержки 9. 1 ил.

Реферат

Изобретение относится к электронно-вычислительной технике и радиотехнике, предназначено для синтеза сигналов многочастотной телеграфии и может быть использовано в современных адаптивных системах связи.

Известны цифровые синтезаторы частот, содержащие генератор тактовых импульсов, блок задержки, первый и второй регистры памяти, счетчик с предварительной установкой, первый и второй блоки постоянного запоминания, ЦАП, ФНЧ, первый и второй цифровые накопители [1].

Наиболее близким техническим решением (прототипом) является цифровой синтезатор частот, содержащий эталонный генератор и блок задержки; регистр сдвига, цифровой накопитель, функциональный преобразователь код-синус, цифроаналоговый преобразователь (ЦАП), фильтр нижних частот (ФНЧ) [2].

Положительный технический результат - возможность формирования сигналов многочастотной телеграфии и повышение быстродействия - достигается за счет того, что в цифровом синтезаторе для формирования сигналов многочастотной телеграфии, содержащем последовательно соединенные опорный генератор и блок формирования и задержки; первый регистр памяти; последовательно соединенные цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является аналоговым выходом цифрового синтезатора, а его первым цифровым входом является вход первого регистра памяти; выходы блока формирования и задержки подключены к тактовым входам цифрового накопителя и цифроаналогового преобразователя соответственно, новым является то, что введены второй регистр памяти и сумматор; выход второго регистра памяти подсоединен к второму входу сумматора; выход первого регистра памяти подсоединен к первому входу сумматора, а выход сумматора подключен к входу цифрового накопителя; вход второго регистра памяти является вторым цифровым входом цифрового синтезатора.

Цифровой синтезатор для формирования сигналов многочастотной телеграфии содержит первый регистр памяти 1, второй регистр памяти 2, сумматор 3, цифровой накопитель 4, преобразователь кодов 5, цифроаналоговый преобразователь (ЦАП) 6, фильтр нижних частот (ФНЧ) 7, выход которого является аналоговым выходом цифрового синтезатора; опорный генератор 8 и блок формирования и задержки 9; первым и вторым цифровыми входами цифрового синтезатора являются информационные входы первого и второго регистров памяти 1 и 2 соответственно.

Цифровой синтезатор работает следующим образом.

На информационный вход первого регистра памяти 1 поступает код Ai, одновременно на вход второго регистра памяти 2 поступает код Bj. Эти коды складываются в сумматоре 3 и код С

будет определять начальную частоту синтезированного сигнала.

Опорный генератор 8 вырабатывает синусоидальный сигнал опорной частоты, из которого в блоке формирования и задержки 9 формируются тактовые импульсы формы «меандр», разнесенные во времени и служащие для синхронизации работы цифрового накопителя 4 и цифроаналогового преобразователя 6.

С приходом первого тактового импульса код С загружается в цифровой накопитель 4, результат суммирования в котором будет изменяться по формуле

Код суммы S поступает на преобразователь кодов 5, который из кода S формирует код sin(S), поступающий на информационные входы ЦАП 6, где формируется ступенчатый сигнал синусоидальной формы, определяемый кодом С. Фильтр нижних частот 7 пропускает на выход только первую гармонику сформированного сигнала.

Если принять, что ω0=C=Ai+Bj - начальная частота синтезируемого сигнала, Δt=T - длительность тактового интервала, то на выходе ФНЧ 7 будет сформирован сигнал, описываемый формулой:

где Um - амплитуда сигнала.

Частота синтезированного сигнала ω0 будет определяться кодами Ai и Bj, поступающими на входы первого и второго регистров памяти 1 и 2, которые являются цифровыми входами цифрового синтезатора.

Следовательно, изменяя коды Ai и Bj, можно управлять частотой цифрового синтезатора и формировать сигналы многочастотной телеграфии. Скорость перестройки частоты формируемого сигнала не будет превышать одного тактового интервала, поэтому быстродействие данного цифрового синтезатора выше по сравнению с прототипом.

Литература

1. Патент РФ №2058659. МПК Н03В 19/00. Цифровой синтезатор частот / Рябов И.В., Фищенко П.А. Заявл. 23.09.1993. Опубл. 20.04.1996. Бюл. №11. - 4 с.

2. Патент №2452085 Российской Федерации МПК H03L 7/00. Цифровой вычислительный синтезатор для многочастотной телеграфии/ Рябов И.В., Дедов А.Н., Юрьев П.М., Рябова С.А., Толмачев С.В. Заявл. 07.07.2011. Опубл. 27.05.2012. Бюл. №15. 4 с. (прототип).

Цифровой синтезатор для формирования сигналов многочастотной телеграфии, содержащий последовательно соединенные опорный генератор и блок формирования и задержки; первый регистр памяти; последовательно соединенные цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является аналоговым выходом цифрового синтезатора, а его первым цифровым входом является вход первого регистра памяти; выходы блока формирования и задержки подключены к тактовым входам цифрового накопителя и цифроаналогового преобразователя соответственно, отличающийся тем, что введены второй регистр памяти и сумматор; выход второго регистра памяти подсоединен к второму входу сумматора; выход первого регистра памяти подсоединен к первому входу сумматора, а выход сумматора подключен к входу цифрового накопителя; вход второго регистра памяти является вторым цифровым входом цифрового синтезатора.