Вычислительная система

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано при создании вычислительных систем повышенной надежности. Техническим результатом является повышение надежности работы системы. Вычислительная система содержит трехканальный центральный системный модуль, к которому через системную магистраль подключены n вычислительных модулей, m модулей связи и запоминающее устройство санкционированного доступа. В состав вычислительной системы введен установленный между выходами каналов центрального системного модуля в магистраль переключатель каналов, к управляющим входам которого подключены выходы блока контроля и управления, подключенного входами к выходам каналов центрального системного модуля, кроме того, к системной магистрали подключен таймер, а к ее управляющим шинам подключены установочными входами перестраиваемый формирователь синхроимпульсов и управляемый источник вторичного электропитания, выходы которых являются соответственно синхронизирующими выходами и выходами постоянного и импульсного питания. Центральный системный модуль запускает модули на выполнение тестов, сравнивает результаты вычислений модулей и, проводя периодическое тестирование этих модулей, использует в дальнейшей работе результаты правильно работающего модуля. 16 з.п. ф-лы, 21 ил.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для создания вычислительных систем, к которым предъявляются повышенные требования по надежности при длительной работе в неблагоприятных внешних условиях (широкий диапазон изменения температуры окружающей среды от - 60 до +125 градусов по Цельсию, внешние механические воздействия(удары и широкополосная вибрация) и электромагнитные воздействия. Кроме того, система должна работать длительное время в полях непрерывного ионизирующего излучения и быть устойчивой к мощным импульсам ионизирующего излучения, вызванным вспышками на Солнце, авариями ядерных энергетических установок или направленным противодействием.

Известна трехканальная вычислительная система (см. АС №1156273), содержащая в каждом канале внешнее устройство и вычислительное устройство, информационный выход которого подключен к первому входу первого мажоритарного элемента и к первому входу первого элемента сравнения всех каналов. Второй вход первого элемента сравнения соединен с выходом первого мажоритарного элемента и со входом внешнего устройства, выход которого подключен к первому информационному входу второго мажоритарного элемента всех каналов, второй и третий информационные входы которого соединены соответственно со вторым и третьим информационными входами вторых мажоритарных элементов других каналов и с выходами внешних устройств соответственно. Выход второго мажоритарного элемента подключен к первому входу второго элемента сравнения и к первому входу вычислительного устройства. Второй вход второго элемента сравнения соединен с первым входом второго мажоритарного элемента, а выход - с выводом связи.

В каждом канале содержится также регистр номера канала, четыре блока анализа, группа элементов «И», контрольный регистр и элемент «ИЛИ», выход которого подключен ко входу прерывания вычислительного устройства. Первый вход контрольного регистра соединен с выходом последовательной передачи информации вычислительного устройства.

Входы контрольного регистра соединены с выходами группы элементов «И». Вторые выходы соединены со входами элемента «ИЛИ». Кроме того, каждый канал содержит элемент «НЕ», а каждый блок анализа выполнен в виде дешифратора, связанного входами с выходами элементов сравнения.

Это известное устройство благодаря установке мажоритарных элементов в выходных информационных шинах вычислителей обеспечивает нейтрализацию неисправности, возникающей в одном из каналов при правильной работе двух других каналов. Кроме того, благодаря введению схем сравнения, подключенных к связям внешних устройств, обеспечивается обнаружение неправильной работы одного из них по отличию его информации от двух других, что позволяет диагностировать отказы внешних устройств путем анализа состояний контрольного регистра вычислительным устройством. Эти свойства являются положительными. Особенно важным является нейтрализация неисправности в одном из каналов вычислительного устройства.

В то же время после возникновения неисправности в одном из каналов надежность дальнейшей работы системы резко снижается, так как возникновение неисправности в любом из двух оставшихся исправными вычислительных устройств приводит к полной неработоспособности системы. Это происходит потому, что интенсивность отказа в двух каналах в два раза больше, чем у одноканального вычислителя. Целесообразно максимально полно использовать имеющуюся избыточность в виде двух дополнительно введенных каналов для сохранения работоспособности системы после возникновения второй неисправности.

Задача сохранения работоспособности системы при возникновении двух неисправностей в системе частично решена в РЕЗЕРВИРОВАННОМ ВЫЧИСЛИТЕЛЬНОМ УСТРОЙСТВЕ (см. АС №1200292). В данном устройстве для повышения надежности между блоками памяти и процессора введен коммутатор, переключающий блоки по сигналам встроенных устройств оперативного контроля.

Общим недостатком известных вычислительных устройств является то, что как для работы схем мажоритации, так и для работы коммутатора, переключающего блоки в процессе работы, требуется синхронная и синфазная работа всех каналов устройства, что обеспечивается введением единого генератора синхроимпульсов. При такой реализации резервирования отказ этого генератора приводит к отказу устройства и системы в целом. Кроме того, наличие временного рассогласования одноименных сигналов разных каналов резервированного устройства требует снижение быстродействия с целью учета межканальных рассогласований, вызванных отличиями задержек элементов разных каналов. Более того, в процессе работы вычислительной системы под влиянием температуры и особенно из-за воздействия внешнего ионизирующего излучения, например, космического пространства происходит деградация параметров электрорадиоизделий, учесть которую при проектировании невозможно.

Наиболее полно задача повышения надежности устройств, работающих при внешних неблагоприятных воздействиях, решена в прототипе - МОДУЛЬНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ (см. АС №747326), наиболее близкой к заявляемой системе. Известная система содержит несколько функциональных модулей, а именно вычислительные модули и модули связи с внешними подсистемами, работающие независимо друг от друга на собственной частоте синхронизации. Для обеспечения взаимодействия между модулями все они подключены к общесистемной магистрали. Для организации обменов по магистрали и управления работой функциональных модулей в систему введен центральный модуль управления (системный модуль), управляющий взаимодействием модулей по общесистемной магистрали.

Системный модуль периодически контролирует работоспособность функциональных модулей и может в случае снижения их быстродействия из-за деградации параметров послать команду в устройства синхронизации выбранного функционального модуля на изменение тактовой частоты, что обеспечивает адаптацию модулей системы к деградации параметров элементов и тем самым повышает надежность функционирования системы при работе в неблагоприятных условиях.

В то же время такая система, несмотря на ряд очевидных достоинств, имеет недостаток, который заключается в наличии центрального модуля, управляющего общесистемной магистралью. Такое построение системы приводит к отказу системы при возникновении отказа в центральном модуле.

С целью повышения надежности работы системы и сохранения работоспособности центрального модуля при возникновении отказов в его оборудовании предлагается

ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА, содержащая несколько функциональных модулей, а именно N вычислительных модулей, и М модулей связи (МС) и центральный - системный модуль (СМ). Дополнительно в систему введены блок контроля и управления (БКУ) и переключатель каналов (ПК) системного модуля, установленный на выходах этого модуля в магистраль.

Кроме того, в систему введены таймер и модуль запоминающего устройства санкционированного доступа (ЗУСД).

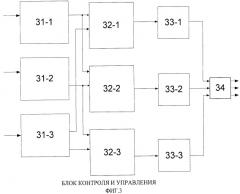

БКУ содержит первый, второй и третий буферные регистры, первую, вторую и третью схемы совпадения. Выход первого буферного регистра подключен к первым входам первой и второй схем совпадения. Выход второго буферного регистра подключен ко второму входу первой схемы и первым входам второй и третьей схемы совпадения, а вход третьего буферного регистра подключен ко вторым входам первой и третьей схем совпадения. Выход каждой схемы совпадения подключен к входу соответствующей каждой схеме триггера неисправностей, подключенных выходами к группе контрольных логических элементов, выходы которой являются выходами блока.

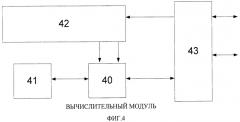

ВМ содержит блок процессора с подключенным к нему через первую двунаправленную связь блоком запоминающего устройства и подключенным через вторую двунаправленную связь блоком связи по магистрали, два входа-выхода которого являются входами-выходами блока, подключенными к магистрали, а управляющий выход этого блока подключен к входу блока синхронизации, выходы которого подключены к синхровходам процессора.

МС содержит процессор с подключенными к нему через внутреннюю магистраль запоминающим устройством и устройством связи по магистрали, два входа-выхода которого являются входами-выходами модуля, подключенными к магистрали, а выход устройства связи подключен к входу устройства синхронизации, выходы которого подключены к синхровходам процессора, который по двунаправленной связи через кодирующее-декодирующее устройство подключен к приемопередатчику мультиплексной линии связи с периферийными устройствами.

Таймер содержит первый, второй и контрольный счетчики- формирователи, выходы которых подключены к схеме контроля. При этом первый, второй, контрольный счетчики и схема контроля подключены соответственно через первую, вторую, контрольную и схемную двунаправленные линии связи к таймерному устройству связи по магистрали, два входа-выхода которой являются входами-выходами таймера, подключенными к магистрали.

ИВЭП содержит модуль постоянного питания (МПП) и модуль импульсного питания (МИП), силовые входы, установочный вход МПП, три управляющих входа МИП являются одноименными входами ИВЭП, а выходы МПП и МИП соответственно выходами постоянного и импульсного питания ИВЭП.

МПП содержит три конвертора, частотные выходы которых подключены к частотным входам блока управления и контроля (БУК), а выходы конверторов подключены к входам БУК и через блок отключения подключены к входам блока выравнивания, выход которого является выходом и контрольным выходом МПП. При этом выходы БУК подключены к управляющим входам блока отключения, а вход-выход БУК является входом-выходом модуля, подключенным к магистрали.

МИП содержит три ветви, в каждой из которых последовательно включены два полевых транзистора. Ветви объединены с каждой из сторон, одна из которых является силовым входом модуля, вторая - выходом, а три управляющих сигнала разведены таким образом, что каждый из них подключен к затворам двух транзисторов, установленных в разных ветвях, образуя выборку «2 из 3».

Конвертор содержит последовательно включенные фильтр, защитный диод, трансформатор с включенным в первичную обмотку транзистором-прерывателем, выпрямляющий диод после вторичной обмотки и выходной фильтр, выход которого является выходом конвертора. Этот выход подключен к входу преобразователя напряжения в частоту, подключенного выходом к элементу развязки, выход которого является частотным выходом конвертора и подключен к входу частотно-импульсного модулятора (ЧИМ), выход которого подключен к базе транзистора прерывателя.

БУК содержит первый, второй, третий и четвертый частотные счетчики. Входы первых трех являются частотными входами блока, подключенными соответственно к частотным выходам первого, второго и третьего конверторов. Вход четвертого счетчика подключен к выходу схемы преобразования напряжения в частоту, вход которой является контрольным входом блока, подключенным к выходу МПП. Выход первого счетчика подключен к первым входам первого и второго сумматоров. Выход второго счетчика подключен ко второму входу первого сумматора и первым входам второго и третьего сумматоров, а выход третьего счетчика подключен ко вторым входам третьего и первого сумматоров. Выход четвертого счетчика подключен к первому входу четвертого сумматора, ко второму входу которого подключен выход регистра кода, выход которого подключен ко вторым входам всех схем сравнения, а вход этого регистра объединен с входом регистра допуска, выходы которого подключены к первым входам первой, второй, третьей и четвертой схем сравнения. К выходам этих схем подключены входы соответствующих им первого, второго, третьего и четвертого триггеров неисправностей, выходы которых подключены к управляющей группе логических схем, выходы которой являются выходами блока, подключенными к управляющим входам блока отключения.

Фильтр содержит включенный в плюсовую шину диод, анод которого является входом, а катод - выходом фильтра. При этом между плюсовой и минусовой шиной включен низкочастотный конденсатор, а каждая из шин и плюсовая, и минусовая через свои высокочастотные конденсаторы подключены к шине земли.

ФСИ содержит первый, второй и третий перестраиваемые генераторы импульсов, установочный вход которых является одноименным входом формирователя, а выход каждого из генераторов подключен к входу своего, соответственно первого, второго и третьего, блока фазирования, фазирующий выход каждого из которых подключен к фазирующим входам двух других блоков и фазирующим входам блока мажоритации, а синхронизирующие выходы блоков фазирования подключены к синхронизирующим входам блока мажоритации, выходы которого являются выходами формирователя.

Перестраиваемый генератор импульсов содержит группу последовательно включенных инверторов, выходы которых подключены к входам первого мультиплексора, выход которого подключен к входу первого инвертора и является выходом генератора. Выходы этого счетчика подключены к первым входам первой схемы сравнения, ко вторым входам которой подключены выходы первого регистра кода частоты, а инкрементный и декрементный выходы этой схемы подключены к одноименным входам первого счетчика кода частоты, выходы которого подключены к управляющим входам первого мультиплексора. При этом установочный вход первого регистра кода частоты и первого счетчика кода частоты является установочным входом модулятора, конвертора, МПП и ИВЭП в целом.

Блок синхронизации ВМ и устройство синхронизации МС выполнены идентично и каждый из них содержит управляемый генератор импульсов, управляющий вход которого является одноименным входом блока (устройства), а выход подключен к входу сдвигающего регистра, выходы которого являются синхронизирующими выходами блока (устройства).

Перестраиваемый генератор импульсов и управляемый генератор импульсов реализованы аналогично друг другу.

ЧИМ содержит несколько последовательно включенных инверторов, выходы которых подключены к входам второго мультиплексора, выход которого подключен к входу первого инвертора и является выходом модулятора, вход которого является входом второго счетчика кода частоты. Выходы этого счетчика подключены к первым входам второй схемы сравнения, ко вторым входа которой подключены выходы второго регистра кода частоты, а инкрементный и декрементный выходы этой схемы подключены к одноименным входам второго счетчика кода частоты, выходы которого подключены к управляющим входам второго мультиплексора. При этом установочный вход второго регистра кода частоты и вход второго счетчика кода частоты являются установочным входом модулятора.

Блок фазирования содержит элемент «И», первый вход которого является входом блока, подключенным к генератору, а выход элемента подключен к входу сдвигового регистра и входу динамического счетчика, подключенного выходами через дешифратор к запускающему входу триггера останова, выход которого является фазирующим выходом блока и подключен ко второму входу элемента «И» и первому входу мажоритарного элемента, подключенного выходом к входу триггера пуска, выход которого подключен к сбрасывающему входу триггера останова. При этом ко второму и третьему входам мажоритарного элемента подключены выходы триггеров привязки, стробирующий вход которых объединен первым входом элемента «И», а входы являются фазирующими входами блока. Кроме того, выходы четных и нечетных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам f триггеров-формирователей, выходы которых являются синхронизирующими выходами блока.

Динамический триггер, используемый в динамическом счетчике, построен как транзисторный усилитель, к базе транзистора которого кроме резистивного делителя подключена LC цепь, индуктивность которой содержит рабочую обмотку и намотанную поверх нее встречно-компенсационную, концы которой закорочены.

На чертежах (фигуры с 1 по 15) приведен состав вычислительной системы, ее блоков и узлов.

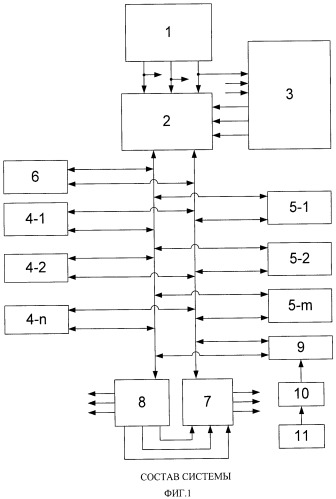

На фигуре 1 приведен состав вычислительной системы, где цифрой 1 обозначен системный модуль, цифрой 2 - переключатель каналов, цифрой 3 обозначен блок контроля и управления, цифрами от 4-1 до 4-n обозначены n вычислительных модулей, цифрами от 5-1 до 5-m обозначены m модулей связи, цифрой 6 обозначен таймер, цифрой 7 - ИВЭП, цифрой 8 - перестраиваемый ФСИ, цифрой 9 обозначено ЗУСД, цифрой 10 - формирователь сигнала, цифрой 11 - датчик внешнего воздействия.

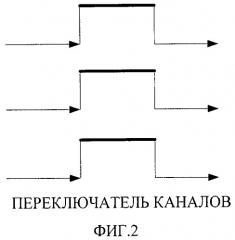

На фигуре 2 приведен переключатель каналов.

На фигуре 3 приведен БКУ, где цифрой от 31-1 до 31-3 обозначены соответственно первый, второй и третий буферные регистры, цифрами от 32-1 до 32-3 обозначены соответственно первая, вторая, третья схемы совпадения, цифрами от 33-1 до 33-3 обозначены соответственно первый, второй, третий триггера неисправностей, а цифрой 34 обозначена контрольная группа логических схем.

На фигуре 4 приведен состав вычислительного модуля, где цифрой 40 обозначен блок процессора, цифрой 41 - блок запоминающего устройства, цифрой 42 обозначен блок синхронизатора, цифрой 43 - блок связи по магистрали.

На фигуре 5 приведен состав модуля связи, где цифрой 50 обозначен процессор, цифрой 51 - запоминающее устройство, цифрой 52 обозначено устройство синхронизации, цифрой 53 - устройство связи, цифрой 54 обозначен кодирующее-декодирующее устройство, цифрой 55 - приемопередатчик мультиплексной линии связи.

На фигуре 6 приведен состав таймера, где цифрой 61 обозначен первый формирователь, цифрой 62 - второй формирователь, цифрой 63 обозначен контрольный формирователь, цифрой 64 - схема контроля, цифрой 65 обозначена схема связи.

На фигуре 7 приведен состав ИВЭП, где цифрой 70 обозначен МПП, а цифрой 71 обозначен МИП.

На фигуре 7-1 приведен состав МПП, где цифрами от 71-1 до 71-3 обозначены соответственно первый, второй и третий конверторы, цифрой 72 обозначен БУК, цифрой 73 - блок отключения, цифрой 74 обозначен блок выравнивания.

На фигуре 7-1-1 приведен состав конвертора, где цифрой 7111 обозначен фильтр, цифрой 7112 - трансформатор, цифрой 7113 обозначен выходной фильтр, цифрой 7114 - преобразователь напряжения в частоту, цифрой 7115 обозначен элемент гальванической развязки, цифрой 7116 - ЧИМ, цифрой 7117 транзистор-прерыватель.

На фигуре 7-1-2 приведен состав БУК, где цифрами от 712-1.1 до 712-1.4 обозначены соответственно первый, второй, третий и четвертый частотные счетчики, цифрами от 712-2.1 до 712-2.4 обозначены соответственно первый, второй, третий, четвертый сумматоры, цифрами от 712-3.1 до 712-3.4 обозначены соответственно первая, вторая, третья, четвертая контрольные схемы сравнения, цифрами от 712-4.1 до 712-4.4 обозначены соответственно первый, второй, третий, четвертый триггера неисправностей, цифрой 712-5 обозначена группа логических элементов, цифрой 712-6 - регистр допуска, цифрой 712-7 обозначен регистр контрольного кода, цифрой 712-8 - контрольный преобразователь напряжения в частоту.

На фигуре 7-1-3 приведен состав фильтра.

На фигуре 7-2 приведен модуль импульсного питания.

На фигуре 8 приведен перестраиваемый ФСИ, где цифрами от 81-1 до 81-3 обозначены соответственно первый, второй, третий перестраиваемые генераторы импульсов, цифрами от 82-1 до 82-3 обозначены соответственно первый, второй и третий блоки фазирования, цифрой 83 обозначен блок мажоритации.

На фигуре 9 приведен частотно-импульсного модулятор, где цифрой 91 обозначены последовательно включенные инверторы, цифрой 92 - второй мультиплексор, цифрой 93 - второй счетчик кода частоты, цифрой 94 обозначен второй счетчик частоты, цифрой 95 - вторая схема сравнения, цифрой 96 обозначен второй регистр кода частоты.

На фигуре 10 приведен состав перестраиваемого генератора импульсов, где цифрой 101 обозначена группа последовательно включенных инверторов, цифрой 102 - второй счетчик кода частоты, цифрой 103 обозначена первая схема сравнения, цифрой 104 - первый счетчик частоты, цифрой 105 обозначен первый регистр кода частоты, цифрой 106 - первый мультиплексор.

На фигуре 10-1 приведен синхронизатор, где цифрой 1011 обозначен генератор, цифрой 1012 - сдвигающий регистр.

На фигуре 11 приведен блок фазирования, где цифрой 110 обозначен элемент И, цифрой 111 - динамический счетчик, цифрой 112 обозначен сдвиговый регистр, цифрой 113 - дешифратор, цифрой 114 обозначен триггер останова, цифрой 115 - триггер пуска, цифрой 116 обозначен мажоритарный элемент, цифрой 117 - триггер привязки, цифрами от 118-1 до 118-f обозначены формирователи синхроимпульсов.

На фигуре 12 приведен динамический триггер.

На фигуре 13 приведен состав ЗУСД, где цифрой 131 обозначен первый накопитель, цифрой 132 - второй накопитель, цифрой 133-1 и цифрой 133-2 обозначены соответственно первый и второй сумматоры метки времени, цифрой 134-1 и цифрой 134-2 обозначены соответственно первый и второй сумматоры массивов.

На фигуре 14 приведен формирователь сигнала, где цифрой 140 обозначен задающий генератор, цифрой 141 - интервальный счетчик, цифрой 142 обозначен интервальный дешифратор, цифрой 143 - триггер, цифрой 144 обозначен логический элемент, цифрой 145 - регистр санкционированного кода, цифрой 146 обозначен дешифратор кода.

На фигуре 15 приведен датчик внешнего воздействия.

Система может быть реализована следующим образом: каждый канал СМ выполнен как малоразрядная (16-разрядная) вычислительная машина, содержащая процессор на основе БИС 1867 ВМ2 и память на БИС 1620 РЕ и 1620 РУ.

Блок процессора ВМ реализуется на БИС микропроцессора 1867 ВМ6, блок запоминающих устройств аналогично памяти СМ на БИС серии 1620, блок связи реализуется на специализированных БИС на основе БМК серии 1556 и 1557, а блок синхронизации на основе БИС 1825 ВБ2, дополненной БИС на БМК серии 1556 и 1557.

МС реализуется на базе микропроцессора 1867 ВМ2 с запоминающим устройством на БИС серии 1620, устройством синхронизации, заимствованным из ВМ, устройством связи выполняется на специализированных БИС на БМК серии 1556 и 1557, кодек использует БИС 1825 ВВ, а приемопередатчик реализуется на специализированных БИС на основе БМК серии 1537 ХМ2.

Таймер, ФСИ, БУК реализуется на БИС 1825 ВБ, дополненной специализированными БИС на основе БМК серии 1556 и 1557.

ИВЭП реализуется на дискретных компонентах с использованием микросхемы преобразования напряжения в частоту ADFC32 фирмы Analog Devices или ее аналога.

БКУ и БУК реализуются на специализированных БИС на базе БМК серии 1555 и 1556, причем в БУК дополнительно используется преобразователь напряжения в частоту ADFC32 фирмы Analog Devices или ее аналога.

Динамический триггер реализуется на транзисторе типа П16 или аналогичном и дискретных элементах (резисторах, конденсаторах и индуктивности с обмотками на ферритовом кольце).

Система работает следующим образом:

Каждый цикл работы, задаваемый таймером, процессоры системного модуля запускают модули на выполнение тестов, по результатам выполнения которых задают в соответствующие регистры ИВЭП, ФСИ и синхронизаторов управляющие коды. В конце каждого цикла происходит сравнение заданных значений с контрольными известными кодами, значение которых устанавливается при включении системы путем занесения фиксированных кодов в соответствующие регистры и счетчики, значение которых корректируется по результатам тестов модулей. При несовпадении выданных каналами системного модуля кодов включается триггер неисправности соответствующего канала. В соответствии с сигналами неисправности процессоров переключатель каналов подключает к общесистемной магистрали исправный канал СМ, который берет на себя управление на очередной цикл работы, а в МПП ИВЭП к блоку выравнивания подключается исправный конвертор. Кроме того, СМ, сравнивания результаты вычислений ВМ и МС, решающих одну и ту же задачу, и проводя периодическое тестирование модулей, использует в дальнейшей работе результаты правильно работающего модуля. ИВЭП, ФСИ и таймер имеют внутреннее резервирование с самоконтролем и управлением внутренним резервом, обеспечивающими достоверную информацию на их выходах.

Таким образом, в предлагаемой системе устранены отсеченные недостатки известных решений в части нейтрализации одиночных катастрофических отказов в ее компонентах. Более того, система сохраняет работоспособность при деградации параметров комплектующих элементов из-за старения, изменения температуры окружающей среды, дозовых факторов от действия ионизирующего излучения, и система обладает повышенной устойчивостью к внешним электромагнитным излучениям благодаря применению динамических триггеров в ответственных и наиболее чувствительных к помехам узлах. Предлагаемая система успешно может использоваться в системах автоматического управления объектами ракетно-космической техники и робототехническими комплексами, работающими в неблагоприятных внешних условиях и полях электромагнитного и ионизирующего излучения.

1. Вычислительная система, содержащая трехканальный центральный системный модуль, к которому через системную магистраль подключены n вычислительных модулей, m модулей связи и запоминающее устройство санкционированного доступа, отличающаяся тем, что в состав вычислительной системы введены установленный между выходами каналов центрального системного модуля в магистраль переключатель каналов, к управляющим входам которого подключены выходы блока контроля и управления, подключенного входами к выходам каналов центрального системного модуля, кроме того, к системной магистрали подключен таймер, а к ее управляющим шинам подключены установочными входами перестраиваемый формирователь синхроимпульсов и управляемый источник вторичного электропитания, выходы которых являются соответственно синхронизирующими выходами и выходами постоянного и импульсного питания, при этом центральный системный модуль запускает модули на выполнение тестов, сравнивает результаты вычислений модулей и, проводя периодическое тестирование этих модулей, использует в дальнейшей работе результаты правильно работающего модуля.

2. Система по п.1, отличающаяся тем, что переключатель каналов содержит три полевых транзистора, истоки которых являются входами, стоки - выходами, а управляющие входы подключены к затворам транзисторов.

3. Система по п.1, отличающаяся тем, что блок контроля и управления содержит первый, второй и третий буферные регистры, входы которых являются входами блока контроля и управления, причем выход первого регистра подключен к первым входам первой и второй схем совпадения, выход второго регистра подключен ко второму входу первой и первым входам второй и третьей схем совпадения, а выход третьего регистра подключен ко вторым входам третьей и первой схем совпадения, при этом выход каждой из схем совпадения подключен к входу своего, соответственно первого, второго и третьего триггера неисправностей, выход каждого из которых подключен к входам контрольной группы логических схем, выходы которой являются выходами блока контроля и управления.

4. Система по п.1, отличающаяся тем, что вычислительный модуль содержит блок процессора с подключенными к нему через первую и вторую магистраль соответственно блоком запоминающих устройств и блоком связи по магистрали, два входа-выхода которого являются входами выходами вычислительного модуля, а выход этого блока подключен к управляющему входу блока синхронизации, выходы которого подключены к синхровходам блока процессора.

5. Система по п.1, отличающаяся тем, что модуль связи содержит процессор с подключенными к нему через магистраль запоминающим устройством и устройством связи по магистрали, два входа-выхода которого являются входами - выходами модуля связи, а выход этого устройства подключен к управляющему входу устройства синхронизации, синхровыходы которого подключены к синхровходам процессора, вход-выход которого через кодирующе-декодирующее устройство подключен к приемопередатчику мультиплексной линии связи, вход-выход которого является входом-выходом модуля связи и системы.

6. Система по п.1, отличающаяся тем, что таймер содержит первый, второй и контрольный счетчики, выходы которых подключены к входам схемы контроля, подключенной через контрольную связь к схеме связи по магистрали, к которой через первую и вторую формировательные связи подключены соответственно первый и второй счетчики-формирователи, а два входа-выхода этой схемы являются входами-выходами таймера.

7. Система по п.1, отличающаяся тем, что источник вторичного электропитания содержит модуль постоянного питания и модуль импульсного питания, силовой, установочный и три управляющих входа которых являются одноименными входами источника вторичного электропитания, а выходы постоянного и импульсного питания модулей - одноименными выходами источника вторичного электропитания.

8. Система по п.1, отличающаяся тем, что перестраиваемый формирователь синхроимпульсов содержит первый, второй и третий перестраиваемые генераторы импульсов, выход каждого из которых подключен к входу своего, соответственно первого, второго и третьего блока фазирования, фазирующий выход каждого из которых подключен к фазирующим входам двух других блоков и фазирующим входам блока мажоритации, к синхронизирующим выходам которого подключены синхронизирующие выходы блоков фазирования, а выходы блока мажоритации являются выходами перестраиваемого формирователя синхроимпульсов.

9. Система по п.7, отличающаяся тем, что модуль постоянного питания содержит три конвертора, частотные выходы которых являются одноименными выходами блока управления и контроля, а выходы подключены к входам блока управления и контроля и через блок отключения подключены к входам блока выравнивания, выход которого является контрольным выходом и выходом модуля постоянного питания, подключенным к контрольному входу блока управления и контроля, выходы которого подключены к управляющим входам блока отключения.

10. Система по п.7, отличающаяся тем, что модуль импульсного питания содержит три идентичных ветви, объединенные с каждой из сторон, в каждой из которых последовательно включены два полевых транзистора, причем одна из объединенных сторон является силовым входом, вторая - выходом, а три управляющих сигнала разведены таким образом, что каждый из них подключен к затворам двух транзисторов, установленных в разных ветвях, образуя выборку «2 из 3».

11. Система по п.9, отличающаяся тем, что конвертор содержит последовательно включенные фильтр, защитный диод, трансформатор с включенным в первичную обмотку транзистором-прерывателем и выходной фильтр, выход которого является выходом конвертора и подключен к преобразователю напряжения в частоту, подключенного выходом к элементу развязки, выход которого является частотным выходом конвертора и подключен к входу частотно-импульсного модулятора, установочный вход которого является одноименным входом конвертора, а выход подключен к базе транзистора-прерывателя.

12. Система по п.8, отличающаяся тем, что блок фазирования содержит элемент И, первый вход которого является входом блока фазирования, выход подключен к входу сдвигового регистра и входу динамического счетчика, подключенного выходами через дешифратор к запускающему входу триггера останова, выход которого является фазирующим выходом блока фазирования и подключен к первому входу элемента И и к первому входу мажоритарного элемента, выход которого подключен к входу триггера пуска, подключенного выходом к сбрасывающему входу триггера останова, а ко второму и третьему входам мажоритарного элемента подключены выходы триггеров привязки, входы которых являются фазирующими входами блока фазирования, при этом выходы четных и нечетных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам f формирователей синхроимпульсов, выходы которых являются синхронизирующими выходами блока фазирования.

13. Система по п.8, отличающаяся тем, что перестраиваемый генератор импульсов содержит группу последовательно включенных инверторов, выходы которых подключены к входам первого мультиплексора, выход которого является фазирующим выходом генератора и подключен к входу первого инвертора группы и входу первого счетчика частоты, подключенного выходом к первым входам первой схемы сравнения, ко вторым входам которой подключены выходы первого регистра кода частоты, а инкрементный и декрементный выходы этой схемы подключены к одноименным входам первого счетчика кода частоты, подключенного выходами к управляющим входам первого мультиплексора, причем входы второго регистра кода частоты и второго счетчика кода частоты являются установочным входом генератора.

14. Система по п.11, отличающаяся тем, что частотно-импульсный модулятор содержит n последовательно включенных инверторов, подключенных выходами к входам второго мультиплексора, выход которого подключен к входу первого инвертора и является выходом модулятора, вход которого является входом второго счетчика частоты, подключенного выходами к первым входам второй схемы сравнения, ко вторым входам которой подключены выходы второго регистра кода частоты, а инкрементный и декрементный выходы этой схемы подключены к одноименным входам второго счетчика кода частоты, подключенного выходами к управляющим входам второго мультиплексора, причем входы второго регистра кода частоты и второго счетчика кода частоты являются установочным входом модулятора.

15. Система по п.11, отличающаяся тем, что блок управления и контроля содержит первый, второй, третий и четвертый частотные счетчики, у которых входы первых трех являются частотными входами блока управления и контроля, а вход четвертого счетчика подключен к выходу контрольного преобразователя напряжения в частоту, вход которого является контрольным входом блока управления и контроля, причем выход первого частотного счетчика подключен к первым входам первого и второго сумматоров, выход второго частотного счетчика подключен к первым входам второго и третьего сумматора, второй вход которого объединен со вторым входом первого сумматора и подключен к выходу третьего частотного счетчика, а выход четвертого счетчика подключен к первому входу четвертого сумматора, ко второму входу которого подключен выход регистра контрольного кода, вход которого является установочным входом блока управления и контроля и объединен с входом регистра допуска, подключенного выходом к первым входам первой, второй, третьей и четвертой контрольных схем сравнения, ко вторым входам которых подключены выходы соответственно первого, второго, третьего и четвертого сумматоров, а выходы всех четырех контрольных схем сравнения подключены к входам соответствующих им соответственно первого, второго, третьего и четвертого триггеров неисправности, выходы которых подключены к входам управляющей группы логических элементов, выходы которой являются выходами блока управления и контроля.

16. Система по п.4, отличающаяся тем, что блок синхронизации содержит управляемый генератор импульсов, подключенный к входу сдвигающего регистра, к запускающему входу которого подключен выход последнего разряда регистра, при этом управляющий вход генератора является входом блока, а выходы сдвигающего регистра - выходами блока синхронизации.

17. Система по п.11, отличающаяся тем, что динамический триггер выполнен как транзисторный усилитель, к базе транзистора которого кроме резисторного делителя подключена LC цепь, индуктивность которой имеет рабочую обмотку и намотанную поверх нее встречно компенсационную, концы которой закорочены.