Устройство для определения оптимального времени подготовки средств системы к применению

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Техническим результатом является расширение функциональных возможностей устройства за счет введения в схему прототипа функциональных элементов, позволяющих определить оптимальное время начала и продолжительность подготовки средств системы к применению, а также вероятность безотказной работы к моменту окончания цикла применения. Устройство содержит блок памяти, три сумматора, четыре блока умножения, триггер, два блока нелинейностей, четыре вычитателя, датчик времени (генератор линейно изменяющегося напряжения), два блока деления, три элемента памяти, три вентиля, три компаратора и блок логарифмического преобразования. 5 ил.

Реферат

Изобретение относится к вычислительной технике, в частности к устройствам контроля, и может быть использовано в научных исследованиях и технике, где требуется находить оптимальное время подготовки средств системы, обеспечивающее максимум вероятности того, что каждое средство к началу применения по назначению будет работоспособно.

Известны устройства [2, 3, 4, 5, 6], позволяющие определять оптимальные программы обслуживания изделий и технических средств систем, но без учета плана применения этих изделий и систем по назначению.

Наиболее близким по технической сущности к заявляемому изобретению является устройство [7], содержащее блок памяти четыре блока умножения, шесть сумматоров, четыре блока нелинейности, четыре элемента задержки, блок сравнения, блок деления, два триггера, шесть вентилей, схему ИЛИ, три вычитателя, ждущий мультивибратор, четыре элемента памяти, два интегратора, компаратор и аттенюатор.

Недостатком технического решения [7] являются ограниченные функциональные и информативные возможности. Определение значений искомых величин осуществляется без учета плана применения обслуживаемых средств.

Целью заявляемого изобретения является расширение функциональных и информативных возможностей устройства. Цель достигается путем введения в схему прототипа ряда функциональных элементов, позволяющих определять оптимальное время начала и продолжительность подготовки средств системы к применению, а также вероятность безотказной работы к моменту окончания цикла применения.

Система включает в себя совокупность i = 1 , m ¯ средств, находящихся в связях, образующих целостность, единство. Примерами технических систем являются системы управления воздушным движением, системы подготовки и запуска космических аппаратов и другие.

Существует годовой план применения средств системы (рис.1а), включающий интервалы времени τрi задействования средств по назначению и интервалы τнj их простоя, j = 1 , n ¯ . На каждом интервале τнj осуществляется подготовка средств, обеспечивающая их готовность к применению на очередном интервале τpj. Количественные показатели сложности, надежности и ремонтопригодности средств различны, поэтому и оптимальные сроки их подготовки к применению разные. Слишком раннее начало подготовки сопряжено с тем, что обслуженные средства долгое время будут находиться в режиме ожидания применения. За это время в системе может произойти отказ, устранение которого потребует время, превышающее то, которое осталось до планового начала применения средств системы. Слишком позднее начало подготовки может не обеспечить ее завершение, в результате чего система не будет готова к применению в назначенное время.

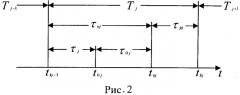

На рис.2 показан фрагмент плана применения средств Tj, j = 1 , n ¯ , отражающий один интервал времени τнj между временем tk(j-1) окончания предыдущего интервала Tj-1 применения и временем tнj начала очередного интервала τpj применения,

τ н j = t н j − t k ( j − 1 ) ( 1 )

Для каждого i-го средства системы на интервале τнj существует оптимальное время τ o i j * его подготовки к применению, обеспечивающее максимум вероятности того, что средство к заданному времени tнj будет готово к работе,

τ o i j * = τ н j − τ i j * ( 2 )

где τ i j * - оптимальная продолжительность между временем tk(j-1) и временем toij начала подготовки i-го средства к применению.

Готовность каждого средства обеспечит готовность системы в целом. Существуют системы, средствам которых соответствует экспоненциальный закон распределения времени безотказной работы, восстановления работоспособности в случае отказа, подготовки к применению с интенсивностями λi, µi, νi соответственно. Рассмотрим следующие возможные состояния каждого i-го средства в общем виде:

1 - средство работоспособно и подготавливается к применению;

2 - средство неисправно и ремонтируется;

3 - средство готово к применению.

Используя граф переходов, запишем в общем для каждого средства виде систему дифференциальных уравнений переходов:

d P 1 d t = − ( λ + ν ) P 1 ( t ) + μ P 2 ( t ) d P 2 d t = − μ P 2 ( t ) + λ P 1 ( t ) + λ P 3 ( t ) d P 3 d t = − λ P 3 ( t ) + ν P 1 ( t ) } ( 3 )

Решением системы уравнений (3) для Р3 при начальных условиях Р1(0)=P(t0), Р2(0)=1-P(t0), Р3(0)=0 будет:

P 3 ( t ) = μ ν ( λ + ν ) ( λ + μ ) + μ ν − P ( t 0 ) ( λ + μ ) ν ( ν − μ ) ( λ + μ ) e − ( λ + μ ) t + μ ν − P ( t 0 ) ( λ + μ ) ν ( ν − μ ) ( λ + ν ) e − ( λ + μ ) t ( 4 )

Дифференцируя P3(t) по t и приравнивая производную к нулю, определим оптимальное по критерию максимума вероятности P 3 ( τ о * ) значение времени t = τ о * готовности средства к применению (рис.3):

τ о * = [ ℓ т P ( t 0 ) ( λ + ν ) − μ P ( t 0 ) ( λ + μ ) − μ ] / ( ν − μ ) ( 5 )

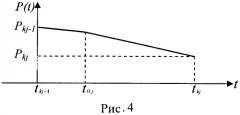

Отметим, что в момент времени tk(j-) (рис.4) вероятность безотказной работы i-го средства равна Pki(j-i). На интервале времени τij согласно [1] надежностный потенциал i-го средства расходуется с интенсивностью λ1i, а на интервале τoij - с интенсивностью λ2i>λ1i Поэтому величина Pi(toij) на интервале τij выражается так:

P i ( τ i j ) = P k i ( j − 1 ) e − λ 1 i ( τ н j − τ 0 i j ) ( 6 )

В связи с этим соотношение (5) для i-го средства приобретает следующий вид:

τ о i j * = [ ln P k i ( j − 1 ) ( k , i ) e − λ 1 i ( τ н j − τ о i j * ) ( λ 2 i + ν i ) − μ i P k i ( j − 1 ) e − λ 1 i ( τ н j − τ о i j * ) ( λ 2 i + ν i ) − μ i ] / ν i − μ i ( 7 )

Полученному значению τ о i j * соответствует согласно (2) оптимальное время τ i j * начала подготовки i-го средства к применению на j-ом интервале.

К началу применения средства вероятность его безотказной работы выражается следующим соотношением:

P i j ( τ н j ) = P k i ( j − 1 ) e − λ 1 i ( τ н j − τ о i j * ) e − λ 2 i τ о i j * , ( 8 )

а в момент окончания интервала τpj применения, то есть к моменту окончания времени Tj (рис.4), будет:

P k j ( T j ) = P i ( τ н j + τ р j ) = P k i ( j − 1 ) e − λ 1 i ( τ н j − τ о i j ) e − λ 2 i ( τ о i j * + τ р j ) ( 9 )

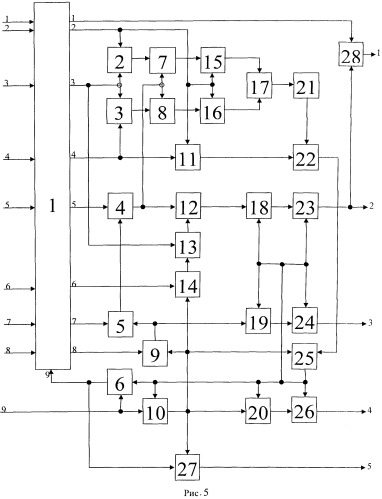

Предложенная математическая модель может быть реализована аппаратурно с помощью устройства, схема которого показана на рис.5.

Устройство содержит: блок памяти 1, сумматоры 2, 3, 14, блоки умножения 4, 7, 8, 12, триггер 6, блоки нелинейности 5, 13, вычитатели 9, 11, 15, 16, датчик времени 10 (генератор линейно изменяющегося напряжения), блоки деления 17, 22, элементы памяти 18, 19, 20, вентили 23, 24, 26, компараторы 25, 27, 28, блок логарифмического преобразования 21.

Рассмотрим один цикл работы устройства применительно к первому средству системы на j-том интервале, не указывая индекс i=1.

Перед началом работы устройства исходные данные P k j д о п , µ, λ2, Pk(j-1), τр, λ1, τн соответствующие первому средству системы, вводятся в блок памяти 1 через его входы с первого по восьмой, соответственно, являющиеся входами устройства. По сигналу «Пуск», поступающему с девятого входа устройства на первые входы триггера 6 и датчика времени 10, триггер 6 переключается в единичное состояние, обеспечивая этим поступление на выходы блока памяти 1 значений хранимых данных. Датчик времени 10 вырабатывает последовательно возрастающий сигнал, соответствующий значениям величины τoj, и передает его на первые входы первого 25 и второго 27 блоков сравнения, в третий элемент памяти 20, а так же на вторые входы первого вычитателя 9 и третьего сумматора 14. С восьмого выхода блока памяти 1 сигнал τнj поступает на первый вход первого вычитателя 9 и на второй вход второго блока сравнения 27. В блоке сравнения 27 осуществляется сравнение величин τнj и τoj. Если окажется, что τoj больше τнj, то с выхода блока сравнения 27 на пятый выход устройства передается сигнал, свидетельствующий о невозможности подготовить данное средство к применению на данном интервале τнj времени. В таком случае дальнейшая работа устройства не даст положительных результатов.

При тoj<τнj работа устройства продолжается. Сигнал, соответствующий разности τнj-τoj с выхода первого вычитателя 9 передается на первый вход второго элемента памяти 19 и на второй вход первого блока нелинейности 5. С седьмого выхода блока памяти 1 значение величины λ1 поступает на первый вход первого блока нелинейности 5, с выхода которого на второй вход первого блока умножения 4 передается значение величины e − λ 1 ( τ н j − τ о j ) . С пятого выхода блока памяти 1 значение величины рk(j-1) поступает на первых вход первого блока умножения 4, с выхода которого сигнал, соответствующий согласно (6) величине Р(τj), передается на первые входы второго 7, третьего 8 и четвертого 12 блоков умножения. С четвертого выхода блока памяти 1 значение величины v передается на вторые входы второго вычитателя 11 и второго сумматора 3, на первый вход которого, как и на первые входы первого сумматора 2 и второго блока нелинейности 13, с третьего выхода блока памяти 1 поступает значение величины λ2. В третьем сумматоре 1 формируется и передается на второй вход второго блока нелинейности 13 сигнал, соответствующий сумме τр+τо. В блоке нелинейности 13 вычисляется значение величины e − λ 2 ( τ р j − τ о j ) и передается на второй вход четвертого блока умножения 12. Выходной сигнал блока умножения 12, соответствующий согласно (9) значению величины Pk(Tj), передается в первый элемент памяти 18. Со второго выхода блока памяти 1 на второй вход первого сумматора 2 и на первые входы второго 11, третьего 15 и четвертого 16 вычитателей поступает значение величины µ. В первом сумматоре 2 формируется значение суммы λ2+µ и передается на второй вход второго блока умножения 7, в котором перемножается с величиной P(τj) и поступает на второй вход третьего вычитателя 15. Во втором сумматоре 3 формируется значение суммы λ2+ν и передается на второй вход третьего блока умножения 8, в котором перемножается с величиной P(τj) и поступает на второй вход четвертого вычитателя 16. Значение сигнала P(τj)·(λ2+µ)-µ с выхода третьего вычитателя 15 передается на первый вход первого блока деления 17, а значение сигнала P(τj)(λ2+ν)-µ с выхода четвертого вычитателя 16 поступает на второй вход первого блока деления 17. Значение сигнала [P(τj)(λ2+ν)-µ]/[P(τj)·(λ2+µ)-µ] с выхода первого блока деления 17 через блок логарифмического преобразования 21 поступит на второй вход второго блока деления 22. Значение сигнала (ν-µ) с выхода второго вычитателя 11 передается на первый вход второго блока деления 22. Результат деления, соответствующий согласно (7) вычисленному значению величины τoj, с выхода блока деления 22 поступит на второй вход первого компаратора 25. Это значение τoj сравнивается со значением, поступившим на первый вход компаратора 25 от датчика времени 10. При их равенстве на выходе компаратора 25 появляется управляющий сигнал, который передается на вторые входы датчика времени 10, триггера 6, первого 18, второго 19 и третьего 20 элементов памяти, первого 23, второго 24 и третьего 26 вентилей. В результате этого триггер 6 переводится в нулевое состояние, датчик времени выключается, вентили 23, 24, 26 открываются и с элементов памяти 18, 19, 20 считываются хранимые в них данные. При этом на второй выход устройства поступит вычисленное значение величины Pkj, а на третий и четвертый выходы - оптимальные значения τ j * и τ о j * соответственно. Значение Pkj поступит также на второй вход третьего компаратора 28, на первый вход которого с первого выхода блока памяти 1 передается допустимое значение P k j д о п данной величины. При выполнении условия P k j ≥ P k j д о п средство системы удовлетворяет требованию по надежности и может применяться по назначению. Если же окажется, что вычисленное значение Pkj будет меньше допустимого P k j д о п , то на выходе компаратора 28, являющегося первым выходом устройства, появится сигнал, означающий несоответствие данного средства требованию по надежности. На этом работа устройства в данном цикле заканчивается.

На каждый последующий цикл i = 2 , n ¯ работы устройства входные данные, кроме значений τpj и τнj вводимые в блок памяти 1, обновляются соответственно исследуемым средствам системы, а циклы вычисления значений искомых величин идентичны рассмотренному.

Полученные результаты определения значений величин τ i j * и τ о i j * для каждого средства системы i = 2 , m ¯ отражены на плане подготовки средств к применению (рис.1б).

Положительный эффект, который может быть получен от использования предлагаемого технического решения состоит в определении оптимальных значений времени начала и продолжительности подготовки средств системы в условиях существующего плана применения системы по назначению, а также в определении вероятности безотказной работы средств и соответствие ее предъявляемым требованиям, что особенно важно для средств обеспечения испытательных полетов самолетов, подготовки и запуска космических аппаратов, медицинского оборудования перед проведением операций и другого.

Путем m-кратного применения устройства определяются выходные данные всех средств системы. Отсутствие выходных сигналов на 1 и 5 выходах устройства означает, что система готова к применению, при этом вероятность ее безотказной работы выражается так: P c ( T j ) = ∏ i = 1 m P i ( T j ) . Полученный результат является основанием для принятия решения на применение системы на Tj интервале.

Схемы функциональных элементов устройства представлены в [8], в том числе:

- блок логарифмического преобразования - схема 5-2-4, стр.139;

- блок нелинейности - схема 3-4-2, стр.107;

- элемент памяти - схема 4-5-1, стр.124.

Источники информации

1. Седякин Н.М. Об одном физическом принципе теории надежности. - Известия АН СССР, ОТН, Техническая кибернетика, 1966, №3.

2. Гришин В.Д., Соколов Б.В., Иконникова А.В. Патент РФ №2429543. МПК G07C 3/08, G06F 11/30, G06F 17/00, 2011.

3. Гришин В.Д., Соколов Б.В., Петрова И.А. Патент РФ №2429542. МПК G07C 3/08, G05B 23/02, 2011.

4. Гришин В.Д., Зиновьев С. В., Соколов Б.В., Майданович О.В. Патент РФ №2452027. МПК G07C 3/08, 2012.

5. Соколов Б.В., Стародубов В.А., Гришин В.Д., Цивирко Е.Г. Решение о выдаче патента от 23.10.2012 по заявке №2011142589, МПК G07C 3/08, 2011.

6. Соколов Б.В., Гришин В.Д., Зеленцов В.А., Майданович О.В. Решение о выдаче патента от 29.11.2012 по заявке №2011146676, МПК G07C 3/08, 15.09.2011.

7. Соколов Б.В., Гришин В.Д., Зеленцов В.А., Цивирко Б.Г. Решение о выдаче патента от 30.08.2012 по заявке №2011146675, МПК G07C 3/08, 15.09.2011.

8. Тетельбаум И.М., Шнейдер Ю.Р. 400 схем для АВМ. - М.: Энергия, 1978.

Устройство для определения оптимального времени подготовки средств системы к применению, содержащее первый сумматор, второй сумматор, второй вход которого подключен к четвертому выходу блока памяти, второй, третий и четвертый блоки умножения, второй блок нелинейности, второй и третий вычитатели, четвертый вычитатель (эквивалент сумматора прототипа), выход которого соединен со вторым входом первого блока деления, первый элемент памяти, выход которого подключен к информационному входу первого вентиля, выход которого является вторым выходом устройства, третьим выходом которого является выход второго вентиля, информационный вход которого соединен с выходом второго элемента памяти, третий элемент памяти, выход которого подключен к информационному входу третьего вентиля, выход которого является четвертым выходом устройства, девятый вход которого соединен с первым входом триггера, второй вход которого подключен к выходу первого компаратора, а выход - к девятому входу блока памяти, входы которого с первого по восьмой являются одноименными входами устройства, седьмой выход блока памяти соединен с первым входом первого блока нелинейности, второй вход которого связан с выходом первого вычитателя, а выход подключен ко второму входу первого блока умножения, выход которого связан с первым входом третьего блока умножения, шестой выход блока памяти соединен с первым входом третьего сумматора, отличающееся тем, что в него введены датчик времени (генератор линейно изменяющегося напряжения), блок логарифмического преобразования, второй блок деления, второй и третий компараторы, причем первым выходом устройства является выход третьего компаратора, второй вход которого соединен с выходом первого вентиля, а первый вход - с первым выходом блока памяти, первый выход которого подключен ко второму входу первого сумматора, к первым входам второго и третьего вычитателей, а также ко второму входу четвертого вычитателя, первый вход которого соединен с выходом третьего блока умножения, второй вход которого связан с выходом второго сумматора, второй вход которого соединен со вторым входом второго вычитателя, а первый вход вместе с первым входом первого сумматора подключен к третьему выходу блока памяти и к первому входу второго блока нелинейности, второй вход которого соединен с выходом третьего сумматора, а выход подключен ко второму входу четвертого блока умножения, выход которого соединен с информационным входом первого элемента памяти, а первый вход - с выходом первого блока умножения, первый вход которого подключен к пятому выходу блока памяти, восьмой выход которого соединен с первым входом первого вычитателя и со вторым входом второго компаратора, выход которого является пятым выходом устройства, девятый вход которого соединен с первым входом датчика времени, выход которого подключен к второму входу третьего сумматора, к первым входам первого и второго компараторов, к информационному входу третьего элемента памяти и ко второму входу первого вычитателя, выход которого соединен с информационным входом второго элемента памяти, управляющий вход которого вместе с управляющими входами первого и третьего элементов памяти, первого, второго и третьего вентилей, а также со вторым входом датчика времени подключен к выходу первого компаратора, второй вход которого соединен с выходом второго блока деления, первый вход которого связан с выходом второго вычитателя, а второй вход - с выходом блока логарифмического преобразования, вход которого подключен к выходу первого блока деления, первый вход которого соединен с выходом третьего вычитателя, второй вход которого связан с выходом второго блока умножения, второй вход которого подключен к выходу первого сумматора, а первый вход - к выходу первого блока умножения.