Способ и устройство счета импульсов

Иллюстрации

Показать всеГруппа изобретений относится к цифровой вычислительной технике и устройствам цифровой автоматике. Техническим результатом является повышение быстродействия выполнения операции счета импульсов. Каждый десятичный разряд устройства содержит четыре двоичных разряда, каждый из которых содержит один RS-триггер, три логических элементов И, два логических элемента ИЛИ, три логических элемента НЕ. Также каждый десятичный разряд содержит четыре логических элемента И, один логический элемент ИЛИ, вход общей установки триггеров тетрад в нуль, вход счетных импульсов из младшей тетрады, выход счетных импульсов в старшую тетраду. 2 н.п. ф-лы, 2 ил.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и устройствах автоматики.

Известны способы и устройства счета импульсов (см., например И.Н. Букреев, Б.М. Мансуров и В.И. Горячев. Микроэлектронные средства цифровых устройств. 1973, Сов. радио, стр. 143, рис 5.7). Кодирование информации в указанном счетчике выполняется в коде 8 4 2 1, каждый разряд счетчика содержит два RS-триггера и логические элементы (ЛЭ) И, НЕ. Недостатком этого счетчика является наличие двух RS-триггеров (Tr) в разряде и последовательное распространение сигнала переноса (СП), максимальная величина которого, при прочих равных условиях, зависит от числа двоичных разрядов счетчика. Известны счетчики содержащие один RS-триггер в каждом разряде и выполняющие широкий перечень ЭО, например, счетчики импульсов, выполненные по патентам RU 2284653 C2, RU 2284654 C2, но быстродействие этих счетчиков также зависит от числа двоичных разрядов. Ближайшим прототипом предлагаемого устройства является счетчик, выполненный по патенту RU 2308801 C. Прототип содержит в каждом разряде один RS-триггер и несколько снижает максимальное время распространения СП, но это достигается за счет дополнительных затрат оборудования для построения цепи переноса.

Целью изобретения является повышение быстродействия работы счетчика за счет исключения временной задержки при формировании СП при счете импульсов в тетрадах двоично-десятичного счетчика и снижение аппаратурных затрат. Для этого предложен способ счета импульсов, отличающийся тем, что кодирование десятичных цифр от нуля до девяти представляют кодами четырех триггеров 0000, 0001, 0010, 0100, 1000, 1001, 1010, 1100, 1101 и 1110, при этом в случае A 1 ¯ ⋅ A 2 ¯ ⋅ A 3 ¯ = 1.. … ( 1 ) по приходу счетного импульса (СИ) в триггер первого разряда заносят код „1", по следующему СИ сдвигают код принятой единицы в Tr второго разряда, а Tr 1 первого разряда устанавливается в „0". Аналогично выполняют сдвиг „1" на один разряд влево по C2-C4. При A4=1 значение триггера сохраняют до прихода СИ 10. По СИ 5 заносят „1" в Tr первого разряда согласно соотношению (1). Счетные импульсы СИ 6 и СИ 7 сдвигают код „1" в Tr третьего разряда, при A3=1 значение триггера сохраняют до прихода СИ 10. Десятым СИ устанавливают все Tr тетрады в „0" и вырабатывают СП в старшую тетраду. Это позволяет исключить время распространения СП в пределах тетрады, что повышает быстродействие выполнения счета импульсов. Также предложено устройство счета импульсов, отличающееся тем, что каждый двоичный разряд счетчика импульсов построен на основе одного RS-триггера, трех элементов И, двух элементов ИЛИ и трех элементов НЕ. Кроме того, каждая тетрада содержит схему формирования СП, выполненную на двух элементах И, схему управления приемом „1" в Tr первого разряда, выполненную на двух элементах И и одном элементе ИЛИ, вход общей установки триггеров тетрад в „0", вход СИ из младшей тетрады, выход СИ из i-й тетрады в старшую тетраду. Предложенное построение счетчика обеспечивает снижение затрат оборудования и повышает быстродействие счета импульсов.

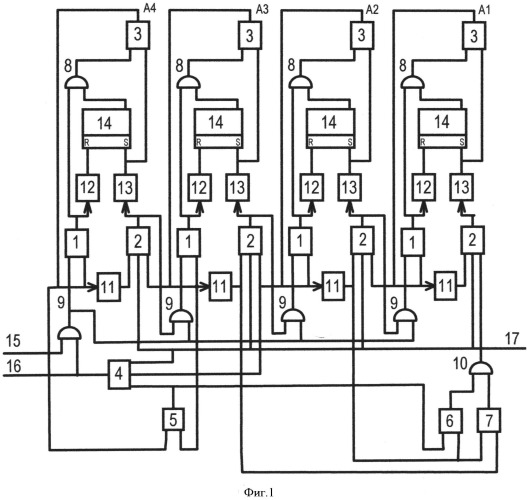

Для пояснения работы предложенного устройства на фиг.1 приведена функциональная схема одной тетрады счетчика импульсов. На схеме приняты следующие обозначения: элементы И 1-7, элементы ИЛИ 8-10, элементы НЕ 11-13; RS-триггер (Tr) 14, вход общей установки „0" триггеров тетрад 15, вход счетных импульсов из младшей тетрады 17, выход счетных импульсов в старшую тетраду 16. На фиг.2 приведена временная диаграмма работы двух тетрад счетчика.

Предлагаемое устройство осуществляется следующим образом. В каждом двоичном разряде счетчика выходы И 1, 2 через НЕ 12, 13 соединены с нулевым и единичным входами Tr 14, выход И 1 и единичный выход Tr 14 через ИЛИ 8 соединены с первым входом И 3, второй вход которого подключен к выходу НЕ 13. Выход И 3 подключен к первому входу к первого И 1 и к входу НЕ 11 i-го разряда и к третьему входу И2 i+1-го разряда. Выход ПЕН в первом разряде соединен с первым входом И 2, второй и третий входы которого соединены с входом 17 и с выходом ИЛИ 10. Выход ИЛИ 9 соединен с первым входом И 1. Первый вход ИЛИ 9 первого-третьего разрядов соединен с выходом И 2 второго-четвертого разрядов, вторые входы ИЛИ 9 первого-третьего разряда соединены между собой и подключены к выходу ИЛИ 9 и входу И 1 четвертого разряда. Первый вход ИЛИ 9 четвертого разряда соединен с входом 15, второй вход упомянутого элемента ИЛИ подключен к выходу И4. В каждой тетраде разрядов первый-третий входы И 4 соединены с входом 17, с выходом ИЗ второго разряда и выходом И 5 соответственно. Выход И 4 соединен с входом СП в старшую тетраду 16. Первый и второй входы И 5 соединены с выходами И 3 четвертого и третьего разрядов. Первый и второй входы И 6 подключены к выходу И 5 и НЕ 11 второго разряда. Первый и второй входы И 7 соединены с выходами НЕ 11 третьего и второго разрядов. Выходы И 6, 7 подключены к входу ИЛИ 10. Вход СП 17 из младшей тетрады соединен со вторыми входами И 2 первого-четвертого разрядов. Рассмотрим работу устройства при выполнении операции счета импульсов. До начала операции триггеры 14 всех тетрад установлены в „0". Импульс установки нуля проходит по цепи: вход 15, ИЛИ 9 четвертого разряда, ИЛИ 9 первого-третьего разрядов, И 1, НЕ 12 и нулевой вход Tr 14 всех тетрад. Первый счетный импульс, поступивший по входу 17, устанавливает Tr 14 в первом разряде в „1" при условии A 1 ¯ ⋅ A 2 ¯ ⋅ A 3 ¯ = 1.. … ( 1 ) . (Здесь A 3 ¯ , A 2 ¯ и A 1 ¯ - инверсные значения Tr 14.), второй СИ установит Tr 14 второго разряда в „1". Сигнал проходит по цепи элементов И 2, НЕ 13 и поступит на единичный вход Tr 14. При этом нулевое значение сигнала с выхода НЕ 13 запрещает работу И 3 второго разряда, чем обеспечивает задержку сигнала с И 3 на время длительности СИ 2. Одновременно сигнал с выхода И 2 через ИЛИ 9, И 1, НЕ 12 поступит на нулевой вход Tr 14 первого разряда и установит упомянутый триггер в „0". Таким образом код „1", хранящийся в Tr 14 первого разряда, будет сдвинут на один разряд влево, т.е. в тетраде будет храниться код 0010, что соответствует числу 2. Третий СИ сдвинет код „1" из второго разряда в третий разряд. Четвертый СИ сдвинет код „1" из третьего разряда в четвертый разряд. Код „1" в четвертом разряде будет сохраняться до конца счета первых десяти СИ в рассматриваемой тетраде. После окончания четвертого СИ снова будет выработан управляющий потенциал по условию (1). Пятый СИ занесет в Tr 14 первого разряда код „1", шестой СИ сдвинет код „1" в Tr 14 второго разряда, седьмой СИ сдвигает код „1" в Tr 14 третьего разряда. Код „1" в третьем разряде будет храниться до конца счета первых десяти СИ. После окончания седьмого СИ будет сформирован управляющий потенциал A 4 ⋅ A 3 ⋅ A 2 ¯ ⋅ A 1 ¯ = 1 … … ( 2 ) . Упомянутый потенциал будет сформирован на выходы И 5, 6, ИЛИ 10, который разрешит прохождение восьмого СИ по цепи элементов И 2, НЕ 13 на единичный вход Tr 14 первого разряда. Девятый СИ сдвинет код „1" из первого разряда во второй. После окончания девятого СИ в тетраде будет сформирован код 1110, что соответствует числу 9. Десятый СИ выработает СП в старшую тетраду счетчика, при этом С П = A 4 ⋅ A 3 ⋅ A 2 ⋅ С И 10 = 1 … … ( 3 ) . Сигнал переноса в старшую тетраду вырабатывается на выход И 4 и по выходу 16 поступает в старшую тетраду на вход 17 и на вход ИЛИ 9 четвертого разряда рассматриваемой тетрады. Сигнал с выхода элемента ИЛИ 9 по цепи элементов И 1, НЕ 12 поступит на первый вход Tr 14 четвертого разряда и одновременно через элементы ИЛИ 9, И 1, НЕ 12 на нулевые входы Tr 14 триггеров третьего-первого разрядов. Таким образом устройство выполняет счет импульсов в двоично-десятичном коде, каждый разряд которого построен на основе одного RS-триггера, ЛЭ И, ИЛИ, НЕ, при этом исключена схема сквозного переноса в разрядах каждой тетрады, что позволяет повысить быстродействие работы и снизить аппаратурные затраты.

1. Способ счета импульсов, отличающийся тем, что каждую десятичную цифру одного разряда представляют четырьмя двоичными разрядами, при этом десятичные цифры от нуля до четырех представляют двоичными кодами 0000, 0001, 0010, 0100 и 1000 соответственно, цифры от пяти до девяти представляют двоичными кодами 1001, 1010, 1100, 1101 и 1110 соответственно, выполнение счета импульсов от „0" до „9" производят путем добавления „1" к коду числа, хранящемуся в первом-четвертом триггерах тетрады A1, A2, A3 и A4, при этом добавление „1" к коду тетрады осуществляют путем занесения „1" в А1 или сдвига „1" на один разряд в сторону старших двоичных разрядов, первым счетным импульсом СИ 1 при нулевых значениях A1, A2 и A3, т.е. , устанавливают A1 в „1", вторым счетным импульсом СИ 2 устанавливают A2 в „1" и A1 устанавливают в „0", третьим счетным импульсом СИ 3 устанавливают A3 в „1", а A2 в „0", четвертым счетным импульсом СИ 4 устанавливают A4 в „1", а A3 в „0", при этом код A4 сохраняют до конца счета в рассматриваемой тетраде, пятым СИ 5 при принимают код „1" в A1, шестым счетным импульсом СИ 6 устанавливают A2 в „1", а A1 в „0", седьмым счетным импульсом СИ 7 устанавливают A3 в „1", а A2 в „0", при этом код A3 сохраняют до конца счета в рассматриваемой тетраде, при условии по СИ 8 разрешают запись кода „1" в A1, по СИ 9 устанавливают A2 в „1" и A1 в „0", по десятому СИ 10 формируют сигнал переноса СП в старшую тетраду, при этом СП=A4·A3·А2·СИ 10=1, и устанавливают все триггеры тетрады в „0", подавая СП по цепи вторых элементов ИЛИ, первых элементов И, вторых элементов НЕ на нулевые входы каждого RS триггера тетрады.

2. Устройство счета импульсов, выполненное на логических элементах ЛЭ И, ИЛИ, НЕ, содержащее в каждом двоичном разряде один RS-триггер, первый-третий элементы И, первый элемент ИЛИ, первый-третий элементы НЕ, при этом первый элемент И, через второй элемент НЕ соединен с нулевым входом RS-триггера, второй элемент И через третий элемент НЕ соединен с единичным входом RS-триггера, выход первого элемента И и единичный выход RS-триггера через первый элемент ИЛИ соединены с первым входом третьего элемента И, второй вход которого подключен к выходу третьего элемента НЕ, выход третьего элемента И соединен с первым входом первого элемента И и с входом первого элемента НЕ, выход которого соединен с первым входом второго элемента И, отличающееся тем, что в каждый двоичный разряд тетрады введен второй элемент ИЛИ, первый вход которого в первом-третьем разрядах соединен с выходом второго элемента И четвертого-второго разряда соответственно, выход упомянутого элемента ИЛИ подключен к второму входу первого элемента И соответствующего разряда, кроме того, выход второго элемента ИЛИ четвертого разряда соединен со вторыми входами вторых элементов ИЛИ третьего-первого разрядов тетрады, первый и второй входы второго элемента ИЛИ четвертого разряда подключены к первому входу общей установки триггеров тетрад в „0" и к выходу четвертого элемента И, выходы третьих элементов И первого-третьего разрядов тетрады соединены с третьеми входами вторых элементов И старших разрядов соответственно; вторые входы вторых элементов И первого-четвертого разрядов тетрады подключены к второму входу счетных импульсов СИ из младшей тетрады, первый, второй и третий входы четвертого элемента И, выход которого является сигналом переноса в старшую тетраду, соединены с входом счетных импульсов из младшего разряда, выходом третьего элемента И второго разряда и с выходом пятого элемента И соответственно, входы пятого элемента И подключены к выходам третьих элементов И четвертого и третьего разрядов, выход пятого элемента И соединен с первым входом шестого элемента И, второй вход которого соединен с выходом первого элемента НЕ второго разряда, входы седьмого элемента И связаны с выходами первых элементов НЕ второго и третьего разрядов, выходы шестого и седьмого элементов И через третий элемент ИЛИ соединены с третьим входом второго элемента И первого разряда.