Способ и устройство вычитания единиц

Иллюстрации

Показать всеИзобретение относится к цифровой вычислительной технике и устройствам цифровой автоматики. Технический результат заключается в сокращении времени формирования импульса вычитания и импульса заема при построении схемы определения нулевых назначений триггеров всех тетрад. Технический результат достигается за счет того, что каждый десятичный разряд устройства содержит четыре двоичных разряда, каждый из которых содержит один RS-триггер, три логических элемента И, два логических элемента ИЛИ, три логических элемента НЕ, каждый десятичный разряд содержит дополнительно три логических элемента И, четыре информационных входа, первый вход импульсов вычитания единиц, выход заема единицы из старшей тетрады. Кроме того, первый десятичный разряд содержит два элемента И и один элемент НЕ. 2 н.п. ф-лы, 1 ил.

Реферат

Описание изобретения.

Изобретение относится к области вычислительной техники и может быть использовано в устройствах управления различными технологическими процессами.

Известны способы и устройства счета и вычитания импульсов (см., например, И.Н. Букреев, Б.М. Мансуров и В.И. Горячев. Микроэлектронные средства цифровых устройств. 1973 г. Сов. Радио, стр. 135-160).

Общими признаками известных устройств являются, как правило, кодирование информации в коде 8, 4, 2, 1, для построения одного разряда устройства требуется два RS-триггера, формирование сигнала переноса (СП) ведется последовательно, т.е. упомянутый сигнал проходит через каждый разряд, в основном, последовательно, при этом максимальная временная задержка СП равна Т=n×t (n - число разрядов, t - задержка сигнала на одном логическом элементе И (ИЛИ).

Известны способы снижения этого показателя, но за счет увеличения аппаратурных затрат. Известно также устройство счета и вычитания импульсов, построенное на основе одного RS-триггера, логических элементов И, ИЛИ, НЕ, например счетчики RU 2269199, RU 2308801, RU 2273951, но принцип последовательного формирования распространения СП, в основном, сохраняется.

Наиболее близким, принятым за прототип, является реверсивный счетчик импульсов по патенту RU 2273951. Его каждый разряд построен на основе одного RS-триггера и логических элементов И, ИЛИ, НЕ, выполняет как счет импульсов, так и их вычитание.

К недостаткам прототипа следует отнести последовательное формирование СП. В предложенных способе и устройстве (СУ) этот недостаток устранен за счет исключения из оборудования каждых четырех двоичных разрядов (тетрады) четырех элементов И формирования СП.

Целью изобретения является повышение быстродействия за счет снижения времени формирования СП и сокращения оборудования при построении схемы определения нулевых значений всех триггеров устройства.

Для этого предложен способ кодирования двоично-десятичных чисел в кодах 4, 3, 2, 1, т.е. «вес» единицы каждого разряда тетрады равен цифре, совпадающей с порядковым номером разряда в тетраде, а двоично-десятичная цифра, хранящаяся в тетраде, равна сумме этих единиц. Также способ вычитания единиц предусматривает замену выполнения операции вычитания выполнением операции сдвига младших единиц кода на один двоичный разряд вправо при поступлении в устройство каждого импульса вычитания (ИВ) единиц. В случае вычитания всех единиц из первой тетрады, формируют импульс заема (ИЗ) единицы из второй тетрады, а во второй-четвертый разряды первой тетрады заносят код девяти единиц, т.е. в первую тетраду заносят цифру «9». После вычитания кодов единиц всех тетрад уменьшаемого операцию заканчивают.

Также предложено устройство вычитания единиц уменьшаемого, хранящихся в триггерных тетрадах, содержащее в каждом двоичном разряде три элемента И, один элемент ИЛИ, три элемента НЕ и один RS-триггер, отличающееся тем, что в каждый разряд введен второй элемент ИЛИ, введена схема определения нулевых значений триггеров каждой тетрады и нулевых значений всех тетрад устройства.

Предлагаемое устройство обеспечивает сокращение времени формирования ИВ, ИЗ и затрат оборудования при построении схемы определения нулевых значений триггеров всех тетрад.

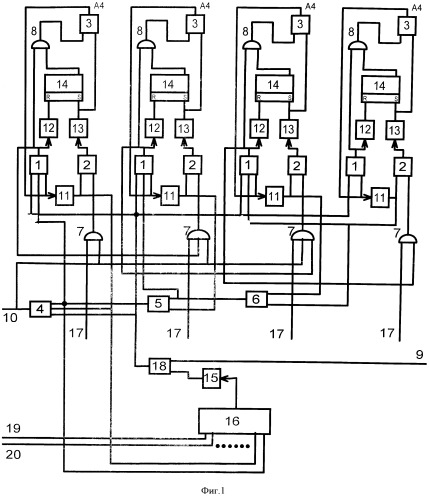

Для пояснения работы устройства на фиг. 1 приведена функциональная схема первой тетрады триггеров устройства.

На схеме приняты следующие обозначения: элементы И1-6, 16, 18 элементы ИЛИ7, 8, элементы НЕ11-13, 15, RS-триггер (Тг) 14, первый вход импульсов вычитания единиц 9, выход импульса заема единицы из второй тетрады 10, выходы нулевых значений 1-3 и четвертого разрядов Тг каждой тетрады с входами на И4-6, 19, 20.

Предлагаемое устройство осуществляется следующим образом.

В каждом двоичном разряде устройства выходы И1, 2 через НЕ12, 13 соединены с нулевым и единичным входами Тг14. Выход И1 и единичный выход Тг14 через ИЛИ8 соединены с первым входом ИЗ, второй вход которого подключен к выходу НЕ13. Выход И3 соединен с третьим входом И1 и с входом НЕ11, выход которого подключен к первому входу И2. В каждой тетраде выходы ИЛИ7 соединены со вторыми входами И2. Первые входы ИЛИ7 во втором-четвертом разрядах соединены с выходом И4. Третьи входы ИЛИ7 соединены с информационными входами 17, а вторые входы ИЛИ7 второго и третьего разрядов подключены к выходам элементов И1 третьего и четвертого разрядов. Выход 10 первой тетрады соединен с первыми входами И1, И4 второй тетрады, выход НЕ11 первого разряда соединен со вторым входом И1 второго разряда и с первым входом И6, второй вход И6 соединен с выходом НЕ11 второго разряда, выход И6 подключен к вторым входам И5 и И1 третьего разряда. Выход И5 соединен со вторыми входами И4 и И1 четвертого разряда. Первый вход И4 связан с выходом НЕ11 четвертого разряда, третий вход И4 соединен с выходом И18, и с первыми входами И1 триггеров всех разрядов тетрады. Второй и первый входы И4 соединены с первым и вторым входами И16, аналогичные связи с И16 имеют все тетрады устройства за счет связей 19 и 20. Выход И16 через НЕ15 соединен с вторым входом И18, первый вход которого соединен с первым входом ИВ9.

Рассмотрим работу устройства при выполнении операции вычитания единиц. Операция выполняется путем выполнения элементарных вычислительных операций:

1. Прием уменьшаемого в Тг14. Сигнал приема проходит по цепи элементов ИЛИ17, 7, И2, НЕ13 на единичный вход Тг14.

2. До прихода ИВ в каждой тетраде формируют нулевой потенциал триггеров тетрады ("0"ПТ). " 0 " П Т = А 4 ¯ × А 3 ¯ × А 2 ¯ × А 1 ¯ = 1 . Или "0"ПТ≠1.

3. После прихода первого ИВ при "0"ПТ=1 импульс вычитания единиц по цепи вход 9, И18, поступает на входы И1 всех разрядов и на И4, т.к. тетрада не содержит единичных значений Тг14, то на выходе И4 будет сформирован импульс заема единицы из второй тетрады, т.е. из второй тетрады будет вычтена единица, а в триггеры первой тетрады будет занесен код единиц в третий-четвертый разряды, что соответствует цифре "9" (1110), принятой в первую тетраду. Импульс занесения "9" пройдет по цепи И4, ИЛИ7, единичные входы Тг14 второго-четвертого разрядов.

4. После окончания первого ИВ и переключения Тг4, 3, 2 будет формироваться новый нулевой потенциал первой тетрады, равный A 1 ¯ = 1 . Одновременно будет подготовлен к работе И1 по сдвигу А2 вправо на один разряд. Второй ИВ поступит на первые входы И1 А4, A3, А2 и А1, выработает импульс сдвига с выхода И1 А2. установит его в "0" и по цепи элементов ИЛИ7, И2, НЕ13 первого разряда поступит на единичный вход Тг14 и установит его в единицу. При этом сигнал с выхода ИЗ А1 будет задержан во времени на время длительности ИВ. Таким образом, из "9" будет вычтена одна единица, и первая тетрада будет хранить код "8" (1101). Заметим, что триггеры А4 и A3 сохранят свое единичное состояние, т.к. потенциалы с выходов И6, 5 будут равны "0".

5. Третий ИВ поступит на первый вход И1 А1 и установит его в "0". После чего на И6 сформируется ВП, который поступит на второй вход И1 A3.

6. Четвертый ИВ по цепи элементов И1, НЕ12 поступит на нулевой вход Тг14 третьего разряда и установит его в "0". Одновременно импульс с И1 третьего разряда по цепи элементов И7, И2, НЕ13 поступит на единичный вход Тг14 второго разряда и установит его в "1". В тетраде будет храниться код 1010 (цифра 6).

7. Пятый ИВ сдвинет код 1 из второго разряда в первый разряд. В тетраде будет храниться код 1001 (цифра 5).

8. Шестой ИВ установит Tг14 первого разряда в "0" 1000 (цифра 5).

9. Седьмой ИВ сдвинет код четвертого разряда в третий разряд 0100 (число 3).

10. Восьмой ИВ сдвинет код третьего разряда во второй разряд 0010 (число 2).

11. Девятый ИВ сдвинет код второго разряда в первый разряд.

12. Десятый ИВ установит код первого разряда в "0", таким образом, на каждый ИВ из первой тетрады устройства вычитается одна единица. Предлагаемый способ и устройство не требуют в тетраде оборудования для формирования сквозного переноса, при этом исключаются временные задержки сигнала переноса и, при прочих равных условиях, повышается быстродействие работы устройства. Кроме того, предложенное построение схемы определения нулевых кодов всех триггеров обеспечивает экономию числа диодов и сокращение информационных связей в два раза, исключается оборудование и временные задержки сигнала переноса в каждой тетраде устройства.

1. Способ вычитания единиц, в котором каждая десятичная цифра представлена в двоично-десятичном коде и хранится в четырехразрядном триггерном регистре или в одной тетраде, отличающийся тем, что единичным состояниям триггеров первого-четвертого разрядов присваивают значение десятичных цифр 4, 3, 2, 1 соответственно далее А4, A3, А2, А1, при этом десятичные цифры от нуля до четырех представляют двоично-десятичными кодами 0000, 0001, 0010, 0100, 1000 соответственно, цифры от пяти до девяти представляют двоично-десятичными кодами 1001, 1010, 1100, 1101, 1110 соответственно, вычитание единиц из тетрады сводят к последовательным сдвигам младшей единицы кода на один разряд вправо по каждому импульсу вычитания, поступающему по первому входу импульсов вычитания ИВ, при этом код единиц старших разрядов не сдвигают до тех пор, пока единицы младших разрядов не будут сдвинуты из самого младшего разряда тетрады, при поступлении ИВ на первый вход управления, если тетрада хранит код 1000, то первый-четвертый ИВ будут выполнять сдвиг А4 последовательно в A3, А2, А1 разряды, четвертый ИВ сдвинет код единицы А1 за пределы разрядов тетрады, пятый ИВ при , , , выработает на выходе четвертого элемента И сигнал, который поступает во вторую тетраду и выполняет сдвиг одной единицы этой тетрады вправо, одновременно этот же импульс, проходя по вторым элементам второго-четвертого разрядов, установит триггеры в «1», т.е. введет в первую тетраду код 1110, т.е. число «9», в том случае, если во всех старших тетрадах хранится код нулей, то дешифратор определения нулевых значений тетрад, построенный на многоходовом восьмом элементе И выработает сигнал окончания операции вычитания, который через четвертый элемент НЕ поступит на второй вход седьмого элемента И и запретит поступление ИВ на входы первых элементов И каждого разряда и третий вход четвертого элемента И, на этом операцию вычитания единиц заканчивают.

2. Устройство вычитания единиц, содержащее в каждом двоичном разряде один RS-триттер, логические элементы И, ИЛИ, НЕ, при этом выходы первого и второго элементов И через второй и третий элементы НЕ соединены с нулевым и единичным входами RS-триггера, выход первого элемента И подключен к входу первого элемента ИЛИ, второй вход которого соединен с единичным выходом RS-триггера, выход первого элемента ИЛИ соединен с первым входом третьего элемента И, второй вход которого подключен к выходу третьего элемента НЕ, выход третьего элемента И является прямым выходом триггера i-го разряда Ai, сигнал с которого задержан во времени на время длительности импульса вычитания единицы и соединен с первым входом первого элемента И и с входом первого элемента НЕ, выход которого является инверсным выходом триггера Ai и соединен с первым входом второго элемента И, отличающееся тем, что в каждый двоичный разряд устройства введен второй элемент ИЛИ, выход которого подключен ко второму входу второго элемента И, вторые входы вторых элементов ИЛИ первого-третьего разрядов соединены с выходами первых элементов И второго-четвертого разрядов соответственно, третьи входы вторых элементов ИЛИ всех разрядов подключены к информационным входам соответствующих двоичных разрядов, первые входы элементов ИЛИ второго-четвертого разрядов подключены к выходу четвертого элемента И, в каждую тетраду двоичных разрядов введены четвертый-шестой элементы И, при этом первый вход шестого элемента И соединен с выходом первого элемента НЕ первого разряда и со вторым входом первого элемента И второго разряда, второй вход шестого элемента И подключен к выходу первого элемента НЕ второго разряда, выход шестого элемента И соединен со вторым входом пятого элемента И и вторым входом первого элемента И третьего разряда, второй вход шестого элемента И подключен к выходу первого элемента НЕ третьего разряда, выход пятого элемента И соединен со вторыми входами четвертого элемента И и первого элемента И четвертого разряда, первый вход четвертого элемента И соединен с выходом первого элемента НЕ четвертого разряда, третий вход упомянутого элемента И подключен к выходу седьмого элемента И и к первым входам первых элементов И первого-четвертого разрядов тетрады, выход четвертого элемента И первой тетрады является импульсом заема ИЗ единицы из второй тетрады и соединен с первым входом первых элементов И всех разрядов второй тетрады и третьим входом четвертого элемента И этой же тетрады, в первую тетраду также введены седьмой и восьмой элементы И, четвертый элемент НЕ, выход которого подключен к первому входу седьмого элемента И, второй вход которого связан с первым входом импульсов вычитания единиц, выход четвертого элемента НЕ соединен со входом восьмого элемента И, первый вход восьмого элемента И связан с выходом пятого элемента И, второй вход упомянутого элемента подключен к первому выходу первого элемента НЕ четвертого разряда, все остальные тетрады устройства имеют аналогичные связи с выходами восьмого элемента И, который является многоходовым элементом И определения нулевых значений триггеров всех тетрад.