Мультиплексирующий цифровой коррелятор

Иллюстрации

Показать всеИзобретение относится к технике цифровой связи и может быть использовано для синхронизации канала управления динамического мультиплексора с временным или кодовым разделением каналов. Техническим результатом является сокращение интервала времени входа в синхронизм канала управления динамического мультиплексора с временным или кодовым разделением каналов за счет параллельного обнаружения команд канала управления, а именно синхрослова, команд включения и выключения каналов, команд активности каналов, при динамическом изменении длины цикла синхронизации канала управления. Устройство содержит схемы ИЛИ, триггер, регистры, регистры сдвига, генератор тактовой частоты, схемы сложения по модулю два, программируемый счетчик, контроллер, счетчики. 2 ил.

Реферат

Изобретение относится к технике цифровой связи и может быть использовано для синхронизации канала управления динамического мультиплексора с временным или кодовым разделением каналов.

Известен переменный коррелятор (патент RU №02111538, МПК6 G06G 7/19), который обеспечивает повышение эффективности обработки для системы связи с растянутым диапазоном частот за счет управляемого изменения длины корреляции, устройство содержит средство управления длиной корреляции для изменения предварительно установленной длины корреляции, при этом средство накопления выполнено с возможностью накопления смешанных данных до числа, соответствующего установленной длине корреляции.

Недостатком известного устройства является невозможность отслеживать одновременно четыре команды канала управления динамического мультиплексора с временным или кодовым разделением каналов, а именно синхрослово, команду включения канала, команду выключения канала, команду активности канала, что определяет достаточно длительный интервал времени вхождения в синхронизм.

Известен коррелятор цифровой последовательности (патент США №3598979, MUK6 G06G 7/19), позволяющий для цифровой последовательности длины n, записанной в один регистр, произвести сравнение с цифровой последовательностью той же длины, записанной в другой регистр, цифровые последовательности сравниваются поэлементно.

Недостатком известного устройства является отсутствие возможности отслеживать одновременно несколько команд управления динамического мультиплексора с временным или кодовым разделением каналов, что определяет достаточно длительный интервал времени вхождения в синхронизм.

Наиболее близким по технической сущности к заявляемому изобретению является выбранный в качестве прототипа мультиплексирующий цифровой коррелятор (патент США №4660164, МПК6 G06F 15/336), который позволяет множеству корреляторов, работающих параллельно, производить одновременное сравнение и формировать общее решение корреляции для цифровой последовательной передачи данных в отношении исходных данных.

Недостатком известного устройства является невозможность отслеживать одновременно команды канала управления, имеющие переменную длину, что определяет достаточно длительный интервал времени вхождения в синхронизм.

Целью изобретения является сокращение интервала времени входа в синхронизм канала управления динамического мультиплексора с временным или кодовым разделением каналов за счет параллельного обнаружения команд канала управления, а именно синхрослова, команд включения и выключения каналов, команд активности каналов при динамическом изменении длины цикла синхронизации канала управления.

Цель достигается тем, что в известное устройство, содержащее генератор тактовой частоты, первый регистр сдвига, второй регистр сдвига, третий регистр сдвига и четвертый регистр сдвига, согласно изобретению введены первая схема ИЛИ, вторая схема ИЛИ, третья схема ИЛИ, четвертая схема ИЛИ, триггер, первый регистр, второй регистр, третий регистр, четвертый регистр, первая схема сложения по модулю два, вторая схема сложения по модулю два, третья схема сложения по модулю два, четвертая схема сложения по модулю два, программируемый счетчик, контроллер, пятая схема ИЛИ, шестая схема ИЛИ, седьмая схема ИЛИ, восьмая схема ИЛИ, первый счетчик, второй счетчик, третий счетчик, четвертый счетчик, причем первым входом устройства в целом является первый вход триггера, вторым входом устройства в целом является второй вход триггера, третьим входом устройства в целом является второй вход генератора тактовой частоты, четвертым входом устройства в целом является шестой вход контроллера, выходом устройства в целом является четвертый выход контроллера, при этом первый выход триггера подключен к первому входу первой схемы сложения по модулю два, второй выход триггера подключен к первому входу второй схемы сложения по модулю два, третий выход триггера подключен к первому входу третьей схемы сложения по модулю два, четвертый выход триггера подключен к первому входу четвертой схемы сложения по модулю два, причем ко второму входу первой схемы сложения по модулю два подсоединен выход первого регистра сдвига, ко второму входу второй схемы сложения по модулю два подсоединен выход второго регистра сдвига, ко второму входу третьей схемы сложения по модулю два подсоединен выход третьего регистра сдвига, ко второму входу четвертой схемы сложения по модулю два подсоединен выход четвертого регистра сдвига, при этом выход первой схемы сложения по модулю два подключен к первому входу четвертого счетчика, выход второй схемы сложения по модулю два подключен к первому входу третьего счетчика, выход третьей схемы сложения по модулю два подключен к первому входу второго счетчика, выход четвертой схемы сложения по модулю два подключен к первому входу первого счетчика, причем третьи входы первого счетчика, второго счетчика, третьего счетчика, четвертого счетчика соединены с вторым выходом генератора тактовой частоты, а ко вторым входам первого счетчика, второго счетчика, третьего счетчика, четвертого счетчика подключены выходы пятой схемы ИЛИ, шестой схемы ИЛИ, седьмой схемы ИЛИ, восьмой схемы ИЛИ, соответственно, при этом к первым входам пятой схемы ИЛИ, шестой схемы ИЛИ, седьмой схемы ИЛИ, восьмой схемы ИЛИ подсоединен выход программируемого счетчика, который также соединен с пятым входом контроллера и первыми входами первой схемы ИЛИ, второй схемы ИЛИ, третьей схемы ИЛИ, четвертой схемы ИЛИ, ко вторым входам пятой схемы ИЛИ, шестой схемы ИЛИ, седьмой схемы ИЛИ, восьмой схемы ИЛИ подключен второй выход контроллера, который подключен также к первому входу программируемого счетчика, первому входу генератора тактовой частоты и ко вторым входам первой схемы ИЛИ, второй схемы ИЛИ, третьей схемы ИЛИ, четвертой схемы ИЛИ и вторым входам первого регистра, второго регистра, третьего регистра, четвертого регистра, к первым входам которых подключен третий выход контроллера, при этом ко вторым входам первого регистра сдвига, второго регистра сдвига, третьего регистра сдвига и четвертого регистра сдвига подключены соответственно выходы первой схемы ИЛИ, второй схемы ИЛИ, третьей схемы ИЛИ и четвертой схемы ИЛИ, причем к первым входам первого регистра сдвига, второго регистра сдвига, третьего регистра сдвига и четвертого регистра сдвига, подключены соответственно выходы первого регистра сдвига, второго регистра сдвига, третьего регистра сдвига и четвертого регистра сдвига, при этом выходы первого счетчика, второго счетчика, третьего счетчика, четвертого счетчика соединены с первым, вторым, третьим и четвертым входами контроллера, причем первый выход контроллера соединен с третьим входом программируемого счетчика, ко второму входу которого подключен третий выход генератора тактовой частоты, первый выход которого соединен с третьими входами первого регистра сдвига, второго регистра сдвига, третьего регистра сдвига и четвертого регистра сдвига.

Сопоставительный анализ технического решения с устройством, выбранным в качестве прототипа, показывает, что новизна технического решения заключается в ведении в заявленное устройство новых схемных элементов: первой схемы ИЛИ, второй схемы ИЛИ, третьей схемы ИЛИ, четвертой схемы ИЛИ, триггера, первого регистра, второго регистра, третьего регистра, четвертого регистра, первой схемы сложения по модулю два, второй схемы сложения по модулю два, третьей схемы сложения по модулю два, четвертой схемы сложения по модулю два, программируемого счетчика, контроллера, пятой схемы ИЛИ, шестой схемы ИЛИ, седьмой схемы ИЛИ, восьмой схемы ИЛИ, первого счетчика, второго счетчика, третьего счетчика, четвертого счетчика.

Таким образом, заявляемое техническое решение соответствует критерию изобретения «новизна».

Анализ известных технических решений в исследуемой и смежных областях позволяет сделать вывод о том, что введенные функциональные узлы известны. Однако введение их в мультиплексирующий цифровой коррелятор с указанными связями придает этому устройству новые свойства. Введенные функциональные узлы взаимодействуют таким образом, что позволяют сократить время входа в синхронизм канала управления динамического мультиплексора с временным или кодовым разделением каналов.

Таким образом, техническое решение соответствует критерию "изобретательский уровень", т.к. оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано для синхронизации каналов управления динамических мультиплексоров с временным и кодовым разделением каналов в каналообразующей аппаратуре цифровых линий связи.

Таким образом, изобретение соответствует критерию "промышленная применимость".

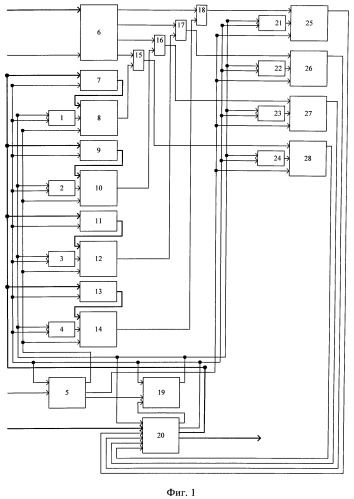

На фиг.1 представлена структурная блок-схема мультиплексирующего цифрового коррелятора,

на фиг.2 - временные диаграммы функционирования мультиплексирующего цифрового коррелятора.

Мультиплексирующий цифровой коррелятор (фиг.1) содержит первую схему ИЛИ 1, вторую схему ИЛИ 2, третью схему ИЛИ 3, четвертую схему ИЛИ 4, генератор тактовой частоты 5, триггер 6, первый регистр 7, первый регистр сдвига 8, второй регистр 9, второй регистр сдвига 10, третий регистр 11, третий регистр сдвига 12, четвертый регистр 13, четвертый регистр сдвига 14, первую схему сложения по модулю два 15, вторую схему сложения по модулю два 16, третью схему сложения по модулю два 17, четвертую схему сложения по модулю два 18, программируемый счетчик 19, контроллер 20, пятую схему ИЛИ 21, шестую схему ИЛИ 22, седьмую схему ИЛИ 23, восьмую схему ИЛИ 24, первый счетчик 25, второй счетчик 26, третий счетчик 27, четвертый счетчик 28, причем первым входом устройства в целом является первый вход триггера 6, вторым входом устройства в целом является второй вход триггера 6, третьим входом устройства в целом является второй вход генератора тактовой частоты 5, четвертым входом устройства в целом является шестой вход контроллера 20, выходом устройства в целом является четвертый выход контроллера 20, при этом первый выход триггера 6 подключен к первому входу первой схемы сложения по модулю два 15, второй выход триггера подключен к первому входу второй схемы сложения по модулю два 16, третий выход триггера подключен к первому входу третьей схемы сложения по модулю два 17, четвертый выход триггера подключен к первому входу четвертой схемы сложения по модулю два 18, причем ко второму входу первой схемы сложения по модулю два 15 подсоединен выход первого регистра сдвига 8, ко второму входу второй схемы сложения по модулю два 16 подсоединен выход второго регистра сдвига 10, ко второму входу третьей схемы сложения по модулю два 16 подсоединен выход третьего регистра сдвига 12, ко второму входу четвертой схемы сложения по модулю два 17 подсоединен выход четвертого регистра сдвига 14, при этом выход первой схемы сложения по модулю два 15 подключен к первому входу четвертого счетчика 28, выход второй схемы сложения по модулю два 16 подключен к первому входу третьего счетчика 27, выход третьей схемы сложения по модулю два 17 подключен к первому входу второго счетчика 26, выход четвертой схемы сложения по модулю два 18 подключен к первому входу первого счетчика 25, причем третьи входы первого счетчика 25, второго счетчика 26, третьего счетчика 27, четвертого счетчика 28 соединены с вторым выходом генератора тактовой частоты 5, а ко вторым входам первого счетчика 25, второго счетчика 26, третьего счетчика 27, четвертого счетчика 28 подключены выходы пятой схемы ИЛИ 21, шестой схемы ИЛИ 22, седьмой схемы ИЛИ 23, восьмой схемы ИЛИ 24, соответственно, при этом к первым входам пятой схемы ИЛИ 21, шестой схемы ИЛИ 22, седьмой схемы ИЛИ 23, восьмой схемы ИЛИ 24 подсоединен выход программируемого счетчика 19, который также соединен с пятым входом контроллера 20 и первыми входами первой схемы ИЛИ 1, второй схемы ИЛИ 2, третьей схемы ИЛИ 3, четвертой схемы ИЛИ 4, ко вторым входам пятой схемы ИЛИ 21, шестой схемы ИЛИ 22, седьмой схемы ИЛИ 23, восьмой схемы ИЛИ 24 подключен второй выход контроллера 20, который подключен также к первому входу программируемого счетчика 19, первому входу генератора тактовой частоты 5 и ко вторым входам первой схемы ИЛИ 1, второй схемы ИЛИ 2, третьей схемы ИЛИ 3, четвертой схемы ИЛИ 4 и вторым входам первого регистра 7, второго регистра 9, третьего регистра 11, четвертого регистра 13, к первым входам которых подключен третий выход контроллера 20, при этом ко вторым входам первого регистра сдвига 8, второго регистра сдвига 10, третьего регистра сдвига 12 и четвертого регистра сдвига 14 подключены соответственно выходы первой схемы ИЛИ 1, второй схемы ИЛИ 2, третьей схемы ИЛИ 3 и четвертой схемы ИЛИ 4, причем к первым входам первого регистра сдвига 8, второго регистра сдвига 10, третьего регистра сдвига 12 и четвертого регистра сдвига 14 подключены соответственно выходы первого регистра сдвига 7, второго регистра сдвига 9, третьего регистра сдвига 11 и четвертого регистра сдвига 13, при этом выходы первого счетчика 25, второго счетчика 26, третьего счетчика 27, четвертого счетчика 28 соединены с первым, вторым, третьим и четвертым входами контроллера 20, причем первый выход контроллера 20 соединен с третьим входом программируемого счетчика 19, ко второму входу которого подключен третий выход генератора тактовой частоты 5, первый выход которого соединен с третьими входами первого регистра сдвига 8, второго регистра сдвига 10, третьего регистра сдвига 12 и четвертого регистра сдвига 14.

Предлагаемое устройство работает следующим образом. Процесс синхронизации динамического мультиплексора с временным или кодовым разделением каналов включает в себя три стадии: поиск цикловой синхронизации канала управления, подтверждение цикловой синхронизации канала управления, обнаружение цикловой синхронизации канала управления после ошибки.

Поиск цикловой синхронизации канала управления сводится к обнаружению циклового синхрослова на известной длине цикла синхронизации.

Поиск циклового синхрослова (или, например, команды активности нулевого канала, выступающей в качестве синхрослова) необходимо вести с допущением о возможном включении и (или) выключении каналов в процессе поиска, т.е. с допущением о возможном изменении длины цикла синхронизации в процессе поиска.

Вторым допущением, которое необходимо делать при поиске циклового синхрослова, является возможное изменение длины и вида цифровых последовательностей циклового синхрослова, команды включения канала, команды выключения канала, команды активности канала, обусловленных отличиями в алгоритме управления для разных версий (моделей, модификаций) мультиплексора.

Мультиплексирующий цифровой коррелятор входит в состав устройства синхронизации канала управления и предназначен для обнаружения циклового синхрослова, команды включения канала, команды выключения канала, команды активности канала в условиях описанных допущений.

На вход триггера 6 мультиплексирующего цифрового коррелятора подается цифровая последовательность принимаемого сигнала (фиг.1).

На вход процессора 20 вводится синхрослово, команда активности канала, команда включения канала, команда выключения канала.

Процессор 20 рассчитывает длину синхрослова, длину команды активности канала, длину команды включения канала, длину команды выключения канала.

Сигнал тактовой синхронизации подается на вход триггера 6 и генератора частоты 5. Изменение фазы сигнала тактовой частоты используется для синхронизации всей схемы мультиплексирующего цифрового коррелятора (фиг.2).

Первый регистр 7, второй регистр 9, третий регистр 11, четвертый регистр 13, первый регистр сдвига 8, второй регистр сдвига 10, третий регистр сдвига 12, четвертый регистр сдвига 14 имеют длину, большую или равную длине команды канала управления.

Процессор 20 записывает синхрослово в первый регистр 7, команду включения канала во второй регистр 9, команду выключения канала в регистр третий регистр 11, команду активности канала в регистр четвертый регистр 13, устанавливает значение программируемого счетчика 19 равным длине команды канала управления. Процессор 20 запускает генератор частоты 5, подав на его вход инверсное значение команды RESET2.

Генератор частоты 5 подает сигнал тактовой частоты CLK+90 (фиг.2) на сумматор 25, сумматор 26, сумматор 27, сумматор 28, запуская их, сигнал тактовой частоты CLK+180 (фиг.2) на первый регистр сдвига 8, на второй регистр сдвига 10, на третий регистр сдвига 12, на четвертый регистр сдвига 14, запуская схему.

Данные из первого регистра 7, второго регистра 9, третьего регистра 11, четвертого регистра 13 записываются в первый регистр сдвига 8, второй регистр сдвига 10, третий регистр сдвига 12, четвертый регистр сдвига 14, соответственно, сигнал тактовой частоты CLK+270 (фиг.2) подается на программируемый счетчик 19, запуская его.

Программируемый счетчик 19 производит счет тактов до значения, равного длине команды канала управления, после чего подает сигнал RESET 1 на следующие схемы ИЛИ: ИЛИ 1, ИЛИ 2, ИЛИ 3, ИЛИ 4, ИЛИ 21, ИЛИ 22, ИЛИ 23, ИЛИ 24, останавливая их, на процессор 20, сигнализируя об окончании счета.

Процессор 20 анализирует значения VALUE 1, VALUE 2, VALUE 3, VALUE 4, полученные от сумматора 25, сумматора 26, сумматора 27, сумматора 28, соответственно. Процессор 20 принимает решение об обнаружении одной из команд канала управления: синхрослова, команды активности канала, команды включения канала, команды выключения канала. Если синхрослово обнаружено дважды, то процессор 20 подает команду RESET2 на первый регистр 7, второй регистр 9, третий регистр 11, четвертый регистр 13, генератор частоты 5, программируемый счетчик 19, схемы ИЛИ: ИЛИ 1, ИЛИ 2, ИЛИ 3, ИЛИ 4, ИЛИ 21, ИЛИ 22, ИЛИ 23, ИЛИ 24, останавливая устройство, иначе принимает решение об анализе новой цифровой последовательности, запуская генератор частоты 5.

Заявляемое устройство обнаруживает в параллельном режиме синхрослово, команды включения и выключения каналов, команды активности каналов, что позволяет пересчитывать длину цикла синхронизации канала управления при включении и (или) выключении канала. В противном случае для синхронизации канала управления необходимо было бы ждать один полный цикл передачи команд канала управления без включений и выключений каналов, что в условиях активной коммутации каналов значительно увеличило время в хождения в цикловый синхронизм.

Таким образом, достигнут положительный эффект, заключающийся в сокращении временя входа в синхронизм канала управления динамического мультиплексора с временным или кодовым разделением каналов в условиях активной коммутации каналов мультиплексором.

Для реализации заявляемого устройства использованы известные элементы и схемы, выпускаемые зарубежной промышленностью.

В качестве генератора тактовой частоты 5 использован генератор частоты Clock Generator для ПЛИС Virtex-5 компании Xilinx Inc., США.

В качестве программируемого счетчика 19 использован восьмиразрядный двоичный счетчик CB8CLE с параллельной синхронной загрузкой, асинхронным сбросом и входом разрешения счета для ПЛИС Virtex-5 компании Xilinx Inc., США.

Контроллер 20 реализован на известном процессоре РРС-440 ПЛИС Virtex-5 компании Xilinx Inc., США.

Первая схема ИЛИ 1, вторая схема ИЛИ 2, третья схема ИЛИ 3, четвертая схема ИЛИ 4, триггер 6, первый регистр - 7, первый регистр сдвига - 8, второй регистр - 9, второй регистр сдвига - 10, третий регистр - 11, третий регистр сдвига - 12, четвертый регистр - 13, первая схема сложения по модулю два 15, вторая схема сложения по модулю два 16, третья схема сложения по модулю два 17, четвертая схема сложения по модулю два 18, пятая схема ИЛИ 21, шестая схема ИЛИ 22, седьмая схема ИЛИ 23, восьмая схема ИЛИ 24, первый счетчик - 25, второй счетчик - 26, третий счетчик - 27, четвертый счетчик - 28 реализованы на ПЛИС Virtex-5 компании Xilinx Inc., США.

Мультиплексирующий цифровой коррелятор, содержащий генератор тактовой частоты, первый регистр сдвига, второй регистр сдвига, третий регистр сдвига и четвертый регистр сдвига, отличающееся тем, что введены первая схема ИЛИ, вторая схема ИЛИ, третья схема ИЛИ, четвертая схема ИЛИ, триггер, первый регистр, второй регистр, третий регистр, четвертый регистр, первая схема сложения по модулю два, вторая схема сложения по модулю два, третья схема сложения по модулю два, четвертая схема сложения по модулю два, программируемый счетчик, контроллер, пятая схема ИЛИ, шестая схема ИЛИ, седьмая схема ИЛИ, восьмая схема ИЛИ, первый счетчик, второй счетчик, третий счетчик, четвертый счетчик, причем первым входом устройства в целом является первый вход триггера, вторым входом устройства в целом является второй вход триггера, третьим входом устройства в целом является второй вход генератора тактовой частоты, четвертым входом устройства в целом является шестой вход контроллера, выходом устройства в целом является четвертый выход контроллера, при этом первый выход триггера подключен к первому входу первой схемы сложения по модулю два, второй выход триггера подключен к первому входу второй схемы сложения по модулю два, третий выход триггера подключен к первому входу третьей схемы сложения по модулю два, четвертый выход триггера подключен к первому входу четвертой схемы сложения по модулю два, причем ко второму входу первой схемы сложения по модулю два подсоединен выход первого регистра сдвига, ко второму входу второй схемы сложения по модулю два подсоединен выход второго регистра сдвига, ко второму входу третьей схемы сложения по модулю два подсоединен выход третьего регистра сдвига, ко второму входу четвертой схемы сложения по модулю два подсоединен выход четвертого регистра сдвига, при этом выход первой схемы сложения по модулю два подключен к первому входу четвертого счетчика, выход второй схемы сложения по модулю два подключен к первому входу третьего счетчика, выход третьей схемы сложения по модулю два подключен к первому входу второго счетчика, выход четвертой схемы сложения по модулю два подключен к первому входу первого счетчика, причем третьи входы первого счетчика, второго счетчика, третьего счетчика, четвертого счетчика соединены с вторым выходом генератора тактовой частоты, а ко вторым входам первого счетчика, второго счетчика, третьего счетчика, четвертого счетчика подключены выходы пятой схемы ИЛИ, шестой схемы ИЛИ, седьмой схемы ИЛИ, восьмой схемы ИЛИ, соответственно, при этом к первым входам пятой схемы ИЛИ, шестой схемы ИЛИ, седьмой схемы ИЛИ, восьмой схемы ИЛИ подсоединен выход программируемого счетчика, который также соединен с пятым входом контроллера и первыми входами первой схемы ИЛИ, второй схемы ИЛИ, третьей схемы ИЛИ, четвертой схемы ИЛИ, ко вторым входам пятой схемы ИЛИ, шестой схемы ИЛИ, седьмой схемы ИЛИ, восьмой схемы ИЛИ подключен второй выход контроллера, который подключен также к первому входу программируемого счетчика, первому входу генератора тактовой частоты и ко вторым входам первой схемы ИЛИ, второй схемы ИЛИ, третьей схемы ИЛИ, четвертой схемы ИЛИ и вторым входам первого регистра, второго регистра, третьего регистра, четвертого регистра, к первым входам которых подключен третий выход контроллера, при этом ко вторым входам первого регистра сдвига, второго регистра сдвига, третьего регистра сдвига и четвертого регистра сдвига, подключены соответственно выходы первой схемы ИЛИ, второй схемы ИЛИ, третьей схемы ИЛИ и четвертой схемы ИЛИ, причем к первым входам первого регистра сдвига, второго регистра сдвига, третьего регистра сдвига и четвертого регистра сдвига подключены соответственно выходы первого регистра сдвига, второго регистра сдвига, третьего регистра сдвига и четвертого регистра сдвига, при этом выходы первого счетчика, второго счетчика, третьего счетчика, четвертого счетчика соединены с первым, вторым, третьим и четвертым входами контроллера, причем первый выход контроллера соединен с третьим входом программируемого счетчика, ко второму входу которого подключен третий выход генератора тактовой частоты, первый выход которого соединен с третьими входами первого регистра сдвига, второго регистра сдвига, третьего регистра сдвига и четвертого регистра сдвига.