Устройство определения ролевой функции участника творческого коллектива

Иллюстрации

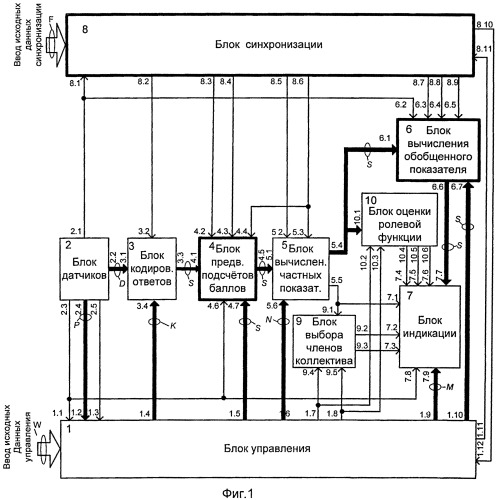

Показать всеИзобретение относится к вычислительной технике, в частности к устройствам психологического моделирования действий лиц, вовлеченных в практически важные ситуации. Техническим результатом от использования заявленного устройства является повышение оперативности оценки характеристик испытуемых. Устройство состоит из блока синхронизации 8, снабженного шиной ввода исходных данных, блоков датчиков 2, кодирования ответов 3, предварительных подсчетов баллов 4, вычисления частных показателей 5, выбора членов коллектива 9, оценки ролевой функции 10, вычисления обобщенного показателя 6, индикации 7 и блока управления 1, снабженного шиной ввода исходных данных. Управляющие входы/выходы блока управления 1 соединены с управляющими выходами/входами соответствующих блоков. Техническим результатом изобретения является повышение оперативности и точности оценки характеристик испытуемых. 5 з.п. ф-лы, 17 ил.

Реферат

Изобретение относится к вычислительной технике, в частности к устройствам психологического моделирования действий лиц, вовлеченных в практически важные ситуации, с последующей оценкой этих действий, к области испытаний профессиональной пригодности и связанному с ними обучению, к области психометрических измерений интеллекта, проводимых в психологии. Устройство может использоваться для проведения индивидуальных экспресс-тестов профессиональной пригодности в условиях отсутствия ресурсов для более полного и точного оценивания уровня готовности личности к инновационной деятельности в практически важных ситуациях, а также при формировании команд для эффективного решения узкоспециализированных наукоемких творческих задач.

Известна автоматизированная система для обучения и контроля знаний (Патент RU №2110095 C1 G09B 7/00), выполненная на базе персонального компьютера, состоящая из пульта управления, устройства ввода ответов и реакций обучаемого, блоков ввода информации, дешифратора управляющих сигналов, буфера данных, устройства управления и синхронизации, счетчика адреса, блока памяти, цифроаналогового преобразователя и аналогового мультиплексора.

Первый аналог позволяет использовать информационную стимуляцию на субсенсорном уровне восприятия в процессе ускоренного индивидуального обучения и контроля знаний.

Недостатком первого аналога является громоздкость и относительно высокая стоимость одного рабочего места из-за использования в качестве базы персонального компьютера.

Известна система тестирования «Телетестинг» (RU 2186423 С2, G09B 7/00), предназначенная для проверки объема и качества знаний при дистанционном обучении, при заочном автоматизированном определении профпригодности, при организационно-управленческом, профориентационном и индивидуально-личностном консультировании, а также при аттестационном контроле кадрового состава предприятий. Система базируется на компьютерных сетевых информационных технологиях и включает в себя блоки подготовительных модулей, модули тестирования, телекоммуникационные модули и модули анализа и обработки.

Второй аналог позволяет реализовать дистанционное одновременное тестирование множества испытуемых, находящихся территориально в различных местах, и обеспечивает секретность тестовых заданий для повышения достоверности получаемых результатов.

Недостатком второго аналога является относительная сложность системы и высокая стоимость одного рабочего места, необходимость разработки специального программного обеспечения для подсчета тестовых баллов в процессе телекоммуникации.

Наиболее близким аналогом (прототипом) по своей технической сущности заявленному устройству является прибор контроля знаний (RU 2110096 C1, G09B 7/07), включающий в себя несколько пультов учащихся, преобразователи угла поворота в код, блок двухпозиционных датчиков, пульт управления прибора, электрическую схему формирования оценок, табло и источник электропитания.

Схема прототипа позволяет использовать его для экспресс-тестинга испытуемых, существенно снизить при этом стоимость одного рабочего места.

Однако устройство-прототип имеет недостатки:

1. Зависимость конструкции прибора от количества и сложности проводимых тестов. В связи с этим для проведения комплексной оценки испытуемого при большом количестве гетерогенных тестовых заданий требуется пропорциональное усложнение конструкции прибора (трудно масштабировать);

2. Необходимость централизованного управления приборами для задания ключей к тестам и управления процессом тестирования.

Целью изобретения является разработка устройства тестирования, обеспечивающего оперативную оценку уровня инновационного интеллекта испытуемых, упрощение масштабирования в соответствии с требуемым количеством испытуемых за счет использования автономных индивидуальных пультов тестирования, децентрализации управления процессом тестирования за счет применения технологии микропрограммных автоматов, возможность применения гетерогенных тестовых заданий с большим количеством вопросов различной сложности и вариантов ответов за счет использования оперативных запоминающих устройств.

Поставленная цель достигается тем, что в известное устройство тестирования, содержащее блок датчиков, D-разрядный, где D≥2, информационный выход которого подключен к D-разрядному информационному входу блока кодирования ответов, блок вычисления частных показателей, пятый управляющий выход которого подключен к первому управляющему входу блока индикации, а N-разрядный, где N≥2, управляющий вход блока вычисления частных показателей подключен к N-разрядному управляющему выходу блока управления, Р-разрядный, где Р≥2, информационный вход которого подключен к Р-разрядному управляющему выходу блока датчиков, пятый управляющий выход которого подключен к третьему управляющему входу блока управления, а третий управляющий выход блока датчиков подключен к первому управляющему входу блока управления и восьмому управляющему входу блока индикации, K-разрядный и М-разрядный, где К≥2 и М≥2, информационные выходы блока управления подключены соответственно к K-разрядному информационному входу блока кодирования ответов и к М-разрядному информационному входу блока индикации, дополнительно введены блок синхронизации, блок предварительных подсчетов баллов, блок вычисления обобщенного показателя, блок выбора членов коллектива и блок оценки ролевой функции, S-разрядный, где S≥2, информационный вход которого подключен к S-разрядному информационному выходу блока вычисления частных показателей, второй и третий управляющие входы блока оценки ролевой функции подключены соответственно к седьмому и восьмому управляющим выходам блока управления, четвертый, пятый и шестой информационные выходы блока оценки ролевой функции подключены соответственно к четвертому, пятому и шестому информационным входам блока индикации, первый информационный вход блока выбора подключен к пятому информационному выходу блока вычисления частных показателей, четвертый и пятый управляющие входы блока выбора подключены соответственно к седьмому и восьмому управляющим выходам блока управления, второй и третий информационные выходы блока выбора подключены соответственно к второму и третьему информационным входам блока индикации, S-разрядный информационный вход блока вычисления обобщенного показателя подключен к S-разрядному информационному выходу блока вычисления частных показателей. Третий, четвертый и пятый синхронизирующие входы блока вычисления обобщенного показателя подключены соответственно к седьмому, восьмому и девятому синхронизирующим выходам блока синхронизации. Второй управляющий вход и седьмой управляющий S-разрядный вход блока вычисления обобщенного показателя подключены соответственно к первому управляющему выходу блока датчиков и к S-разрядному десятому управляющему выходу блока управления. S-разрядный шестой информационный выход блока вычисления обобщенного показателя подключен к S-разрядному информационному входу блока индикации. S-разрядные информационные вход и выход блока предварительных подсчетов балов подключены соответственно к S-разрядным информационным выходу блока кодирования ответов и входу блока вычисления частных показателей. S-разрядный управляющий вход и шестой управляющий вход блока предварительных подсчетов баллов подключены соответственно к S-разрядному пятому управляющему выходу блока управления и к третьему выходу БД. Четвертый синхронизирующий вход блока предварительных подсчетов баллов и третий синхронизирующий вход блока вычисления частных показателей подключены к шестому выходу блока синхронизации. Второй и третий синхронизирующие входы блока предварительных подсчетов баллов подключены соответственно к третьему и четвертому синхронизирующим выходам блока синхронизации, второй синхронизирующий выход которого подключен к синхронизирующему входу блока кодирования ответов. Пятый синхронизирующий выход блока синхронизации подключен к второму синхронизирующему входу блока вычисления частных показателей. Одиннадцатый управляющий выход и двенадцатый управляющий вход блока управления подключены соответственно к одиннадцатому управляющему входу и десятому выходу блока синхронизации. Первый управляющий вход блока синхронизации подключен к первому управляющему выходу блока датчиков. Блок синхронизации и блок управления снабжены соответственно F-разрядным, где F≥2 и W-разрядным, где W≥2, вводами исходных данных синхронизации и управления.

Блок предварительных подсчетов баллов состоит из каскадно включенных по S-разрядному информационному сигналу первого накопительного сумматора, делителя, умножителя и второго накопительного сумматора, первого и второго элементов «ИЛИ», выходы которых подключены соответственно к обнуляющим входам первого и второго накопительных сумматоров. S-разрядные информационные вход первого и выход второго накопительных сумматоров являются соответственно S-разрядными информационными входом и выходом блока промежуточных подсчетов баллов. Синхронизирующий вход делителя является вторым синхронизирующим входом блока промежуточных подсчетов баллов. Вход первого элемента «ИЛИ» и вход умножителя объединены и являются третьим синхронизирующим входом блока промежуточных подсчетов баллов. Первый вход второго элемента «ИЛИ» является четвертым управляющим входом блока промежуточных подсчетов баллов. Четвертый S-разрядный управляющий вход делителя и объединенные вторые входы первого и второго элементов «ИЛИ» являются соответственно S-разрядным седьмым и шестым управляющими входами блока предварительных подсчетов баллов.

Блок вычисления обобщенного показателя состоит из каскадно включенных по S-разрядному информационному сигналу умножителя, накопительного сумматора, вычислителя квадратного корня и делителя. Первый S-разрядный информационный вход умножителя и третий S-разрядный информационный выход делителя являются соответственно S-разрядными информационными входом и выходом блока вычисления обобщенного показателя. S-разрядный управляющий вход делителя является седьмым S-разрядным управляющим входом блока вычисления обобщенного показателя. Синхронизирующие вход умножителя, вход вычислителя квадратного корня и вход делителя являются соответственно третьим, четвертым и пятым синхронизирующими входами блока вычисления обобщенного показателя. Управляющий вход накопительного сумматора является вторым управляющим входом блока вычисления обобщенного показателя.

Блок синхронизации состоит из генератора тактовых импульсов, триггерного ключа, дешифратора, счетчика тактовых импульсов, компаратора, счетчика адреса, регистра памяти, элемента задержки и элемента «ИЛИ». Информационный выход компаратора подключен к входу «Стоп» триггерного ключа и через элемент задержки к информационному входу счетчика адреса, D-разрядные, где D≥2, третий и первый информационные входы компаратора подключены соответственно к D-разрядным информационным выходу счетчика тактовых импульсов и выходу регистра памяти, R-разрядный, где R≥3, управляющий выход счетчика адреса подключен к R-разрядным управляющим входам регистра памяти и дешифратора. Информационный выход триггерного ключа подключен к информационному входу счетчика тактовых импульсов и информационному входу дешифратора. Выход генератора тактовых импульсов подключен к первому информационному входу триггерного ключа. Управляющий вход «Старт» триггерного ключа подключен к выходу элемента «ИЛИ», шестой вход которого является одинадцатым управляющим входом блока синхронизации. Информационные выходы (с третьего по десятый) дешифратора являются соответстветственно синхронизирующими выходами (с 2-го по 9-й) блока синхронизации. Четвертый, шестой, восьмой и девятый информационные выходы дешифратора подключены соответственно к второму, третьему, четвертому и пятому входам элемента «ИЛИ». Информационный выход компаратора является десятым управляющим выходом блока синхронизации. Входы «Установка нуля» счетчика тактовых импульсов и счетчика адреса объединены и являются первым управляющим входом блока синхронизации. D-разрядный информационный вход/выход и R-разрядный адресный вход регистра памяти образуют F-разрядный вход исходных данных синхронизации, где F=D+R.

Блок оценки ролевой функции состоит из регистра памяти, первого, второго и третьего компараторов двоичных чисел, второй информационный выход регистра памяти подключен к первому информационному входу первого компаратора и третьему информационному входу третьего компаратора, третий информационный выход регистра памяти подключен к третьему информационному входу первого компаратора и к первому информационному входу второго компаратора, четвертый информационный выход регистра памяти подключен к третьему информационному входу второго компаратора и к первому информационному входу третьего компаратора, причем первый 5-разрядный информационный вход регистра памяти является первым информационным входом блока оценки ролевой функции, пятый и шестой управляющие входы регистра памяти являются вторым и третьим управляющими входами блока оценки ролевой функции, информационные выходы первого, второго и третьего компараторов являются соответственно четвертым, пятым и шестым информационными выходами блока оценки ролевой функции.

Блок выбора членов коллектива состоит регистра памяти, мажоритарного элемента и элемента «И», второй, третий и четвертый информационные выходы регистра памяти подключены соответственно к первым, вторым и третьим информационным входам мажоритарного элемента и элемента «И», причем первый информационный вход регистра памяти является первым информационным входом блока выбора, пятый и шестой управляющие входы регистра памяти являются соответственно четвертым и пятым управляющими входами блока выбора, а четвертый информационные выходы элемента «И» и мажоритарного элемента являются соответственно вторым и третьим информационными выходами блока выбора.

Указанные в формуле изобретения буквенные обозначения имеют следующий смысл:

S - количество разрядов кода, соответствующего максимальному количеству баллов, начисляемых за решение одного тестового задания.

Р - количество разрядов кода, соответствующего максимальному количеству тестовых заданий.

D - количество разрядов кода, соответствующего максимальному количеству вопросов в тестовом задании.

М - количество разрядов кода, отражающего максимальный объем данных одного тестового задания.

R - количество разрядов адресного входа дешифратора БС (в рассматриваемом случае R≥3).

V - количество разрядов кода, соответствующего максимальному значению обобщенного показателя.

Q - количество разрядов кода, соответствующего количеству оцениваемых частных показателей (в рассматриваемом случае Q≥3).

U - количество разрядов, соответствующее разрядности управляющих входов графического ЖКИ.

Благодаря новым совокупностям существенных признаков при реализации устройства обеспечивается двухуровневая оценка общего показателя инновационного интеллекта, их простота модификации структуры и содержания тестов и автоматизация всех процедур, т.е. повышение оперативности проведения исследований, кроме того, устройство позволяет осуществлять отбор кандидатов по заданным критериям, определять для каждого участника предпочитаемый характер решаемых задач инновационного процесса.

Изобретение поясняется чертежами, на которых показаны:

на фиг.1 - структурная схема устройства;

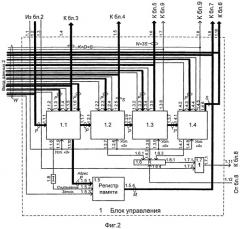

на фиг.2 - структурная схема блока управления (БУ);

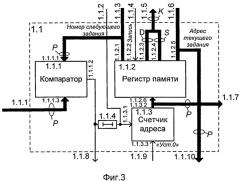

на фиг.3-6 - структурные схемы микропрограммных модулей блока управления;

на фиг.7 - структурная схема блока датчиков (БД);

на фиг.8 - структурная схема блока кодирования ответов (БКО);

на фиг.9 - структурная схема блока предварительных подсчетов баллов (БППБ);

на фиг.10 - структурная схема блока вычисления частных показателей (БВЧП);

на фиг.11 - структурная схема блока вычисления обобщенного показателя (БВОП);

на фиг.12 - структурная схема блока индикации (БИ);

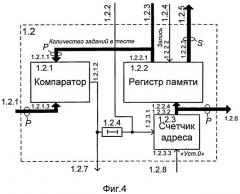

на фиг.13 - структурная схема блока синхронизации (БС);

на фиг.14 - структурная схема триггерного ключа БС;

на фиг.15 - структурная схема блока выбора членов коллектива (БВЧК);

на фиг.16 - структурная схема блока оценки ролевой функции (БОРФ);

на фиг.17 - трехкомпонентная модель инновационного интеллекта;

на фиг.18 - блок-схема алгоритма функционирования устройства.

Заявленное устройство, показанное на фиг.1, состоит из блока управления 1, блока датчиков 2, блока кодирования ответов 3, блока предварительных подсчетов баллов 4, блока вычисления частных показателей 5, блока вычисления обобщенного показателя 6, блока индикации 7, блока синхронизации 8, блока выбора членов коллектива 9 и блока оценки ролевой функции 10.

D-разрядный, где D≥2, информационный выход 2.2 БД 2 подключен к D-разрядному информационному входу 3.1 БКО 3. Пятый управляющий выход 5.5 БВЧП 5 подключен к первому управляющему входу 7.1 БИ 7. N-разрядный, где N≥2, управляющий вход 5.6 БВЧП 5 подключен к N-разрядному управляющему выходу 1.6 БУ 1. Р-разрядный, где Р≥2, информационный вход 1.2 БУ 1 подключен к Р-разрядному управляющему выходу 2.4 БД 2. Пятый 2.5 управляющий выход БД 2 подключен к третьему 1.3 управляющему входу БУ 1. Третий управляющий выход 2.3 БД 2 подключен к первому управляющему входу 1.1 БУ 1 и восьмому управляющему входу 7.8 БИ 7. K-разрядный 1.4 и М-разрядный 1.9, где К≥2 и М≥2, информационные выходы БУ 1 подключены соответственно к К-разрядному информационному входу 3.4 БКО 3 и к М-разрядному информационному входу 7.9 БИ 7. S-разрядный, где S≥2, информационный вход 6.1 БВОП 6 подключен к S-разрядному информационному выходу 5.4 БВЧП 5. Третий 6.3, четвертый 6.4 и пятый 6.5 синхронизирующие входы БВОП 6 подключены соответственно к седьмому 8.7, восьмому 8.8 и девятому 8.9 синхронизирующим выходам БС 8. Второй управляющий вход 6.2 и седьмой управляющий S-разрядный вход 6.6 БВОП 6 подключены соответственно к первому управляющему выходу 2.1 БД 2 и к S-разрядному управляющему выходу 1.10 БУ 1. S-разрядный информационный выход 6.6 БВОП 6 подключен к S-разрядному информационному входу 7.7 БИ 7. S-разрядные информационные вход 4.1 и выход 4.5 БППБ 4 подключены соответственно к S-разрядным информационным выходу 3.3 БКО 3 и входу 5.1 БВЧП 5. S-разрядный управляющий вход 4.7 и управляющий вход 4.6 БППБ 4 подключены соответственно к S-разрядному пятому 1.5 управляющему выходу БУ 1 и к выходу 2.3 БД 2. Четвертый синхронизирующий вход 4.4 БППБ 4 и третий синхронизирующий вход 5.3 БВЧП 5 подключены к выходу 8.6 БС 8. Второй 4.2 и третий 4.3 синхронизирующие входы БППБ 4 подключены соответственно к третьему 8.3 и четвертому 8.4 синхронизирующим выходам БС 8. Второй синхронизирующий выход 8.2 БС 8 подключен к синхронизирующему входу 3.2 БКО 3. Пятый 8.5 синхронизирующий выход БС 8 подключен соответственно к второму 5.2 синхронизирующему входу БВЧП 5. Одиннадцатый 1.11 управляющий выход и двенадцатый 1.12 управляющий вход БУ 1 подключены соответственно к одиннадцатому 8.11 управляющему входу и десятому 8.10 выходу БС 8. Первый управляющий вход 8.1 БС 8 подключен к первому 2.1 управляющему выходу БД 2, причем БС 8 и БУ 1 снабжены соответственно F-разрядным, где F≥2 и W-разрядным, где W≥1, вводами исходных данных синхронизации и управления.

Блок управления 1, структурная схема которого представлена на фиг.1, предназначен для хранения данных тестовых заданий, назначения весовых коэффициентов сложности тестовых заданий, а также для выдачи необходимых данных на основные блоки устройства. Реализация блока может быть различной, в частности, как показано на фиг.2, на основе принципа построения микропрограммного автомата [4, 5, 6].

БУ 1 осуществляет своевременную выдачу данных в такие элементы устройства, как умножители, делители, компараторы. Он состоит из четырех каскадно включенных по P-разрядному, где Р≥2, управляющему сигналу типовых модулей 1.1, 1.2, 1.3, 1.4, которые реализуют принцип работы микропрограммного автомата, регистра памяти 1.5 для хранения данных тестовых заданий, регистра сдвига 1.6 с параллельной записью и последовательным считыванием из очереди типа FIFO, элемента «ИЛИ» 1.7 и элемента задержки 1.8. Первый вход 1.7.1 элемента «ИЛИ» подключен к четвертому 1.6.4 информационному выходу регистра сдвига 1.6, а второй 1.7.2 вход элемента «ИЛИ» 1.7 является третьим 1.3 управляющим входом БУ 1. Информационный выход 1.7.3 элемента «ИЛИ» 1.7 является одиннадцатым 1.11 управляющим выходом БУ 1. Первый 1.6.1, второй 1.6.2 и третий 1.6.3 информационные входы регистра сдвига 1.6 подключены соответственно к седьмому 1.2.7 управляющему выходу второго модуля 1.2, восьмому 1.3.8 управляющему выходу третьего модуля 1.3 и седьмому 1.4.7 управляющему выходу четвертого модуля 1.4. Пятый управляющий вход 1.6.5 регистра сдвига 1.6 является двенадцатым 1.12 управляющим входом БУ 1. Восьмой 1.1.8 и Р-разрядный десятый 1.1.10 управляющие выходы первого модуля 1.1 подключены соответственно через элемент задержки 1.8 к второму 1.5.2 и первому 1.5.1 управляющим входам регистра памяти 1.5. Второй 1.7.2 управляющий вход элемента «ИЛИ» 1.7 является третьим 1.3 управляющим входом БУ 1. Р-разрядный управляющий вход 1.1.1 первого модуля 1.1 является вторым 1.2 управляющим входом БУ 1. Обнуляющие входы «Уст.0» 1.1.9, 1.2.8, 1.3.9, 1.4.8 модулей 1.1-1.4 объединены и образуют первый 1.1 управляющий вход БУ 1. Информационные выходы 1.1.4, 1.2.5, 1.3.5, 1.3.6, 1.4.5, 1.4.6 модулей 1.1, 1.2, 1.3, 1.4 являются соответственно K-разрядным четвертым 1.4, S-разрядным пятым 1.5, N-разрядным шестым 1.6, седьмым 1.7, восьмым 1.8 и S-разрядным десятым 1.10 управляющими выходами БУ 1. М-разрядный, где М≥2, выход 1.5.4 регистра памяти 1.5 является девятым 1.9 управляющим выходом БУ 1.

Каждый типовой модуль, схемы которых показаны на фиг.3, 4, 5, состоит из компаратора 1.1.1-1.4.1, регистра памяти 1.1.2-1.4.2, счетчика адреса 1.1.3-1.4.3 и элемента задержки 1.1.4-1.4.4. Типовой модуль имеет следующую структуру, которую можно рассмотреть на примере первого модуля (см. фиг.3). Адресный вход 1.1.2.6 регистра памяти 1.1.2 подключен к информационному выходу 1.1.3.2 счетчика адреса 1.1.3, а первый информационный выход 1.1.2.1 регистра памяти 1.1.2 подключен к первому информационному входу 1.1.1.1 компаратора 1.1.1. Выход компаратора 1.1.1.2 подключен через элемент задержки 1.1.4 к информационному входу 1.1.3.1 счетчика адреса.

Первый модуль 1.1 (фиг.3) обеспечивает работу БКО 2. Третий информационный вход 1.1.1.3 компаратора 1.1.1 является первым управляющим входом 1.1.1 модуля 1.1. Третий управляющий вход 1.1.3.3 счетчика адреса 1.1.3 является девятым управляющим входом 1.1.9 модуля 1.1. Информационный выход 1.1.1.2 компаратора 1.1.1 является восьмым 1.1.8 управляющим выходом модуля 1.1. D-разрядный третий 1.1.2.3 и S-разрядный четвертый 1.1.2.4 информационные выходы регистра памяти 1.1.2 образуют K-разрядный, где K=D+S, пятый управляющий выход 1.1.5 модуля 1.1. Р-разрядные второй информационный выход 1.1.3.2 счетчика адреса 1.1.3 и пятый информационный выход 1.1.2.5 регистра памяти 1.1.2 являются соответственно седьмым 1.1.7 и шестым 1.1.6 управляющими выходами модуля 1.1. Первый 1.1.3.1 информационный вход счетчика адреса 1.1.3, первый 1.1.2.1, третий 1.1.2.3, четвертый 1.1.2.4 и пятый 1.1.2.5 информационные выходы и второй 1.1.2.2 управляющий вход «Запись» регистра памяти 1.1.2 используются для предварительного ввода исходных данных в модуль 1.1.

Второй модуль 1.2 (см. фиг.4) обеспечивает работу БППБ 4. Третий 1.2.1.3 информационный вход компаратора 1.2.1 является первым управляющим входом 1.2.1 модуля 1.2. Третий управляющий вход 1.2.3.3 счетчика адреса 1.2.3. является восьмым 1.2.8 управляющим входом модуля 1.2. Выход компаратора 1.2.1.2 является седьмым 1.2.7 управляющим выходом модуля 1.2. S-разрядный третий 1.2.2.3 информационный выход регистра памяти 1.2.2 и Р-разрядный второй 1.2.3.2 информационный выход счетчика адреса 1.2.3 являются соответственно пятым 1.2.5 и шестым 1.2.6 управляющими выходами модуля 1.2. Первый 1.2.3.1 информационный вход счетчика адреса 1.2.3, первый 1.2.2.1 и третий 1.2.2.3 информационные выходы, а также второй управляющий вход «Запись» 1.2.2.2 регистра памяти 1.2.2 используются для предварительного ввода данных в модуль 1.2.

Третий модуль 1.3 обеспечивает работу БВЧП 5, БВ 9 и БОРФ 10. Р-разрядный третий информационный вход 1.3.1.3 компаратора 1.3.1 и третий управляющий вход 1.3.3.3 счетчика адреса 1.3.3 являются соответственно первым 1.3.1 и девятым 1.3.9 управляющими входами модуля 1.3. Выход 1.3.1.2 компаратора 1.3.1 является восьмым 1.3.8 управляющим выходом модуля 1.3. S-разрядные третий 1.3.2.3, четвертый 1.3.2.4 и пятый 1.3.2.5 информационные выходы регистра памяти 1.3.2 образуют N-разрядный, где N=3S, пятый 1.3.5 управляющий выход модуля 1.3. Шестой 1.3.2.6 информационный выход регистра памяти 1.3.2 является вторым управляющим выходом модуля 1.3. Р-разрядный второй выход 1.3.3.2 счетчика адреса 1.3.3 является седьмым 1.3.7 управляющим выходом модуля 1.3. Первый информационный вход 1.3.3.1 счетчика адреса 1.3.3, первый 1.3.2.1, третий 1.3.2.3, четвертый 1.3.2.4, пятый 1.3.2.5 информационные выходы и второй 1.3.2.2 управляющий вход регистра памяти 1.3.2 используются для предварительного ввода исходных данных в модуль 1.3.

Четвертый модуль 1.4 обеспечивает работу БВОП 6, БВ 9 и БОРФ 10. P-разрядный третий информационный вход 1.4.1.3 компаратора 1.4.1 и третий управляющий вход 1.4.3.3 счетчика адреса 1.4.3 являются соответственно первым 1.4.1 и восьмым 1.4.8 управляющими входами модуля 1.4. Третий 1.4.2.3 и S-разрядный четвертый 1.4.2.4 информационные выходы регистра памяти 1.4.2 являются соответственно третьим 1.4.3 и шестым 1.4.6 управляющими выходами модуля 1.4. Выход 1.4.1.2 компаратора 1.4.1 является седьмым 1.4.7 управляющим выходом модуля 1.4. Первый информационный вход 1.4.3.1 счетчика адреса 1.4.3, первый 1.4.2.1 и четвертый 1.4.2.4 информационные выходы, второй 1.4.2.2 управляющий вход регистра памяти 1.4.2 используются для предварительного ввода исходных данных в модуль 1.4.

Регистр сдвига 1.6 предназначен для обеспечения согласованной работы БУ 1 и БС 8. Через его информационные входы 1.6.1-1.6.3 записываются разрешающие сигналы, соответствующие логической единице и считываются по очереди от первого к третьему при поступлении тактовых импульсов на пятый 1.6.5 вход регистра сдвига.

БД 2, схема которого представлена на фиг.7, предназначен для кодирования двоичным кодом номера теста и номера ответа, которые выбираются испытуемым, а также для установки в исходное состояние всех счетчиков устройства. БД 2 может быть реализован различным образом, например, как показано на фиг.7, с помощью двухпозиционных датчиков 2.1, 2.2, 2.3, 2.6, счетчика номера теста 2.5, реверсивного счетчика номера ответа 2.4 и регистра памяти 2.7. D-разрядный первый информационный вход 2.7.1 регистра памяти 2.7 подключен к D-разрядному информационному выходу 2.4.2 счетчика номера ответа 2.4. Третий управляющий вход 2.7.3 регистра памяти 2.7 подключен к выходу 2.6.2 датчика «Запись» 2.6. Первый информационный вход 2.4.1 счетчика номера ответа 2.4 подключен к выходу 2.1.3 датчика «Выбор ответа» 2.1, а третий обнуляющий вход 2.4.3 счетчика номера ответа подключен к выходу датчика «Выбор теста» 2.2. Первый информационный вход 2.5.1 счетчика номера теста 2.5 подключен к выходу 2.2.2 датчика «Выбор теста» 2.2, а третий обнуляющий вход 2.5.3 счетчика номера теста 2.5 подключен к выходу 2.3.2 датчика «Установка 0» 2.3. На входы 2.1.1 и 2.1.2 датчика «Выбор ответа» 2.1 подаются потенциалы, соответствующие логическим нулю и единице, а на входы датчиков 2.2.1, 2.3.1, 2.6.1 «Выбор теста» 2.2, «Установка 0» 2.3 и «Запись» 2.6 подается потенциал, соответствующий логической единице. Выход 2.3.2 датчика «Установка 0» 2.3 является первым 2.1 и третьим 2.3 управляющими выходами БД 2. D-разрядный выход 2.7.2 регистра памяти 2.7 и Р-разрядный выход 2.5.2 счетчика номера теста 2.5 являются соответственно вторым 2.2 и четвертым 2.4 информационными выходами БД 2. Выход 2.6.2 датчика «Запись» 2.6 является пятым 2.5 управляющим выходом БД 2.

БКО 3 предназначен для определения количества баллов за выбранный ответ на тестовое задание в соответствии с предварительно заданными вестовыми коэффициентами заданий. БКО 3 может быть реализован различным образом, в частности, как показано на фиг.8.

БКО 3 состоит из компаратора 3.1 и умножителя 3.2. Первый информационный вход 3.2.1 умножителя 3.2 подключен к выходу 3.1.2 компаратора 3.1. Первый 3.1.1 информационный вход компаратора 3.1 и информационный выход 3.2.3 умножителя 3.2 являются соответственно D-разрядным информационными входом 3.1 и S-разрядным выходом 3.3 БКО 3, а третий вход 3.1.3 компаратора 3.1 и четвертый вход 3.2.4 умножителя 3.2 образуют K-разрядный управляющий вход БКО 3, где K=S+D. Второй синхронизирующий вход 3.2.2 умножителя является вторым 3.2 синхронизирующим входом БКО 3.

БППБ 4 предназначен для вычисления суммарного и среднего количества баллов, начисляемых по результатам выполнения тестовых заданий и подготовки исходных данных для вычисления частных показателей интеллекта. БППБ 4 может быть реализован различным образом, в частности, как показано на фиг.9.

БППБ 4 состоит из каскадно включенных по 5-разрядному информационному сигналу первого накопительного сумматора 4.1, делителя 4.2, умножителя 4.3, второго накопительного сумматора 4.4, первого 4.5 и второго 4.6 элементов «ИЛИ». Умножитель 4.3 осуществляет возведение в квадрат числа, поступающего в двоичном коде на первый его вход 4.3.1.

Первый вход 4.1.1 первого и второй выход 4.4.2 второго накопительного сумматора являются соответственно информационным входом 4.1 и выходом 4.5 БППБ 4. Входы 4.5.3 и 4.6.3 первого 4.5 и второго 4.6 элементов «ИЛИ» являются шестым 4.6 управляющим входом БППБ 4. Второй вход 4.6.2 второго элемента «ИЛИ» является четвертым 4.4 управляющим входом БППБ 4. Синхронизирующие входы 4.2.2, 4.3.2 делителя 4.2 и умножителя 4.3 являются синхронизирующими входами 4.2 и 4.3 БПП 4. S-разрядный четвертый 4.2.4 управляющий вход делителя 4.2 является седьмым 4.7 управляющим входом БППБ 4.

Начальная установка в исходное состояние накопительных сумматоров 4.1 и 4.4 осуществляется подачей на их управляющие входы 4.1.3 и 4.4.3 через первый 4.5 и второй 4.6 элементы «ИЛИ» потенциала логической единицы, который поступает через шестой 4.6 управляющий вход БППБ 4. Подготовка БППБ 4 к очередному этапу работы осуществляется обнулением накопительных сумматоров 4.1. и 4.4 тактовыми импульсами, поступающими через третий 4.3 и четвертый 4.4 синхронизирующие входы БППБ 4.

БВЧП 5 предназначен для вычисления значений частных показателей интеллекта и формирования по результатам вычисления информационного сигнала на БИ 7, а также для подготовки исходных данных для вычисления значения обобщенного показателя. БВЧП 5 может быть реализован различным образом, в частности, как показано на фиг.10.

БВЧП 5 состоит из каскадно включенных по S-разрядному информационному сигналу первого 5.2 и второго 5.3 делителей и компаратора 5.1.

Первый вход 5.2.1 первого делителя 5.2 и выход 5.3.3 второго делителя 5.3 являются соответственно информационными входом 5.1 и выходом 5.4 БВЧП 5. Выход 5.1.2 компаратора 5.1 является пятым 5.5 управляющим выходом БВЧП 5. Синхронизирующие входы 5.2.2 и 5.2.3 делителей 5.2 и 5.3 являются соответственно вторым 5.2 и третьим 5.3 синхронизирующими входами БВЧП 5, а четвертый информационные входы 5.2.4, 5.3.4 делителей 5.2 и 5.3 и третий информационный вход 5.1.3 компаратора 5.1 образуют управляющий N-разрядный вход 5.6 БВЧП 5, где N=3S.

БВОП 6 предназначен для вычисления значения обобщенного показателя интеллекта испытуемого и формирования информационного сигнала в БИ 7. БВОП 6 может быть реализован различным образом, в частности, как показано на фиг 11.

БВОП 6 состоит из каскадно включенных по S-разрядному информационному сигналу умножителя 6.1, накопительного сумматора 6.2, вычислителя квадратного корня 6.3 и делителя 6.4. S-разрядные вход 6.1.1 умножителя 6.1 и выход 6.4.3 делителя 6.4 являются соответственно информационным входом 6.1 и информационным выходом 6.6 БВОП 6. Синхронизирующие входы 6.1.2, 6.3.2, 6.4.2 умножителя 6.1, вычислителя квадратного корня 6.3 и делителя 6.4 являются синхронизирующими входами 6.3-6.5 БВОП 6. S-разрядный вход 6.4.1 делителя 6.4 и обнуляющий вход 6.2.2 накопительного сумматора 6.2 являются соответственно управляющими входами 6.7 и 6.2 БВОП 6.

БИ 7 предназначен для представления испытуемому содержания тестовых заданий, а также отображения результатов вычисления частных и обобщенного показателей интеллекта. БИ 7 может быть реализован различным образом, в частности, как показано на фиг.12.

БИ 7 состоит из счетчика адреса 7.1, дешифраторов 7.2-7.6, сегментного жидкокристаллического индикатора ЖКИ 7.8, индикаторов состояния 7.9-7.12, триггеров 7.13-7.15 и графического жидкокристаллического индикатора ЖКИ 7.6. Управление графическим ЖКИ 7.6 осуществляется через его входы 7.6.1 и 7.6.2, к которым подключены выходы 7.5.2 и 7.4.2 четвертого 7.5 и третьего 7.4 дешифраторов. Управление сегментным ЖКИ 7 осуществляется через его вход 7.7.1, к которому подключен выход 7.2.2 первого дешифратора 7.2. Управление индикаторами состояния 7.9-7.12 осуществляется через соответствующие входы 7.9.1-7.12.1, которые посредством триггеров 7.13-7.15 подключены к выходам 7.3.2-7.3.4 дешифратора 7.3. Индикатор «Не готов» 7.12 управляется через его вход 7.12.1, который посредством триггера 7.6 подключен к входу 7.3 БИ. Q-разрядный управляющий вход 7.3.1 второго дешифратора 7.3 подключен к выходу 7.1.2 счетчика адреса 7.1. Информационный вход 7.1.1 счетчика адреса 7.1 является первым информационным входом 7.1 БИ 7. S-разрядный информационный вход 7.2.1 первого дешифратора 7.2 является седьмым 7.7 информационным входом БИ 7. М/2-разрядные информационные входы 7.4.1 и 7.5.1 третьего 7.4 и четвертого 7.5 дешифраторов образуют девятый 7.9 М-разрядный информационный вход БИ 7. Третий 7.1.3 обнуляющий вход счетчика адреса 7.1 является восьмым 7.8 управляющим входом БИ 7.

БС 8 предназначен для формирования синхронизирующих сигналов и выдачи их в другие блоки в соответствии с алгоритмом работы устройства, он обеспечивает согласованную работу таких элементов устройства, как умножители, делители и вычислитель квадратного корня. БС 8 может быть реализован различным образом, в частности, как показано на фиг.13.

БС 8 состоит из генератора тактовых импульсов 8.1, триггерного ключа 8.2, дешифратора 8.3, счетчика тактовых импульсов 8.4, компаратора 8.5, счетчика адреса 8.6 и регистра памяти 8.7, элемента задержки 8.8 и элемента «ИЛИ» 8.9. Информационный выход 8.5.3 компаратора 8.5 подключен к входу «Стоп» 8.2.2 триггерного ключа 8.2.2 и через элемент задержки 8.8 к информационному входу 8.6.1 счетчика адреса 8.6. D-разрядные третий 8.5.3 и первый 8.5.1 информационные входы компаратора 8.5 подключены соответственно к D-разрядным информационным выходу 8.4.1 счетчика тактовых импульсов 8.4 и выходу 8.7.2 регистра памяти 8.7 R-разрядный управляющий выход 8.6.2 счетчика адреса 8.6 подключен к R-разрядным управляющим входу 8.7.1 регистра памяти 8.7 и входу 8.3.2 дешифратора 8.3. Информационный выход 8.2.3 триггерного ключа 8.2 подключен к информационному входу 8.4.2 счетчика тактовых импульсов 8.4 и информационному входу 8.3.1 дешифратора 8.3. Выход 8.1.1 генератора тактовых импульсов 8.1 подключен к первому информационному входу 8.2.1 триггерного ключа 8.2. Управляющий вход «Старт» 8.2.4 триггерного ключа 8.2 подключен к выходу 8.9.1 элемента «ИЛИ» 8.9, шестой вход 8.9.6 которого является одиннадцатым 8.1 управляющим входом блока синхронизации 8, а информационные выходы 8.3.3-8.3.10 дешифратора 8.3 являются соответствующими синхронизирующими выходами 8.2-8.9 блока синхронизации 8. Четвертый 8.3.4, шестой 8.3.6, восьмой 8.3.8 и девятый 8.3.9 информационные выходы дешифратора 8.3 подключены к входам 8.9.2-8.9.5 элемента «ИЛИ» 8.9. Входы «Установка нуля» 8.4.3 счетчика тактовых импульсов 8.4 и 8.6.3 счетчика адреса 8.6 объединены и являются первым 8.11 управляющим входом блока синхронизации 8. D-разрядный информационный выход 8.7.2 и R-разрядный адресный вход 8.7.1. регистра памяти 8.7 образуют F-разрядный вход блока синхронизации 8 для ввода данных синхронизации, где F=D+R.

Схема триггерного ключа 8.2 должна пропускать импульсы равной длительности. Триггерный ключ 8.2 может быть реализован различным образом, в частности, как показано на фиг.14. Он состоит из первого 8.2.1.1 и второго 8.2.1.3 RS-триггеров, элемента инверсии 8.2.1.2 и элемента «И» 8.2.1.4. Выход первого триггера 8.2.1.1 подключен к D-входу второго триггера 8.2.1.3. Выход второго триггера 8.2.1.3 подключен ко второму входу элемента «И» 8.2.1.4. Синхронизирующий вход второго триггера 8.2.1.3 подключен к выходу элемента инверсии 8.2.1.2. Входы элемента инверсии 8.2.1.2 и