Функционально-полный толерантный элемент

Иллюстрации

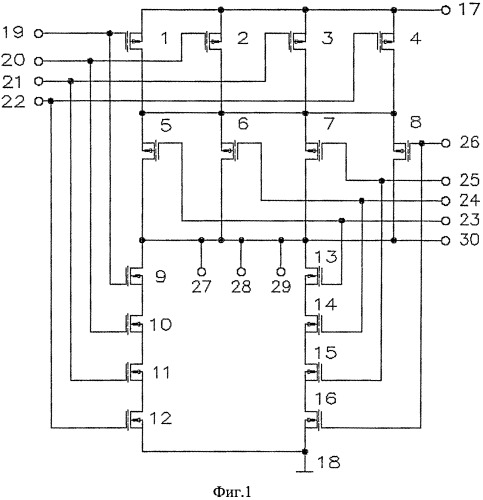

Показать всеИзобретение относится к вычислительной технике и может быть использовано для реализации цифровых схем высокой надежности. Технический результат заключается в повышении надежности элемента при отказах транзистора за счет обеспечения сохранения вида реализуемой логической функции при однократных константных отказах входов элемента или транзисторов. Устройство содержит 8 КМДП транзисторов проводимости n-типа (1-8) и 8 КМДП транзисторов проводимости p-типа (9-16), которые включены между шиной питания (17) и нулевой шиной (18), на затворы которых подаются входные сигналы (19-26). В итоге на выходах элемента (27-30) получаем базисную логическую функцию Z = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) ⋅ ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) , которая при условии, что X1=X1.1=X1.2=X1.3=X1.4 и X2=X2.1=X2.2=X2.3=X2.4, реализует функцию 2И-НЕ с четырехкратной избыточностью, что близко к подходу «учетверенной логики» (логики с переплетением). Устройство сохраняет вид реализуемой им функции при однократных константных отказах входов либо транзисторов и может использоваться при появлении неисправностей, удовлетворяющих заданным моделям отказов без проведения дополнительных процедур реконфигурирования. 1 ил.

Реферат

Изобретение относится к вычислительной технике и может использоваться для реализации цифровых схем, имеющих повышенные требования по надежности, в частности в авиационной и космической областях промышленности.

Известен логический элемент 2И-НЕ (см. Титце У., Шенк К. Полупроводниковая схемотехника. 12-е изд. Том 1: Пер. с нем. - М.: ДМК Пресс, 2008, с.709, рис.7.30) на КМДП-транзисторах, содержащий первый и второй транзисторы проводимости n-типа, включенные параллельно, третий и четвертый транзисторы проводимости p-типа, включенные последовательно. Первый и второй транзисторы включены между шиной питания и выходной шиной, третий и четвертый транзисторы включены между выходной и нулевой шинами, стоки первого и второго транзисторов n-типа соединены с выходной шиной, истоки первого и второго транзисторов n-типа соединены с шиной питания, сток третьего транзистора p-типа подключен к выходной шине, исток третьего транзистора p-типа подключен к стоку четвертого транзистора p-типа, исток четвертого транзистора p-типа подключен к нулевой шине, затворы первого и четвертого транзисторов соединены с первой входной шиной, а затворы второго и третьего транзисторов соединены со второй входной шиной.

Недостатком известного элемента является выход его из строя при однократных константных отказах входов и транзисторов, что ограничивает использование элемента в неремонтируемой аппаратуре при повышенных требованиях к ее отказоустойчивости.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является функционально-полный толерантный элемент (RU 2438234 C1, 27.12.2011) на КМДП-транзисторах, содержащий первый, второй, третий, четвертый транзисторы с проводимостью n-типа, пятый, шестой, седьмой, восьмой транзисторы с проводимостью p-типа, четыре входные шины и одну выходную, шину питания и нулевую шину, истоки первого и третьего транзисторов с проводимостью n-типа подключены к шине питания, истоки шестого и восьмого транзисторов с проводимостью p-типа подключены к нулевой шине, затворы первого и пятого транзисторов подключены к первой входной шине, затворы второго и седьмого транзисторов подключены к третьей входной шине, затворы третьего и шестого транзисторов подключены к второй входной шине, затворы четвертого и шестого транзисторов подключены к четвертой входной шине, сток первого транзистора с проводимостью n-типа подключен к истоку второго транзистора, сток третьего транзистора с проводимостью n-типа подключен к истоку четвертого транзистора, при этом стоки первого и третьего транзисторов с проводимостью n-типа и истоки второго и четвертого транзисторов с проводимостью n-типа соединены между собой, стоки второго и четвертого транзисторов с проводимостью n-типа и стоки пятого и седьмого транзисторов подключены к выходной шине, исток пятого транзистора с проводимостью p-типа подключен к стоку шестого транзистора с проводимостью p-типа, исток седьмого транзистора с проводимостью p-типа подключен к стоку восьмого транзистора с проводимостью p-типа. Данная схема реализует логическую функцию Y = X 1 ¯ X 2 ¯ ∨ X 3 ¯ X 4 ¯ и обладает свойством сохранения функциональной полноты реализуемой ею функции, при однократных константных отказах входов и транзисторов. Данное устройство принято за прототип.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения: КМДП-транзисторы, шина питания и нулевая шина.

Недостатком известного устройства, принятого за прототип, является изменение вида реализуемой функции при однократных константных отказах входов и транзисторов, что требует проведения операции реконфигурации для использования остаточного базиса, образованного отказами. Это требует построения внешней системы, которая будет осуществлять данную операцию.

Задачей изобретения является разработка элемента, реализующего логическую функцию, вид которой будет сохраняться при однократных константных отказах внешних входов и транзисторов.

Поставленная задача была решена за счет того, что в заявляемом устройстве, включающем первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой транзисторы с проводимостью n-типа, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый транзисторы с проводимостью p-типа, восемь входных шин, четыре выходных, шину питания и нулевую шину, истоки первого, второго, третьего и четвертого транзисторов с проводимостью n-типа подключены к шине питания, истоки двенадцатого и шестнадцатого транзисторов с проводимостью p-типа подключены к нулевой шине, сток первого транзистора подключен к истоку пятого транзистора, сток второго транзистора подключен к истоку шестого транзистора, сток третьего транзистора подключен к истоку седьмого транзистора, сток четвертого транзистора подключен к истоку восьмого транзистора, стоки пятого, шестого, седьмого и восьмого транзисторов с проводимостью n-типа соединены между собой и подключены к выходной шине, стоки девятого и тринадцатого транзисторов также подключены к выходной шине, исток девятого транзистора подключен к стоку десятого транзистора, исток десятого транзистора подключен к стоку одиннадцатого транзистора, исток одиннадцатого транзистора подключен к стоку двенадцатого транзистора, исток тринадцатого транзистора подключен к стоку четырнадцатого транзистора, исток четырнадцатого транзистора подключен к стоку пятнадцатого транзистора, исток пятнадцатого транзистора подключен к стоку шестнадцатого транзистора, затворы первого и девятого транзисторов подключены к первой входной шине, затворы второго и десятого транзисторов подключены ко второй входной шине, затворы третьего и одиннадцатого транзисторов подключены к третьей входной шине, затворы четвертого и двенадцатого транзисторов подключены к четвертой входной шине, затворы пятого и тринадцатого транзисторов подключены к пятой входной шине, затворы шестого и четырнадцатого транзисторов подключены к шестой входной шине, затворы седьмого и пятнадцатого транзисторов подключены к седьмой входной шине, затворы восьмого и шестнадцатого транзисторов подключены к восьмой входной шине.

Признаки заявляемого технического решения, отличительные от прототипа, состоят в том, что оно содержит первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой транзисторы с проводимостью n-типа, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый транзисторы с проводимостью p-типа, восемь входных шин, четыре выходных, истоки первого, второго, третьего и четвертого транзисторов с проводимостью n-типа подключены к шине питания, истоки двенадцатого и шестнадцатого транзисторов с проводимостью p-типа подключены к нулевой шине, сток первого транзистора подключен к истоку пятого транзистора, сток второго транзистора подключен к истоку шестого транзистора, сток третьего транзистора подключен к истоку седьмого транзистора, сток четвертого транзистора подключен к истоку восьмого транзистора, стоки пятого, шестого, седьмого и восьмого транзисторов с проводимостью n-типа соединены между собой и подключены к выходной шине, стоки девятого и тринадцатого транзисторов также подключены к выходной шине, исток девятого транзистора подключен к стоку десятого транзистора, исток десятого транзистора подключен к стоку одиннадцатого транзистора, исток одиннадцатого транзистора подключен к стоку двенадцатого транзистора, исток тринадцатого транзистора подключен к стоку четырнадцатого транзистора, исток четырнадцатого транзистора подключен к стоку пятнадцатого транзистора, исток пятнадцатого транзистора подключен к стоку шестнадцатого транзистора, затворы первого и девятого транзисторов подключены к первой входной шине, затворы второго и десятого транзисторов подключены ко второй входной шине, затворы третьего и одиннадцатого транзисторов подключены к третьей входной шине, затворы четвертого и двенадцатого транзисторов подключены к четвертой входной шине, затворы пятого и тринадцатого транзисторов подключены к пятой входной шине, затворы шестого и четырнадцатого транзисторов подключены к шестой входной шине, затворы седьмого и пятнадцатого транзисторов подключены к седьмой входной шине, затворы восьмого и шестнадцатого транзисторов подключены к восьмой входной шине.

Отличительные признаки в сочетании с известными позволяют синтезировать элемент, сохраняющий вид реализуемой им функции при отказах внешних входов и транзисторов.

При дискретном исполнении в качестве КМДП транзисторов с проводимостью n-типа могут использоваться КП301, IRF7304, а в качестве КМДП транзисторов с проводимостью p-типа КП302, IRF7311 или любые другие.

Элемент может быть реализован в интегральном исполнении и использоваться в качестве универсального базиса для программируемых логических интегральных схем (ПЛИС), так как существующие базисные элементы при отказах в матрице коммутаций не обладают способностью к сохранению вида реализуемой ими функции. При этом предполагается, что входы и выход элемента имеют четырехкратную избыточность. В итоге элемент реализует функцию Z = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) ⋅ ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) . В дальнейшем выходы элемента можно объединять с использованием мажоритарных элементов.

На фиг.1 приведена принципиальная электрическая схема заявляемого логического элемента.

Таблица истинности предлагаемого элемента приведена в таблице 1.

| Таблица 1 | |||

| Таблица истинности заявляемого устройства | |||

| № набора | Входы | Выход Z=Z1.1=Z1.2=Z1.3=Z1.4 | |

| X1=X1.1=X1.2=X1.3=X1.4 | X2=X2.1=X2.2=X2.3=X2.4 | ||

| 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 2 | 1 | 0 | 1 |

| 3 | 1 | 1 | 0 |

Таким образом, заявляемое устройство обеспечивает реализацию функции 2И-НЕ с четырехкратной избыточностью.

Покажем, что заявляемое устройство обеспечивает сохранение вида реализуемой им функции при любом однократном константном отказе входа. Возможны 16 случаев отказов, так как элемент имеет 8 входов. Полная группа событий включает следующие реализации:

1. Константа «1» на входе Х1.1. Тогда при условии, что X1=X1.1=X1.2=X1.3=X1.4 и X2=X2.1=X2.2=X2.3=X2.4, функция примет вид Z 1 = ( 0 ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) ⋅ ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

2. Константа «0» на входе Х1.1. Тогда левая конъюнкция будет равна единице и при условии, что X1=X1.1=X1.2=X1.3=X1.4 и X2=X2.1=X2.2=X2.3=X2.4, функция примет вид Z 2 = 1 ⋅ ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

3. Константа «1» на входе X1.2. Тогда при условии, что X1=X1.1=X1.2=X1.3=X1.4 и X2=X2.1=X2.2=X2.3=X2.4, функция примет вид Z 3 = ( X 1.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) ⋅ ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

4. Константа «0» на входе X1.2. Получим функцию Z 4 = ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

5. Константа «1» на входе Х1.3. Получим функцию Z 5 = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) ⋅ ( X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

6. Константа «0» на входе Х1.3. Получим функцию Z 6 = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

7. Константа «1» на входе Х1.4. Получим функцию Z 7 = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) ⋅ ( X 2.3 ¯ ∨ X 1.3 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

8. Константа «0» на входе Х1.4. Получим функцию Z 8 = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

9. Константа «1» на входе Х2.1. Получим функцию Z 9 = ( X 1.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) ⋅ ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

10. Константа «0» на входе Х2.1. Функция примет вид Z 10 = ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

11. Константа «1» на входе Х2.2. Функция примет вид Z 11 = ( X 1.1 ¯ ∨ X 1.2 ¯ ∨ X 2.1 ¯ ) ⋅ ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

12. Константа «0» на входе Х2.2. Функция примет вид Z 12 = ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

13. Константа «1» на входе X2.3 Функция примет вид Z 13 = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) ( X 1.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

14. Константа «0» на входе X2.3. Функция примет вид Z 14 = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

15. Константа «1» на входе Х2.4. Функция примет вид Z 15 = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) ⋅ ( X 1.3 ¯ ∨ X 1.4 ¯ ∨ X 2.3 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

16.Константа «0» на входе Х2.4. Функция примет вид Z 16 = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

Как видно, во всех случаях внешних отказов входов реализуется заданная логическая функция.

Кроме того, легко доказать, что элемент толерантен к инверсии входных переменных. Рассмотрим, например, инверсию переменной Х1.1. Тогда функция примет вид Z = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) ⋅ ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯

Аналогичная ситуация будет происходить и в случае инверсии остальных входных шин. Поэтому элемент может парировать одиночные сбои, которые могут происходить на входных линиях.

Рассмотрим работу элемента при однократных константных отказах транзисторов. Для КМДП транзисторов возможны два случая константных отказов - это константа единицы, которая эквивалентна пробою связи сток-исток или постоянно включенному затвору, и константа нуля, которая эквивалентна обрыву связи сток-исток или обрыву затвора. Таким образом, возможны 32 случая отказа. Полная группа событий включает следующие реализации:

1. Пробой цепи сток-исток (или постоянно включенный затвор) первого транзистора.

2. Обрыв цепи сток-исток (или обрыв затвора) первого транзистора.

3. Пробой цепи сток-исток (или постоянно включенный затвор) второго транзистора.

4. Обрыв цепи сток-исток (или обрыв затвора) второго транзистора.

5. Пробой цепи сток-исток (или постоянно включенный затвор) третьего транзистора.

6. Обрыв цепи сток-исток (или обрыв затвора) третьего транзистора.

7. Пробой цепи сток-исток (или постоянно включенный затвор) четвертого транзистора.

8. Обрыв цепи сток-исток (или обрыв затвора) четвертого транзистора.

9. Пробой цепи сток-исток (или постоянно включенный затвор) пятого транзистора.

10. Обрыв цепи сток-исток (или обрыв затвора) пятого транзистора.

11. Пробой цепи сток-исток (или постоянно включенный затвор) шестого транзистора.

12. Обрыв цепи сток-исток (или обрыв затвора) шестого транзистора.

13. Обрыв цепи сток-исток (или обрыв затвора) седьмого транзистора.

14. Пробой цепи сток-исток (или постоянно включенный затвор) седьмого транзистора.

15. Обрыв цепи сток-исток (или обрыв затвора) восьмого транзистора.

16. Пробой цепи сток-исток (или постоянно включенный затвор) восьмого транзистора.

17. Пробой цепи сток-исток (или постоянно включенный затвор) девятого транзистора.

18. Обрыв цепи сток-исток (или обрыв затвора) девятого транзистора.

19. Пробой цепи сток-исток (или постоянно включенный затвор) десятого транзистора.

20. Обрыв цепи сток-исток (или обрыв затвора) десятого транзистора.

21. Пробой цепи сток-исток (или постоянно включенный затвор) одиннадцатого транзистора.

22. Обрыв цепи сток-исток (или обрыв затвора) одиннадцатого транзистора.

23. Пробой цепи сток-исток (или постоянно включенный затвор) двенадцатого транзистора.

24. Обрыв цепи сток-исток (или обрыв затвора) двенадцатого транзистора.

25. Пробой цепи сток-исток (или постоянно включенный затвор) тринадцатого транзистора.

26. Обрыв цепи сток-исток (или обрыв затвора) тринадцатого транзистора.

27. Пробой цепи сток-исток (или постоянно включенный затвор) четырнадцатого транзистора.

28. Обрыв цепи сток-исток (или обрыв затвора) четырнадцатого транзистора.

29. Обрыв цепи сток-исток (или обрыв затвора) пятнадцатого транзистора.

30. Пробой цепи сток-исток (или постоянно включенный затвор) пятнадцатого транзистора.

31. Обрыв цепи сток-исток (или обрыв затвора) шестнадцатого транзистора.

32. Пробой цепи сток-исток (или постоянно включенный затвор) шестнадцатого транзистора.

Причем в данном случае необходимо рассматривать как функцию подключения к шине питания Z + = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) ⋅ ( X 1.3 ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) , так и функцию подключения к шине ноль вольт Z − = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) ∨ ( X 1.3 ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) .

1. Пробой цепи сток-исток (или постоянно включенный затвор) первого транзистора. В данном случае истоки пятого, шестого, седьмого и восьмого транзисторов будут подключены к шине питания, и функция Z+ примет вид Z 1 + = ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ . При этом функция подключения к нулевой шине не изменится. Ортогональность функций Z1+ и Z1- не будет нарушена. Таким образом, элемент сохраняет вид реализуемой им функции.

2. Обрыв цепи сток-исток (или обрыв затвора) первого транзистора. В данном случае функция Z+ примет вид Z 2 + = ( X 2.1 ¯ ∨ X 1.2 ¯ ∨ X 2.2 ¯ ) ⋅ ( X 1.3 ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ . При этом функция подключения к нулевой шине не изменится, но ортогональность функций Z2+ и Z2- не будет нарушена. Таким образом, элемент сохраняет вид реализуемой им функции.

3. Пробой цепи сток-исток (или постоянно включенный затвор) второго транзистора. Функция Z+ примет вид Z 3 + = ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

4. Обрыв цепи сток-исток (или обрыв затвора) второго транзистора. Функция примет вид Z 4 + = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 2.2 ¯ ) ⋅ ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

5. Пробой цепи сток-исток (или постоянно включенный затвор) третьего транзистора. Функция примет вид Z 5 + = ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

6. Обрыв цепи сток-исток (или обрыв затвора) третьего транзистора. Функция примет вид Z 6 + = ( X 1.1 ¯ ∨ X 2.1 ¯ ∨ X 2.2 ¯ ) ⋅ ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) = X 1 ¯ ∨ X 2 ¯ .

7. Пробой цепи сток-исток (или постоянно включенный затвор) четвертого транзистора. Функция примет вид Z 7 + = ( X 1.3 ¯ ∨ X 2.3 ¯ ∨ X 1.4 ¯ ∨ X 2.4 ¯ ) =