Способ цифровой генерации непрерывного случайного процесса произвольной длины

Иллюстрации

Показать всеИзобретение относится к способам создания широкополосных случайных сигналов с заданными собственными спектральными плотностями мощности при испытаниях аппаратуры на вибростойкость к воздействиям случайной вибрации. Техническим результатом является повышение быстродействия преобразования с быстрой петлей коррекции. В способе генерируют непрерывный случайный процесс произвольной и заданной длины с использованием дискретных цифровых преобразований для управления несколькими вибростендами при их испытаниях с использованием циклически меняющихся буферов для доступа к памяти DMA. 6 ил.

Реферат

Изобретение относится к способам создания широкополосных случайной процессов с заданными собственными спектральными плотностями мощности и может быть использовано в приборостроении, машиностроении, вычислительной технике для создания, в частности, многоканальных автоматических систем, в испытаниях на вибростойкость к воздействиям случайной вибрации и т.д.

Генерация во временной области случайного сигнала x(t), имеющего нормальный закон распределения амплитуд, производится по известному алгоритму («Автоматическое управление вибрационными испытаниями», Библиотека по автоматике, вып. 579, М., Энергия, 1978 г.) путем формирования во временной области на основе заданного спектра амплитуд последовательности (временного блока a 1) вещественных чисел a 1i (i=0, 1, …, N-1) в форме разложения Райса-Пирсона с шагом дискретизации Δt [сек] и преобразования полученной последовательности в непрерывный во времени случайный сигнал длиной TБ=N·Δt=1/Δf [сек], обратно пропорциональной шагу квантования спектра амплитуд сигнала по частоте Δf.

Все названные признаки присутствуют в предлагаемом способе. Как правило, при виброиспытаниях реальных объектов требуется реализация случайных процессов значительной длины, что создает проблемы с управлением в реальном времени с быстрой петлей коррекции.

Предлагаемым изобретением решается задача генерирования непрерывного случайного процесса произвольной заданной длины легко реализуемым на стандартном однопроцессорном компьютере методом дискретных цифровых преобразований, не требующим большого объема вычислений, времени и памяти, что существенно при создании систем управления в реальном времени с быстрой петлей коррекции, например, для управления несколькими вибростендами при испытаниях.

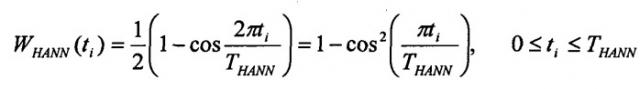

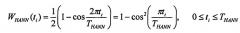

Предлагается способ формирования непрерывного случайного процесса произвольной длины путем цифровой генерации во временной области на основе заданного спектра амплитуд сигнала последовательностей вещественных чисел a ri (i=1, 2, …; i=0, 1, …, N-1) в форме разложения Райса-Пирсона с шагом дискретизации Δt [сек] (временных блоков a r, длиной TБ=NΔt); построения косинусоидального окна Ханна на длине THANN=(4·n-3) точек (n<<N, например, n=N/10):

;

формирования случайного процесса из последовательности следующих друг за другом временных блоков a r (r=1, 2, …), состыкованным по последним a r,N-1 и первым a r+1.0 точкам блоков a r и a r+1 соответственно по следующему алгоритму: в конце блока a r (r=1, 2, …) и в начале следующего блока a r+1 выделяют последовательности точек, длиной n, к концу блока a r добавляют (n-1) точек, симметричных последним n точкам блока a r, умноженным на вторую половину окна Ханна, к началу блока a r+1 добавляют (n-1) точек, симметричных первым n точкам блока a r+1, умноженным на левую половину окна Ханна, полученные в блоках a r и a r+1 последовательности складывают для получения суммарной последовательности, производят замену последовательностей точек блоков так, что последние n точек блока a r заменяют первыми n точками суммарной последовательности, первые n точек следующего блока a r+1 заменяют последними n точками суммарной последовательности; создания для формирования на выходе из системы управления из отдельных следующих друг за другом блоков a r непрерывного случайного сигнала цифрового механизма "ping-pong": в памяти компьютера организуют два буфера длиной N, в один из которых заносят сгенерированный блок данных a r, который затем контроллером прямого доступа к памяти (DMA) без участия центрального процессора передается в память цифроаналогового преобразователя (ЦАП). За время выдачи первого блока a r на выход ЦАП центральный процессор генерирует следующий блок данных a r+1, осуществляет стыковку его начала с концом предыдущего a r и переносит во второй буфер, который, в свою очередь, будет передан в ЦАП через DMA-канал. Затем буфера автоматически циклически меняются местами, и на выходе ЦАП генерируется непрерывный во времени случайный сигнал произвольной длины.

Отличительным признаком предлагаемого способа является:

построение косинусоидального окна Ханна на длине THANN=(4·n-3) точек (n<<N):

;

формирование случайного процесса из последовательности следующих друг за другом временных блоков a r (r=1, 2, …), состыкованным по последним a r,N-1 и первым a r+1.0 точкам блоков a r и a r+1 соответственно по следующему алгоритму: в конце блока a r (r=1, 2, …) и в начале следующего блока a r+1 выделяют последовательности точек, длиной n, к концу блока a r добавляют (n-1) точек, симметричных последним n точкам блока a r, умноженным на вторую половину окна Ханна, к началу блока a r+1 добавляют (n-1) точек, симметричных первым n точкам блока a r+1, умноженным на левую половину окна Ханна, полученные в блоках a r и a r+1 последовательности складывают для получения суммарной последовательности, производят замену последовательностей точек блоков так, что последние n точек блока a r заменяют первыми n точками суммарной последовательности, первые n точек следующего блока a r+1 заменяют последними n точками суммарной последовательности; создание для формирования на выходе из системы управления из отдельных следующих друг за другом блоков a r непрерывного случайного сигнала цифрового механизма "ping-pong": в памяти компьютера организуют два буфера длиной N, в один из которых заносят сгенерированный блок данных a r, который затем контроллером прямого доступа к памяти (DMA) без участия центрального процессора передается в память цифроаналогового преобразователя (ЦАП). За время выдачи первого блока a r на выход ЦАП центральный процессор генерирует следующий блок данных a r+1, осуществляет стыковку его начала с концом предыдущего a r и переносит во второй буфер, который, в свою очередь, будет передан в ЦАП через DMA-канал. Затем буферы автоматически циклически меняются местами, и на выходе ЦАП генерируется непрерывный во времени случайный сигнал произвольной длины.

Благодаря наличию указанного отличительного признака в совокупности с известными приобретается возможность формирования непрерывных случайных процессов x(t) заданной произвольной длины.

В результате поиска по источникам патентной и научно-технической информации решений, содержащих аналогичные признаки, не обнаружено.

Таким образом, можно сделать заключение о том, что предложенный способ неизвестен на уровне техники и, следовательно, соответствует критерию «патентоспособности».

Предложенный способ может найти применение везде, где возникает необходимость в непрерывных случайных процессах произвольной длины, что позволяет сделать вывод о соответствии критерию «Промышленная применимость».

Способ реализуется следующим образом. В конце блока a r (для примера взято r=1) и в начале следующего a r+1 выделяют последовательности длиной n точек (как правило, значение n является незначительным по отношению ко всей длине блока N точек, например, в данном примере n=N/10=10), на которых строится алгоритм стыковки фаз (Фиг.1) На длине THANN=(4·n-3) точек вычисляют косинусоидальное окно Ханна (Фиг.2):

.

К концу блока a r,N-1 добавляют (n-1) точек, симметричных последним n точкам блока: a 1,N= a 1,N-2, …, a 1,N+n-2=a 1,N-n. Умножают полученную последовательность на вторую половину окна Ханна (Фиг.3). К концу последующего блока a r+1 (точке a 2,0) добавляют (n-1) точек, симметричных первым n точкам блока: a 2,-1=a 2,1, …, a 2,1-n=a 2,n-1. Умножают полученную последовательность на первую половину окна Ханна (Фиг.4). Преобразованные последовательности (Фиг.3 и 4) складывают в суммарную последовательность (Фиг.5). Точками суммарной последовательности заменяют точки исходных блоков точек блоков a r и a r+1 так, что последние n точек блока a r заменяют первыми n точками суммарной последовательности, а первые n точек следующего блока a r+1 заменяют последними n точками суммарной последовательности (Фиг.6).

Способ цифровой генерации непрерывного случайного процесса произвольной длины, включающий цифровую генерацию во временной области на основе заданного спектра амплитуд сигнала последовательностей вещественных чисел ari (r=1, 2, …; i=0, 1, …, N-1) в форме разложения Райса-Пирсона с шагом дискретизации Δt [сек] временных блоков ar, длиной TБ=NΔt, отличающийся тем, что включает построение на длине THANN=(4·n-3) точек (n<<N) косинусоидального окна Ханна: ;формирование случайного процесса из последовательности следующих друг за другом временных блоков ar (r=1, 2, …), состыкованным по последним ar,N-1 и первым ar+1.0 точкам блоков ar и ar+1 соответственно, по следующему алгоритму: в конце блока ar (r=1, 2, …) и в начале следующего блока ar+1 выделяют последовательности точек, длиной n, к концу блока ar добавляют (n-1) точек, симметричных последним n точкам блока ar, умноженным на вторую половину окна Ханна, к началу блока ar+1 добавляют (n-1) точек, симметричных первым n точкам блока ar+1, умноженным на левую половину окна Ханна, полученные в блоках ar и ar+1 последовательности складывают для получения суммарной последовательности, производят замену последовательностей точек блоков так, что последние n точек блока ar заменяют первыми n точками суммарной последовательности, первые n точек следующего блока ar+1 заменяют последними n точками суммарной последовательности; создание для формирования на выходе из системы управления из отдельных следующих друг за другом блоков ar непрерывного случайного сигнала цифрового механизма, для чего в памяти компьютера организуют два буфера длиной N, в один из которых заносят сгенерированный блок данных ar, который затем контроллером прямого доступа к памяти (DMA) без участия центрального процессора передается в память цифроаналогового преобразователя (ЦАП), за время выдачи первого блока ar на выход ЦАП центральный процессор генерирует следующий блок данных ar+1, осуществляет стыковку его начала с концом предыдущего ar и переносит во второй буфер, который, в свою очередь, будет передан в ЦАП через DMA-канал, затем буферы автоматически циклически меняются местами, и на выходе ЦАП генерируется непрерывный во времени случайный сигнал произвольной длины.