Устройство для измерения защищенности сигнала от помех

Иллюстрации

Показать всеИзобретение относится к радиотехнике и может быть использовано при оценке систем связи с широкополосными сигналами. Технический результат заключается в повышении точности измерения защищенности сигнала от помех. В устройстве для измерения защищенности сигнала от помех взаимодействие сигнала и помехи в частотно-временной области оценивается с помощью коэффициента взаимной корреляции искаженного и эталонного сигналов g, а искажения сигнала, неизбежно возникающие при принятии мер по подавлению помехи в тракте приема, - с помощью коэффициента взаимной корреляции помехи и эталонного сигнала λ. В качестве комплексного показателя Ξ степени защищенности сигнала от помех (с учетом эффективности принимаемых мер по подавлению помех) предлагается использовать отношение указанных коэффициентов, т.e. Ξ = g λ . Чем больше воздействие помехи на сигнал, тем больше значение коэффициента взаимной корреляции помехи и эталонного сигнала λ, а следовательно, меньше значение комплексного показателя Ξ степени защищенности сигнала от помех. Подавление помехи в спектре сигнала приводит к уменьшению как знаменателя, так и числителя в выражении для Ξ , так как при этом растет отличие между искаженным и эталонным (опорным) сигналами. 1 ил.

Реферат

Изобретение относится к радиотехнике, в частности к устройствам измерения защищенности сигнала от помех и может быть использовано при оценке систем связи с широкополосными сигналами.

Известно устройство для измерения защищенности сигнала от помех, содержащее приемник, формирователь сигнала, формирователь стробирующих импульсов, два перемножителя, два интегратора, два квадратора, сумматор, нормирующий блок, ключ и преобразователь сигнала (см. USSR №1376249, 1986 г.).

Недостатком данного устройства является низкая точность измерения вследствие отсутствия учета инструментальных погрешностей, обусловленных искажениями сигнала в измерительном тракте.

Наиболее близким по технической сущности к заявляемому изобретению является устройство для измерения защищенности сигнала от помех, содержащее кнопку «Пуск», одновибратор, формирователь стробирующих импульсов, инвертор, переключатель, регистр памяти, блок деления, формирователь эталонного сигнала, два перемножителя, фазосдвигатель, два интегратора, два квадратора, сумматор, ключ, преобразователь сигнала, нормирующий блок и приемник (см. USSR №1570006, 1988 г.).

Недостатком данного устройства является низкая точность результатов измерения защищенности сигнала от помех вследствие принятия мер по повышению помехозащищенности радиотехнической системы, в частности при режекции пораженного помехой участка спектра.

Задачей предлагаемого изобретения является разработка устройства для измерения защищенности сигнала от помех, позволяющего повысить точность результата измерения защищенности сигнала от помех.

Технический результат, который может быть получен с помощью предлагаемого изобретения, сводится к повышению точности измерения защищенности сигнала от помех.

Технический результат достигается с помощью устройства для измерения защищенности сигнала от помех, содержащего кнопку «Пуск», одновибратор, формирователь эталонного сигнала, формирователь стробирующих импульсов, переключатель, приемник, блок разделительных фильтров, амплитудный детектор, N блоков канальных детекторов, N блоков сравнения, N блоков канальных ключей, суммирующий фильтр, первый и второй перемножители, фазовращатель, первый и второй интеграторы, первый и второй квадраторы, сумматор, нормирующий блок, измеритель мощности, стробирующий ключ, аналогово-цифровой преобразователь, регистр памяти, инвертор, блок деления и блок ключей, причем выход кнопки «Пуск» подключен к входу одновибратора, входу формирователя эталонного сигнала и входу формирователя стробирующих импульсов, выход одновибратора подключен к входу инвертора и первому входу переключателя, первый выход формирователя эталонного сигнала подключен к входу фазовращателя и первому входу первого перемножителя, второй выход формирователя эталонного сигнала подключен к входу измерителя мощности, первый выход формирователя стробирующих импульсов подключен к первым управляющим входам первого и второго интеграторов, второй выход формирователя стробирующих импульсов подключен к управляющему входу стробирующего ключа, третий выход формирователя стробирующих импульсов подключен к управляющему входу аналогово-цифрового преобразователя, четвертый выход формирователя стробирующих импульсов подключен ко вторым управляющим входам первого и второго интеграторов, первый выход переключателя подключен к входу регистра памяти, второй выход переключателя подключен к первому входу блока деления, на вход приемника поступает сигнал из радиолинии, выход приемника подключен к входу блока разделительных фильтров и входу амплитудного детектора, N выходов блока разделительных фильтров подключены к информационным входам N блоков канальных ключей и входам N блоков канальных детекторов соответственно, выход амплитудного детектора подключен к первым входам N блоков сравнения, выходы N блоков канальных детекторов подключены ко вторым входам N блоков сравнения соответственно, выходы N блоков сравнения подключены к N входам блока ключей, выходы N блоков канальных ключей подключены к N входам суммирующего фильтра, выход суммирующего фильтра подключен ко второму входу первого перемножителя и первому входу второго перемножителя, выход первого перемножителя подключен к информационному входу первого интегратора, выход второго перемножителя подключен к информационному входу второго интегратора, выход фазовращателя подключен ко второму входу второго перемножителя, выход первого интегратора подключен к входу первого квадратора, выход второго интегратора подключен к входу второго квадратора, выход первого квадратора подключен к первому входу сумматора, выход второго квадратора подключен ко второму входу сумматора, выход сумматора подключен к первому входу нормирующего блока, выход нормирующего блока подключен к информационному входу стробирующего ключа, выход измерителя мощности подключен ко второму входу нормирующего блока, выход стробирующего ключа подключен к информационному входу аналогово-цифрового преобразователя, выход аналогово-цифрового преобразователя подключен ко второму входу переключателя, выход регистра памяти подключен ко второму входу блока деления, выход инвертора подключен ко вторым управляющим входам N блоков канальных ключей и управляющему входу блока ключей, на выход устройства данные поступают с блока деления, N выходов блока ключей подключены к первым управляющим входам N блоков канальных ключей.

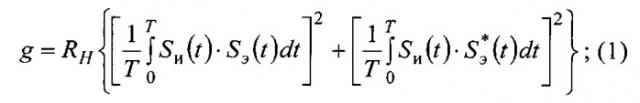

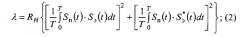

Взаимодействие сигнала и помехи в частотно-временной области оценивается с помощью коэффициента взаимной корреляции искаженного и эталонного сигналов g, а искажения сигнала, неизбежно возникающие при принятии мер по подавлению помехи в тракте приема, - с помощью коэффициента взаимной корреляции помехи и эталонного сигнала λ. Аналитически данные коэффициенты взаимной корреляции определяются выражениями

где Sи(t) - аналитическое описание искаженного в измерительном тракте сигнала; Sэ(t) аналитическое описание эталонного (опорного) сигнала; S э * ( t ) - функция, сопряженная по Гильберту с Sэ(t) (соответствует фазовому сдвигу сигнала на 90° по отношению к исходному); Sп(t) - аналитическое описание помехи; T - период эталонного сигнала; RH - нормирующий коэффициент, обеспечивающий равенство g=1(λ=1) при полном совпадении спектров искаженного сигнала (помехи) и эталонного сигнала.

В качестве комплексного показателя Ξ степени защищенности сигнала от помех (с учетом эффективности принимаемых мер по подавлению помех) предлагается использовать отношение указанных коэффициентов, т.е. Ξ = g λ . Чем больше воздействие помехи на сигнал, тем больше значение коэффициента взаимной корреляции помехи и эталонного сигнала λ, а следовательно, меньше значение комплексного показателя Ξ степени защищенности сигнала от помех.

Подавление помехи в спектре сигнала приводит к уменьшению как знаменателя, так и числителя в выражении для Ξ, так как при этом растет отличие между искаженным и эталонным (опорным) сигналами. Таким образом, предлагаемый показатель позволяет оценить не только защищенность сигнала от помех, но и учесть побочный эффект от принимаемой меры борьбы с помехами.

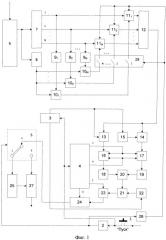

На фиг. 1 изображена блок-схема устройства для измерения защищенности сигнала от помех.

Устройство для измерения защищенности сигнала от помех состоит из кнопки 1 «Пуск», одновибратора 2, формирователя 3 эталонного сигнала, формирователя 4 стробирующих импульсов, переключателя 5, приемника 6, блока 7 разделительных фильтров, амплитудного детектора 8, N блоков 91÷9Ν канальных детекторов, N блоков сравнения 101÷10Ν, N блоков канальных ключей 111÷11N, суммирующего фильтра 12, первого и второго перемножителей 13 и 14, фазовращателя 15, первого и второго интеграторов 16 и 17, первого и второго квадраторов 18 и 19, сумматора 20, нормирующего блока 21, измерителя мощности 22, стробирующего ключа 23, аналогово-цифрового преобразователя 24, регистра памяти 25, инвертора 26, блока деления 27 и блока 28 ключей, причем выход кнопки 1 «Пуск» подключен к входу одновибратора 2, входу формирователя 3 эталонного сигнала, входу формирователя 4 стробирующих импульсов, выход одновибратора 2 подключен к входу инвертора 26 и первому входу переключателя 5, первый выход формирователя 3 эталонного сигнала подключен к входу фазовращателя 15 и первому входу первого перемножителя 13, второй выход формирователя 3 эталонного сигнала подключен к входу измерителя мощности 22, первый выход формирователя 4 стробирующих импульсов подключен к первым управляющим входам первого и второго интеграторов 16 и 17 соответственно, второй выход формирователя 4 стробирующих импульсов подключен к управляющему входу стробирующего ключа 23, третий выход формирователя 4 стробирующих импульсов подключен к управляющему входу аналогово-цифрового преобразователя 24, четвертый выход формирователя 4 стробирующих импульсов подключен ко вторым управляющим входам первого и второго интеграторов 16 и 17 соответственно, первый выход переключателя 5 подключен к входу регистра памяти 25, второй выход переключателя 5 подключен к первому входу блока деления 27, на вход приемника 6 поступает сигнал из радиолинии, выход приемника 6 подключен к входу блока 7 разделительных фильтров и входу амплитудного детектора 8, N выходов блока разделительных фильтров 7 подключены к информационным входам N блоков канальных ключей 111÷11Ν и входам N блоков 91÷9N канальных детекторов соответственно, выход амплитудного детектора 8 подключен к первым входам N блоков сравнения 101÷10N, выходы N блоков 91÷9N канальных детекторов подключены ко вторым входам N блоков сравнения 101÷10Ν соответственно, выходы N блоков сравнения 101÷10Ν подключены к N входам блока 28 ключей, выходы N блоков канальных ключей 111÷11N подключены к N входам суммирующего фильтра 12, выход суммирующего фильтра 12 подключен ко второму входу первого перемножителя 13 и первому входу второго перемножителя 14, выход первого перемножителя 13 подключен к информационному входу первого интегратора 16, выход второго перемножителя 14 подключен к информационному входу второго интегратора 17, выход фазовращателя 15 подключен ко второму входу второго перемножителя 14, выход первого интегратора 16 подключен к входу первого квадратора 18, выход второго интегратора 17 подключен к входу второго квадратора 19, выход первого квадратора 18 подключен к первому входу сумматора 20, выход второго квадратора 19 подключен ко второму входу сумматора 20, выход сумматора 20 подключен к первому входу нормирующего блока 21, выход нормирующего блока 21 подключен к информационному входу стробирующего ключа 23, выход измерителя мощности 22 подключен ко второму входу нормирующего блока 21, выход стробирующего ключа 23 подключен к информационному входу аналогово-цифрового преобразователя 24, выход аналогово-цифрового преобразователя 24 подключен ко второму входу переключателя 5, выход регистра памяти 25 подключен ко второму входу блока деления 27, выход инвертора 26 подключен ко вторым управляющим входам N блоков канальных ключей 111÷11N и управляющему входу блока 28 ключей, на выход устройства поступает информация с блока деления 27, N выходов блока 28 ключей подключены к первым управляющим входам N блоков канальных ключей 111÷11N.

Устройство для измерения защищенности сигнала от помех работает следующим образом.

При нажатии кнопки 1 «Пуск» напряжение через ее контакты подается на входы одновибратора 2, формирователя 3 эталонного сигнала и формирователя 4 стробирующих импульсов для их запуска.

Одиночный импульс с выхода одновибратора 2, имея уровень логической «единицы», поступает на вход переключателя 5, устанавливая его в исходное состояние (замкнуты контакты 1-2) и на вход инвертора 26. После преобразования в инверторе 26 сигнал логического «нуля» подается на вход установки в исходное состояние блока 28 ключей (контакты замкнуты) и на вторые управляющие входы блоков канальных ключей 111÷11Ν для установки их в исходное состояние.

На вход приемника 6 поступает сигнал из радиолинии, с выхода приемника 6 принимаемый сигнал поступает на вход блока 7 разделительных фильтров и вход амплитудного детектора 8. Блок 7 разделительных фильтров обеспечивает разделение спектра принимаемого сигнала на N частотных каналов. Разделенные составляющие сигнала с N выходов блока 7 разделительных фильтров подаются, через N блоков 91÷9Ν канальных детекторов, на первые входы соответствующих N блоков сравнения 101÷10N, на вторые входы которых с выхода амплитудного детектора 8 подается опорное усредненное напряжение принимаемого сигнала.

При превышении опорного напряжения сигналом любого из N каналов, что свидетельствует о наличии мощной сосредоточенной помехи в данном канале, на выходе одного из N блоков сравнения 101÷10Ν, соответствующего данному каналу, появляется напряжение, поступающее через замкнутые ключи блока 28 ключей на первый управляющий вход одного из N блоков канальных ключей 111÷11Ν соответственно для его открытия. Один из N блоков канальных ключей 111÷11Ν, который был открыт, обеспечивает прохождение помехи с соответствующего выхода блока 7 разделительных фильтров на вход суммирующего фильтра 12.

С выхода суммирующего фильтра 12 помеха Sп(t) поступает на второй вход первого и первый вход второго перемножителей 13 и 14 соответственно. Эталонный сигнал Sэ(t) с выхода формирователя 3 эталонного сигнала поступает на первый вход первого перемножителя 13 непосредственно, а на второй вход второго перемножителя 14 - через фазовращатель 15, который осуществляет формирование сигнала S э * ( t ) сопряженного по Гильберту с эталонным сигналом Sэ(t). Результаты перемножения сигналов с выходов первого и второго перемножителей 13 и 14 поступают на информационные входы первого и второго интеграторов 16 и 17 соответственно, предварительно установленных в исходное состояние импульсом с первого выхода формирователя 4 стробирующих импульсов. После интегрирования в течение времени, равного длительности t∈[0, Τ], сигналы с выходов первого и второго интеграторов 16 и 17 поступают через первый и второй квадраторы 18 и 19 на соответствующие входы сумматора 20.

Сигнал, подаваемый с выхода сумматора 20 на первый вход нормирующего блока 21, нормируется к уровню мощности эталонного сигнала, измеренного в измерителе мощности 22, вход которого подключен к выходу формирователя 3 эталонного сигнала. С выхода нормирующего блока 21 сигнал подается на информационный вход стробирующего ключа 23, в котором, при поступлении на его управляющий вход импульса со второго выхода формирователя 4 стробирующих импульсов, осуществляется отсчет результата измерения коэффициента взаимной корелляции помехи и эталонного сигнала λ, описываемого выражением (1).

Сигнал с выхода стробирующего ключа 23, подаваемый на информационный вход аналогово-цифрового преобразователя 24, на управляющий вход которого подаются импульсы с третьего выхода формирователя 4 стробирующих импульсов, преобразуется в цифровую форму и через замкнутые контакты 1-2 переключателя 5 поступает в регистр памяти 25, являясь значением коэффициента взаимной корреляции помехи и эталонного сигнала λ. Стробирующий импульс с четвертого выхода формирователя 4 стробирующих импульсов поступает на вторые управляющие входы первого и второго интеграторов 16 и 17 для сброса их в исходное состояние.

На втором этапе работы устройства, после окончания импульса, формируемого одновибратором 2, на его выходе появляется напряжение логического «нуля», подаваемое на переключатель 5 и инвертор 26. При этом переключатель 5 замыкает контакты 2-3, обеспечивая подключение выхода аналогово-цифрового преобразователя 24 к входу блока деления 27.

С выхода инвертора 26 напряжение логической «единицы» подается на вход блока 28 ключей, отключающих N блоков сравнения 101÷10Ν от N блоков канальных ключей 111÷11Ν. Кроме того, напряжение логической «единицы» подается на блокирующие входы N блоков канальных ключей 111÷11N, обеспечивая неизменность их состояний, установленных на этапе измерения коэффициента взаимной корелляции помехи и эталонного сигнала λ. В этом случае один из блоков канальных ключей 111÷11N, в котором присутствовала помеха, окажется закрытым на период второго этапа измерения. Вследствие этого частотные составляющие эталонного сигнала с выхода блока 7 разделительных фильтров поступают на входы суммирующего фильтра 12 только через те из блоков канальных ключей 111÷11N, которые остались открытыми. Следовательно, сигнал Sи(t) на выходе суммирующего фильтра 12 будет искаженным вследствие режекции участка спектра в диапазоне частот, на котором присутствует сосредоточенная помеха.

Искаженный сигнал Sи(t) с выхода суммирующего фильтра 12 поступает на второй вход первого и первый вход второго перемножителей 13 и 14 соответственно, на первый вход первого и второй вход второго перемножителей 13 и 14 соответственно подается эталонный сигнал Sэ(t) с формирователя 3 эталонного сигнала: на первый перемножитель 13 - непосредственно; на второй перемножитель 14 - через фазовращатель 15. Далее, по аналогии с первым этапом работы устройства, результаты перемножения сигналов Sи(t)·Sэ(t) и S и ( t ) ⋅ S э * ( t ) с выходов первого и второго перемножителей 13 и 14 соответственно поступают на входы первого и второго интеграторов 16 и 17 соответственно, сигналы с выходов первого и второго интеграторов 16 и 17 поступают через первый и второй квадраторы 18 и 19 на соответствующие входы сумматора 20. С выхода сумматора 20 суммарный сигнал, пройдя через нормирующий блок 21 и стробирующий ключ 23, является результатом измерения коэффициента взаимной корреляции искаженного и эталонного сигналов g, описываемого выражением (2).

Данный результат измерения коэффициента взаимной корреляции искаженного и эталонного сигналов g преобразуется в аналогово-цифровом преобразователе 24 в цифровую форму и через замкнутые контакты 2-3 переключателя 5 поступает на первый вход (вход числителя) блока деления 27, на второй вход (вход знаменателя) которого подается информация с выхода регистра памяти 25, являющаяся значением коэффициента взаимной корреляции помехи и эталонного сигнала λ. Результат деления g/λ, являющийся комплексным показателем Ξ степени защищенности сигнала от помех, с блока деления 27 поступает на выход устройства.

Предлагаемое изобретение по сравнению с прототипом и другими известными техническими решениями имеет следующие преимущества:

- Оценка степени взаимодействия сигнала и помехи в частотно-временной области;

- Возможность учета потерь, обусловленных искажением сигнала при использовании основного способа борьбы с сосредоточенными помехами, - режекцией пораженного помехой участка спектра сигнала;

- Значительное увеличении точности результата измерения защищенности сигнала от помех по сравнению с аналогами.

Устройство для измерения защищенности сигнала от помех, содержащее кнопку «Пуск», одновибратор, формирователь эталонного сигнала, формирователь стробирующих импульсов, переключатель, приемник, первый и второй перемножители, фазовращатель, первый и второй интеграторы, первый и второй квадраторы, сумматор, нормирующий блок, стробирующий ключ, аналогово-цифровой преобразователь, регистр памяти, инвертор, блок деления, отличающееся тем, что в данное устройство введен блок разделительных фильтров, амплитудный детектор, N блоков канальных детекторов, N блоков сравнения, N блоков канальных ключей, суммирующий фильтр, измеритель мощности, блок ключей, причем выход кнопки «Пуск» подключен к входу одновибратора, входу формирователя эталонного сигнала и входу формирователя стробирующих импульсов, выход одновибратора подключен к входу инвертора и первому входу переключателя, первый выход формирователя эталонного сигнала подключен к входу фазовращателя и первому входу первого перемножителя, второй выход формирователя эталонного сигнала подключен к входу измерителя мощности, первый выход формирователя стробирующих импульсов подключен к первым управляющим входам первого и второго интеграторов, второй выход формирователя стробирующих импульсов подключен к управляющему входу стробирующего ключа, третий выход формирователя стробирующих импульсов подключен к управляющему входу аналогово-цифрового преобразователя, четвертый выход формирователя стробирующих импульсов подключен ко вторым управляющим входам первого и второго интеграторов, первый выход переключателя подключен к входу регистра памяти, второй выход переключателя подключен к первому входу блока деления, на вход приемника поступает сигнал из радиолинии, выход приемника подключен к входу блока разделительных фильтров и входу амплитудного детектора, N выходов блока разделительных фильтров подключены к информационным входам N блоков канальных ключей и входам N блоков канальных детекторов соответственно, выход амплитудного детектора подключен к первым входам N блоков сравнения, выходы N блоков канальных детекторов подключены ко вторым входам N блоков сравнения соответственно, выходы N блоков сравнения подключены к N входам блока ключей, выходы N блоков канальных ключей подключены к N входам суммирующего фильтра, выход суммирующего фильтра подключен ко второму входу первого перемножителя и первому входу второго перемножителя, выход первого перемножителя подключен к информационному входу первого интегратора, выход второго перемножителя подключен к информационному входу второго интегратора, выход фазовращателя подключен ко второму входу второго перемножителя, выход первого интегратора подключен к входу первого квадратора, выход второго интегратора подключен к входу второго квадратора, выход первого квадратора подключен к первому входу сумматора, выход второго квадратора подключен ко второму входу сумматора, выход сумматора подключен к первому входу нормирующего блока, выход нормирующего блока подключен к информационному входу стробирующего ключа, выход измерителя мощности подключен ко второму входу нормирующего блока, выход стробирующего ключа подключен к информационному входу аналогово-цифрового преобразователя, выход аналогово-цифрового преобразователя подключен ко второму входу переключателя, выход регистра памяти подключен ко второму входу блока деления, выход инвертора подключен ко вторым управляющим входам N блоков канальных ключей и управляющему входу блока ключей, на выход устройства данные поступают с блока деления, N выходов блока ключей подключены к первым управляющим входам N блоков канальных ключей.