Устройство для определения оптимального периода управления техническим состоянием изделия

Иллюстрации

Показать всеИзобретение относится к вычислительной технике, в частности к устройствам контроля, и может быть использовано в опытно-конструкторских работах и практике эксплуатации, где требуется определять оптимальную периодичность технического обслуживания, вычисленную с учетом динамики расходования изделием его надежностного потенциала, и соответствующие этой периодичности значений эксплуатационных характеристик. Технический результат заключается в повышении точности определения значений искомых величин путем реализации математической модели, позволяющей учитывать зависимость функции отказов от времени и от режима использования изделия. Технический результат достигается за счет устройства, которое содержит пять блоков деления, четыре блока нелинейностей, девять блоков умножения, два интегратора, два вычитателя, датчик времени (генератор ступенчатого напряжения), пять сумматоров, мультивибратор, работающий в ждущем режиме, пять элементов задержки, схему ИЛИ, компаратор, триггер, четыре элемента памяти, четыре вентиля. 2 ил.

Реферат

Изобретение относится к вычислительной технике, в частности к устройствам контроля, и может быть использовано в опытно-конструкторских работах и практике эксплуатации изделий, подверженных старению, для определения оптимальных сроков их технического обслуживания.

Известны устройства [3, 4], позволяющие определять оптимальные значения периодов технического обслуживания изделий. Их недостатком является ограниченная область применения, поскольку они не позволяют учитывать фактор старения изделий. Устройства [5, 6] позволяют вычислять значения периодов обслуживания, обеспечивающие получение экстремальных значений эксплуатационно-технических характеристик изделий с учетом фактора их старения. Однако эти устройства не позволяют учитывать разницу в скорости расходования надежностного потенциала при изменении режима функционирования изделия, что снижает точность получаемых результатов. Устройства [7, 8] предназначены для определения оптимальной периодичности контроля и управления техническим состоянием изделий с учетом изменения интенсивности их отказов в зависимости от режима использования. Недостатком устройств [5, 6] является то, что определение значений выходных величин осуществляется без учета фактора старения изделия. По составу функциональных элементов, используемых в заявляемом изобретении, устройства [7, 8] равнозначны, а по составу выходных параметров более близким является устройство [8].

В связи с изложенным, за прототип заявляемого изобретения принято устройство [8], содержащее блок памяти, шесть вентилей, пять сумматоров, мультивибратор, два триггера, два накапливающих сумматора, схему ИЛИ, четыре блока нелинейностей, компаратор, четыре блока умножения, два вычитателя, четыре элемента задержки, четыре элемента памяти, два интегратора и делитель.

Целью заявляемого технического решения является расширение области применения устройства и повышение точности определения значений искомых величин. Цель достигается путем реализации математической модели, позволяющей учитывать зависимость функции отказов от времени и от режима использования изделия. Критерием оптимизации периода технического обслуживания изделия является максимум коэффициента готовности.

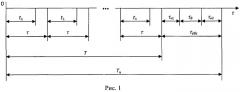

Процесс применения значительного числа различных типов изделий имеет циклический характер. Каждый цикл включает в себя работу изделия в номинальном режиме и нахождение в режиме отдыха. На рисунке 1 представлена диаграмма процесса эксплуатации изделия, включающая в себя:

τ - длительность цикла применения изделия (например, одни сутки);

t1=τKИ - длительность применения изделия в номинальном режиме, KИ - коэффициент использования изделия по назначению, 0<KИ<1. При этом интенсивность отказов изделия имеет значение λ1;

t2=τ-t1 - продолжительность отдыха после применения (например, технические средства предприятий, работающих в одну или две смены, транспортные средства и многое другое). На этом интервале времени интенсивность отказов имеет значение 0<λ2<λ1 [1].

Для поддержания изделия в работоспособном состоянии периодически проводится его техническое обслуживание и затрачивается время τобс. При этом выполняется углубленный контроль состояния в течение времени τк1, проведение регламентных работ и восстановление работоспособности изделия в случае обнаружения отказа, на что расходуется время τв, а по окончании этих работ проводится контрольная проверка состояния изделия в течение времени τк2. Отметим, что контроль технического состояния выполняется в условиях номинального режима работы изделия. Поэтому на интервалах времени τк1 и τк2 интенсивность отказов будет равной λ1. Для проведения ремонтно-восстановительных работ изделие переводится в режим отдыха, что соответствует интенсивности отказов λ2. В связи с изложенным, общая продолжительность технического обслуживания выражается так:

где Р(T), Р(τк1+τк2), Р(τв) - вероятность безотказной работы изделия на соответствующем интервале времени.

Длительность периода обслуживания T (рис. 1) включает в себя множество i = 1 , n ¯ циклов применения длительностью τ каждый, то есть

Продолжительность Tц цикла обслуживания изделия составляет

Вероятность безотказной работы изделия на интервале времени T выражается так:

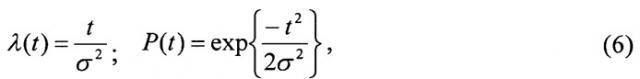

Важным параметром безотказности является интенсивность отказов. Теория и практика эксплуатации широкого класса обслуживаемых изделий показывает, что старение изделий сопровождается увеличением этой интенсивности. Для определения времени безотказной работы таких изделий применим закон распределения Рэлея. При этом интенсивность отказов λ(t) и вероятность безотказной работы изделия P(t) определяются так [2]:

где σ - параметр распределения Рэлея.

В связи с этим имеет место следующее:

Время работоспособного состояния изделия Tф на интервале времени определяется по формуле

Комплексным показателем качества функционирования является коэффициент готовности, выражаемый следующим соотношением:

Проведенные исследования показывают, что существует период обслуживания, при котором KГ(T) имеет глобальный экстремум. В связи с этим, задача определения оптимального периода управления техническим состоянием изделия выражается в следующем виде:

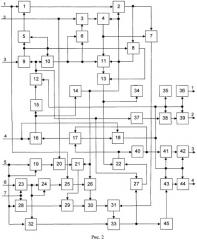

Предложенная математическая модель может быть реализована аппаратурно с помощью устройства, схема которого показана на рисунке 2.

Устройство содержит: первый 1, второй 3, третий 20, четвертый 22 и пятый 25 блоки деления, первый 2, второй 4, третий 21 и четвертый 26 блоки нелинейностей, первый 5, второй 6, третий 7, четвертый 9, пятый 19, шестой 24, седьмой 29, восьмой 30 и девятый 31 блоки умножения, первый 8 и второй 11 интеграторы, первый 10 и второй 33 вычитатели, датчик времени (генератор ступенчатого напряжения) 12, первый 13, второй 23, третий 27, четвертый 28 и пятый 32 сумматоры, мультивибратор 14, первый 15, второй 34, третий 37, четвертый 40 и пятый 45 элементы задержки, схему ИЛИ 16, компаратор 17, триггер 18, первый 35, второй 38, третий 41 и четвертый 43 элементы памяти, первый 36, второй 39, третий 42 и четвертый 44 вентили.

Схемы используемых функциональных блоков устройства представления в [9], в частности элементы памяти могут быть построены по схеме 4-5-1, а блоки нелинейностей по схеме 3-4-2.

Процесс решения задачи (13) имеет итерационный характер. В первом цикле работы (i=1) устройства T=τ, T1=τ1, T2=τ-τ1, а в каждом последующем цикле происходит увеличение параметров T, T1, T2 согласно (2) и (3). Соответственно этому изменяются значения величин Р(T), Tф(T), KГ(T), τобс(T).

Перед началом работы устройства исходные данные: 2 σ 1 2 , 2 σ 2 2 , KИ, τв, τк1, τк2 подаются соответственно на 1, 2, 3, 5, 6, 7 его входы.

Работа начинается с приходом на четвертый вход устройства сигнала «Пуск». Этот сигнал поступает на первый вход триггера 18, переводя его в нулевое состояние. В то же время, сигнал «Пуск», пройдя через схему ИЛИ 16, инициирует генерацию ждущим мультивибратором 14 управляющего воздействия, по которому за время Δt приводятся в исходное состояние (обнуляются) первый 2, второй 4, третий 21 и четвертый 26 блоки нелинейностей, а также первый 8 и второй 11 интеграторы. Кроме того, сигнал «Пуск», задержанный первым элементом задержки 15 на время Δt, запускает датчик времени 12. Этот датчик с шагом τ задает в порядке нарастания последовательность возможных значений τi периода технического обслуживания изделия τi=τi-1+τ, где i=1, 2, 3 …. Начальный сигнал T=τ с выхода датчика времени 12 передается через третий элемент задержки 37 во второй элемент памяти 38, на первые входы третьего сумматора 27 и первого вычитателя 10, а также на второй вход четвертого блока умножения 9. С третьего входа устройства на первый вход блока 9 поступает значение коэффициента использования изделия по назначению KИ. Результат перемножения KИ·τ=t1 с выхода блока 9 передается на вторые входы первого интегратора 8 и первого вычитателя 10, а также на оба входа первого блока умножения 5. Сигнал, соответствующий величине t 1 2 из блока 5 передается на второй вход первого блока деления 1, на первый вход которого с первого входа устройства поступает сигнал 2 σ 1 2 . Этот сигнал поступает и на первый вход пятого блока деления 25. Выходной сигнал t 1 2 / 2 σ 1 2 блока деления 1 передается на первый вход первого блока нелинейности 2, в котором формируется и передается на первые входы третьего блока умножения 7 и первого интегратора 8 значение величины P1(t1). Выходной сигнал t2=τ-t2 первого вычитателя 10 передается на первый вход второго интегратора 11, а также на оба входа второго блока умножения 6. Результат перемножения t 2 2 из блока умножения 6 передается на второй вход второго блока деления 3, на первый вход которого, как и на первый вход третьего блока деления 20, со второго входа устройства поступает значение сигнала 2 σ 2 2 . Выходной сигнал второго блока деления 3 передается на первый вход второго блока нелинейности 4, с выхода которого значение величины P2(t2) передается на вторые входы третьего блока умножения 7 и второго интегратора 11. В блоке умножения 7 формируется сигнал, соответствующий произведению Р1(t1)·Р2(t2), и передается на второй вход девятого блока умножения 31. Выходной сигнал второго интегратора 11 передается на второй вход, а выходной сигнал первого интегратора 8 - на первый вход первого сумматора 13. В сумматоре 13 реализуется соотношение (11) и его выходной сигнал передается через второй элемент задержки 34 в первый элемент памяти 35, а также в четвертый блок деления 22 через его первый вход.

В то же время с пятого входа устройства на первые входы четвертого 28 и пятого 32 сумматоров, а также на первый и второй входы пятого блока умножения 19 поступает значение величины τв. Результат перемножения τ в 2 из блока умножения 19 передается в третий блок деления 20, где формируется и передается на второй вход третьего блока нелинейности 21 величина t в 2 / 2 σ 2 2 . Сигнал, соответствующий величине Р(τв), с выхода третьего блока нелинейности 21 передается на второй вход седьмого блока умножения 29. На первый вход второго сумматора 23 с шестого входа устройства поступает значение величины τk1. С седьмого входа устройства на вторые входы четвертого 28 и второго 23 сумматоров передается значение величины τk2. Суммарный сигнал τk1+τk2 с выхода сумматора 23 поступает на оба входа шестого блока умножения 24 и на второй вход пятого сумматора 32. Результат перемножения (τk1+τk2)2 с выхода шестого блока умножения 24 передается на второй вход пятого блока деления 25. Выходной сигнал ( τ k 1 + τ k 2 ) 2 / 2 σ 1 2 с выхода блока деления 25 поступает на второй вход четвертого блока нелинейности 26, с выхода которого значение величины P(τk1+τk2) передается на второй вход восьмого блока умножения 30. Сигнал, соответствующий сумме τв+τk2, с выхода четвертого сумматора 28 поступает на первый вход седьмого блока умножения 29, выходной сигнал которого (τв+τk2)·Р(τв) передается на первый вход восьмого блока умножения 30. В блоке умножения 30 формируется сигнал, соответствующий величине (τв+τk2)·Р(τв)·Р(τв+τk2), который передается на первый вход девятого блока умножения 31. Выходной сигнал (τв+τk2)·Р(T)·Р(τв)·Р(τk1+τk2) блока умножения 31 поступает на второй вход второго вычитателя 33, на первый вход которого с выхода пятого сумматора 32 приходит сигнал, соответствующий сумме τk1+τв+τk2. В результате во втором вычитателе 33 формируется согласно (1) значение величины τобс, которое передается непосредственно на второй вход третьего сумматора 27 и через пятый элемент задержки 45 на информационный вход четвертого элемента памяти 43. В третьем сумматоре 27 осуществляется вычисление согласно (4) значения времени TЦ, которое передается на второй вход четвертого блока деления 22. В блоке 22 осуществляется вычисление текущего значения KГ(T) согласно (12), оно передается непосредственно на первый вход компаратора 17, а через четвертый элемент задержки 40 на информационный вход третьего элемента памяти 41 и на второй вход компаратора 17. В компараторе 17 происходит сравнение значений KГ(Ti) и KГ(Ti-1). В первом цикле работы устройства выполнится условие KГ(Ti)>KГ(Ti-1). Поэтому управляющий сигнал компаратора 17 появится на его первом выходе и через схему ИЛИ 16 поступит непосредственно на вход мультивибратора 14, а через первый элемент задержки 15 - на вход датчика времени 12. При этом на выходе датчика времени 12 будет действовать сигнал, соответствующий величине T=2τ, и процесс вычисления значений искомых величин, т.е. работы устройства, повторится. Так будет продолжаться пока KГ(Ti) будет больше либо равным KГ(Ti-1).

Как только при некотором значении T=nτ, n=2,3, … в результате сравнения в компараторе 17 окажется, что KГ(Ti)<KГ(Ti-1) управляющий сигнал появится на втором выходе компаратора 17. Этот сигнал переведет триггер 18 в единичное состояние. Его выходной сигнал обеспечит считывание содержимого первого 35, второго 38, третьего 41 и четвертого 43 элементов памяти, откроет вентили 36, 39, 42 и 44, а также переведет датчик времени 12 в исходное (нулевое) состояние. В результате этого вычисленные значения величин Tф, τ, KГ, Tобс поступят соответственно на первый, второй, третий и четвертый выходы устройства. На этом работа устройства заканчивается.

Возрастание интенсивности отказов изделия влечет за собой смещение оптимального периода управления техническим состоянием изделия в сторону меньших значений. Поэтому каждое очередное оптимальное значение периода необходимо находить с учетом изменения интенсивности отказов.

Положительный эффект, который дает предлагаемое техническое решение, состоит в том, что устройство позволяет определять значения периодов управления техническим состоянием изделия, обеспечивающие максимально возможную готовность изделия к применению, с учетом увеличения интенсивности отказов изделия в процессе его эксплуатации, а также различия значений этой интенсивности при нахождении изделия в рабочем режиме и в режиме отдыха после применения.

Источники информации

1. Седякин Н.М. Об одном физическом принципе теории надежности. - Известия АН СССР, ОТН, Техническая кибернетика, 1966, №3.

2. Половко A.M. Основы теории надежности. М.: наука, 1964.

3. Гришин В.Д., Зиновьев С.В., Соколов Б.В., Майданович О.В. Патент RU № 2452027. МПК G07C 3/08, 2012.

4. Соколов Б.В., Стародубов В.А., Гришин В.Д., Цивирко Е.Г. Патент RU № 2476935, МПК G07C 3/08, 2013.

5. Гришин В.Д., Павлов А.Н., Михайлов Е.П. Патент RU № 2343544, МПК G07C 3/08, 2009.

6. Гришин В.Д., Кудряшов А.Н., Тимошенко Д.В. Патент RU № 2347272, МПК G07C 3/08, 2009.

7. Соколов Б.В., Гришин В.Д., Зеленцов В.А., Цивирко Е.Г. Патент RU № 2479041, МПК G07C 3/08, 2013.

8. Соколов Б.В., Гришин В.Д., Зеленцов В.А., Майданович О.В. Патент RU № 2476934, МПК G07C 3/08, 2013.

9. Тетельбаум И.М., Шнейдер Ю.Р. 400 схем для АВМ, - М.: Энергия, 1978.

Устройство для определения оптимального периода управления техническим состоянием изделия, содержащее первый блок нелинейности, выход которого соединен с первыми входами первого интегратора и третьего блока умножения, второй вход которого подключен к выходу второго блока нелинейности и ко второму входу второго интегратора, а выход соединен со вторым входом девятого блока умножения, первый вход второго интегратора подключен к выходу первого вычитателя, а выход - ко второму входу первого сумматора, первый вход которого соединен с выходом первого интегратора, а выход - непосредственно с первым входом четвертого блока деления и через второй элемент задержки - с информационным входом первого элемента памяти, выход которого подключен к информационному входу первого вентиля, выход которого является первым выходом устройства, вторым выходом которого является выход второго вентиля, информационный вход которого соединен с выходом второго элемента памяти, информационный вход которого подключен к выходу третьего элемента задержки, третьим выходом устройства является выход третьего вентиля, информационный вход которого соединен с выходом третьего элемента памяти, информационный вход которого через четвертый элемент задержки подключен к выходу четвертого блока деления и к первому входу компаратора, первый выход которого соединен со вторым входом схемы ИЛИ, выход которой связан с входом мультивибратора, а первый вход, являющийся четвертым входом устройства, соединен с первым входом триггера, второй вход которого подключен ко второму выходу компаратора, а выход связан с управляющими входами первого, второго, третьего и четвертого элементов памяти, первого, второго, третьего и четвертого вентилей, четвертым выходом устройства является выход четвертого вентиля, вход которого соединен с выходом четвертого элемента памяти, информационный вход которого подключен к выходу пятого элемента задержки, вход которого через третий сумматор соединен со вторым входом четвертого блока деления, а непосредственно - с выходом второго вычитателя, первый вход которого подключен к выходу пятого сумматора, второй вход которого соединен с выходом второго сумматора, второй вход которого связан со вторым входом четвертого сумматора, выход которого подключен к первому входу седьмого блока умножения, второй вход которого соединен с выходом третьего блока нелинейности, четвертый блок нелинейности, восьмой блок умножения, выход которого соединен с первым входом девятого блока умножения, отличающееся тем, что в него введены датчик времени, первый элемент задержки, четыре блока деления и пять блоков умножения, причем первый вход устройства соединен с первыми входами пятого блока деления и первого блока деления, второй вход которого подключен к выходу первого блока умножения, а выход - к первому входу первого блока нелинейности, второй вход которого соединен с выходом мультивибратора, с первыми входами третьего и четвертого блоков нелинейности, с третьими входами первого и второго интеграторов, а также со вторым входом второго блока нелинейности, первый вход которого подключен к выходу второго блока деления, первый вход которого связан с первым входом третьего блока деления и является вторым входом устройства, а второй вход соединен с выходом второго блока умножения, оба входа которого связаны с выходом первого вычитателя, второй вход которого подключен ко второму входу первого интегратора, к первому и второму входам первого блока умножения и к выходу четвертого блока умножения, первый вход которого является третьим входом устройства, а второй вход соединен с первым входом первого вычитателя, с входом третьего элемента задержки, с первым входом третьего сумматора и с выходом датчика времени, второй вход которого подключен к выходу триггера, а первый вход через первый элемент задержки - к выходу схемы ИЛИ, пятый вход устройства соединен с первыми входами четвертого и пятого сумматоров и с обоими входами пятого блока умножения, выход которого подключен ко второму входу третьего блока деления, выход которого соединен со вторым входом третьего блока нелинейности, первый и второй входы второго блока умножения являются соответственно шестым и седьмым входами устройства, а выход подключен к обоим входам шестого блока умножения, выход которого соединен со вторым входом пятого блока деления, выход которого подключен ко второму входу четвертого блока нелинейности, выход которого соединен с первым входом восьмого блока умножения, первый вход которого связан с выходом седьмого блока умножения, выход девятого блока умножения подключен ко второму входу второго вычитателя, второй вход компаратора соединен с выходом четвертого элемента задержки.