Логический преобразователь

Иллюстрации

Показать всеИзобретение относится к вычислительной технике, предназначено для реализации любой из пяти простых симметричных булевых функций, зависящих от пяти аргументов - входных двоичных сигналов, и может быть использовано как средство преобразования кодов. Техническим результатом является упрощение устройства. Устройство содержит четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, резистор, шестнадцать ключей. 1 ил., 1 табл.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические преобразователи (см., например, патент РФ 2294007, кл. G06F 7/57, 2007 г.), которые реализуют любую из пяти простых симметричных булевых функций, зависящих от пяти аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических преобразователей, относятся их мажоритарный элементный базис и то, что, в частности, в упомянутом аналоге имеется не менее восьми мест пересечения соединений.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический преобразователь (патент РФ 2475814, кл. G06F 7/57, 2013 г.), который содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, резистор, группы ключей и реализует любую из пяти простых симметричных булевых функций τ1, …, τ5, зависящих от пяти аргументов - входных двоичных сигналов x1, …, x5∈{0, 1}. Отметим, что для функции τj ( j = 1 , 5 ¯ ) справедливо равенство

τ j = { 1 п р и ∑ i = 1 5 x i ≥ j 0 п р и ∑ i = 1 5 x i < j . ( 1 )

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится сложность устройства, обусловленная тем, что в прототипе имеется пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, двадцать один ключ и четыре места пересечения соединений.

Техническим результатом изобретения является упрощение устройства за счет сокращения количества ключей и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а также уменьшения числа мест пересечения соединений при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом преобразователе, содержащем элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, резистор и группы ключей, в которых нечетные и четные ключи выполнены соответственно замыкающими и размыкающими, в k-й ( k = 1 , 2 ¯ ) группе, содержащей пять ключей, вход и выход второго, вход и выход четвертого ключей соединены соответственно с входом третьего и выходом первого, входом пятого и выходом третьего ключей, в третьей группе вход и выход второго, выход четвертого ключей соединены соответственно с входом третьего и выходом первого, выходом третьего ключей, в четвертой группе выход второго ключа соединен с выходом первого ключа, выход нечетного ключа предыдущей группы соединен с входом одноименного нечетного ключа последующей группы, выход пятого ключа второй и выход третьего ключа третьей групп соединены соответственно с входом четвертого ключа третьей и входом второго ключа четвертой групп, а входы первого, третьего и пятого ключей первой группы соединены соответственно с вторым, третьим и четвертым настроечными входами логического преобразователя, q-й ( q = 1 , 4 ¯ ) информационный вход которого образован первым входом q-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенного выходом и вторым входом соответственно к управляющему входу ключей q-й группы и первому настроечному входу логического преобразователя, подсоединенному через резистор к выходу логического преобразователя, особенность заключается в том, что выход первого ключа четвертой группы соединен с выходом логического преобразователя, который содержит не более четырех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и не более четырех групп ключей, третью и четвертую из которых образуют соответственно четыре и два ключей.

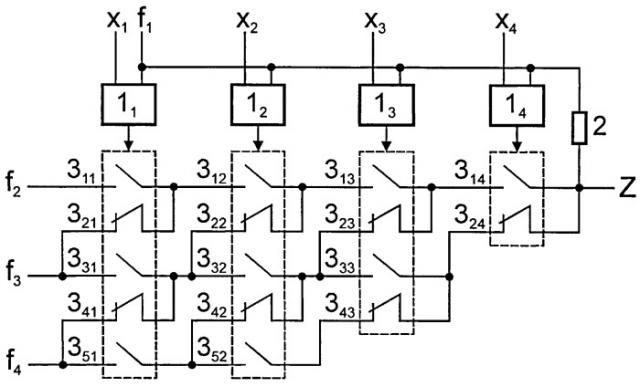

На чертеже представлена схема предлагаемого логического преобразователя.

Логический преобразователь содержит четыре элемента исключающее или 11, …, 14, резистор 2 и шестнадцать ключей 311, …, 324, причем все ключи сгруппированы в четыре группы так, что k-я ( k = 1 , 2 ¯ ) , третья и четвертая группы содержат соответственно ключи 31k, …, 35k, ключи 313, …, 343 и ключи 314, 324, а ключи 31k 33k, 35k 313, 333, 314 и 32k 34k 323, 343, 324 выполнены соответственно замыкающими и размыкающими, вход и выход ключа 32k, вход и выход ключа 34k соединены соответственно с входом ключа 33k и выходом ключа 31k, входом ключа 35k и выходом ключа 33k, вход и выход ключа 323, выход ключа 343 соединены соответственно с входом ключа 333 и выходом ключа 313, выходом ключа 333, выход ключа 324 соединен с выходом ключа 314 и выходом логического преобразователя, выход нечетного ключа предыдущей группы соединен с входом одноименного нечетного ключа последующей группы, выходы ключей 352 и 333 соединены соответственно с входами ключей 343 и 324, а входы ключей 311, 331 и 351 соединены соответственно с вторым, третьим и четвертым настроечными входами логического преобразователя, q-й ( q = 1 , 4 ¯ ) информационный вход которого образован первым входом элемента 1q, подсоединенного выходом и вторым входом соответственно к управляющему входу ключей q-й группы и первому настроечному входу логического преобразователя, подсоединенному через резистор 2 к выходу ключа 314.

Работа предлагаемого логического преобразователя осуществляется следующим образом. На его первый, …, четвертый настроечные и первый,…,четвертый информационные входы подаются соответственно необходимые управляющие сигналы ƒ1, …, ƒ4∈{0, 1} и входные двоичные сигналы x1, …, x4∈{0, 1}. Если на управляющем входе ключей m-й ( m = 1 , 3 ¯ ) группы присутствует логическая «1» либо логический «0», то нечетные ключи этой группы соответственно замкнуты либо разомкнуты, а четные - соответственно разомкнуты либо замкнуты. Если на управляющем входе ключей четвертой группы присутствует логическая «1» либо логический «0», то ключ 314 (324) соответственно замкнут (разомкнут) либо разомкнут (замкнут). Таким образом, имеем следующую таблицу

| ƒ1 | ƒ2 | ƒ3 | ƒ4 | Z |

| 1 | x5 | 1 | 1 | { 1 п р и ∑ i = 1 5 x i ≥ 1 0 п р и ∑ i = 1 5 x i < 1 |

| 1 | 0 | x5 | 1 | { 1 п р и ∑ i = 1 5 x i ≥ 2 0 п р и ∑ i = 1 5 x i < 2 |

| 0 | 1 | 1 | x5 | { 1 п р и ∑ i = 1 5 x i ≥ 3 0 п р и ∑ i = 1 5 x i < 3 |

| 0 | 1 | x5 | 0 | { 1 п р и ∑ i = 1 5 x i ≥ 4 0 п р и ∑ i = 1 5 x i < 4 |

| 0 | x5 | 0 | 0 | { 1 п р и ∑ i = 1 5 x i = 5 0 п р и ∑ i = 1 5 x i < 5 |

С учетом равенства (1) и данных, приведенных в таблице, операция, воспроизводимая предлагаемым логическим преобразователем, определяется выражением

Z = { τ 1 п р и f 1 = f 3 = f 4 = 1 , f 2 = x 5 τ 2 п р и f 1 = f 4 = 1 , f 2 = 0 , f 3 = x 5 τ 3 п р и f 1 = 0 , f 2 = f 3 = 1 , f 4 = x 5 τ 4 п р и f 1 = f 4 = 0 , f 2 = 1 , f 3 = x 5 τ 5 п р и f 1 = f 3 = f 4 = 0 , f 2 = x 5 .

При этом он имеет три места пересечения соединений.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический преобразователь реализует любую из пяти простых симметричных булевых функций, зависящих от пяти аргументов - входных двоичных сигналов, и устроен проще, чем прототип, поскольку имеет меньшие аппаратурные затраты и меньшее число мест пересечения соединений.

Логический преобразователь, предназначенный для реализации любой из пяти простых симметричных булевых функций, зависящих от пяти аргументов - входных двоичных сигналов, содержащий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, резистор и группы ключей, в которых нечетные и четные ключи выполнены соответственно замыкающими и размыкающими, причем в k-й группе, содержащей пять ключей, вход и выход второго, вход и выход четвертого ключей соединены соответственно с входом третьего и выходом первого, входом пятого и выходом третьего ключей, в третьей группе вход и выход второго, выход четвертого ключей соединены соответственно с входом третьего и выходом первого, выходом третьего ключей, в четвертой группе выход второго ключа соединен с выходом первого ключа, выход нечетного ключа предыдущей группы соединен с входом одноименного нечетного ключа последующей группы, выход пятого ключа второй и выход третьего ключа третьей групп соединены соответственно с входом четвертого ключа третьей и входом второго ключа четвертой групп, а входы первого, третьего и пятого ключей первой группы соединены соответственно с вторым, третьим и четвертым настроечными входами логического преобразователя, q-й информационный вход которого образован первым входом q-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенного выходом и вторым входом соответственно к управляющему входу ключей q-й группы и первому настроечному входу логического преобразователя, подсоединенному через резистор к выходу логического преобразователя, отличающийся тем, что выход первого ключа четвертой группы соединен с выходом логического преобразователя, который содержит не более четырех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и не более четырех групп ключей, третью и четвертую из которых образуют соответственно четыре и два ключей.