Устройство обнаружения атак в беспроводных сетях стандарта 802.11g

Иллюстрации

Показать всеИзобретение относится к области электросвязи и может быть использовано для определения состояния беспроводной сети связи, обнаружения в ней атак и повышения достоверности принятия решения системами обнаружения атак в беспроводных сетях. Технический результат, на достижение которого направлено изобретение, заключается в разработке устройства, обеспечивающего обнаружение признаков DoS-атак, атак типа «человек посередине» и нарушения режимов работы сети. Устройство обнаружения атак в беспроводных сетях стандарта 802.11g содержит блок определения режима 1, блок выделения параметров 2, блок хранения и сравнения MAC-адресов 3, блок контроля состояния соединения 4, счетчик повторно идущих подряд кадров 5, блок распознавания фреймов с запросами на разрыв соединения от неподключенного пользователя 6, блок проверки наличия двух одинаковых MAC-адресов 7, блок нормировки 8, блок управления 9, блок принятия решения 10. 11 ил., 2 табл.

Реферат

Изобретение относится к области электросвязи и может быть использовано для определения состояния беспроводной сети связи, обнаружения в ней атак и повышения защищенности беспроводных сетей.

Известно устройство поиска информации по патенту РФ №2301443, приоритет изобретения 04 июля 2005 г., содержащее два блока памяти, девять счетчиков, одиннадцать блоков дешифрации, блок сравнения, устройство управления и блок индикации.

Данное устройство имеет недостаток - анализ сравнительно небольшого количества параметров проходящих через него потоков, основанный на сигнатурном методе, что приводит к неустойчивому функционированию автоматизированных систем в условиях несанкционированного информационного воздействия, а также низкая достоверность принятия решения.

Наиболее близким по технической сущности (прототипом) является устройство определения состояния сети связи по патенту №2383105, приоритет изобретения 30 июня 2006 г. Устройство определения состояния сети связи содержит блок выделения параметров, блок сравнения адресов IP, блок SYN/FIN, блок интенсивности, блок нагрузки, блок потерь, блок достоверности, блок нормировки, блок управления, блок индикации. Первый и второй входы блоков интенсивности, нагрузки подключены соответственно к пятому, шестому, седьмому и восьмому выходам блока выделения параметров, а первый, второй, третий входы блока достоверности подключены соответственно к девятому, десятому и одиннадцатому выходам блока выделения параметров, двенадцатый выход блока выделения параметров подключен к девятнадцатому входу блока индикации, входом блока потерь является статистическая информация о соотношении числа пакетов, получивших отказ к общему числу пришедших пакетов, первый выход блока SYN/FIN, выходы блока интенсивности, блока нагрузки и блока потерь подключены соответственно к первому, второму, третьему и четвертому входам блока нормировки, первый, второй, третий и четвертый выходы которого подключены соответственно к первому, второму, третьему и четвертому входам блока управления, выход блока достоверности подключен к восемнадцатому входу блока индикации, а выходы блока управления с третьего по восемнадцатый включительно подключены соответственно ко входам блока индикации со второго по семнадцатый включительно, выход блока сравнения IP адресов подключен к первому входу блока индикации.

Данное устройство по сравнению с аналогом позволяет расширить область применения и повышения достоверности принятия решения за счет расширения набора характеристических параметров, анализа протокола TCP, учета правил установления и ведения сеанса связи, выявления случаев аномального увеличения интенсивности информационного обмена, аномального увеличения нагрузки входящего трафика, изменения соотношения числа пакетов на установление и разъединение соединения, аномального увеличения числа пакетов, получивших отказ, определения достоверности используемого источником IP адреса, выявления случаев установки запрещенных комбинаций флагов и неправильной установки IP адресов получателя и отправителя пакета.

К недостаткам устройства-прототипа относятся:

- возможность анализа сравнительно небольшого количества параметров проходящих через него,

- низкая защищенность,

- узкая область применения (только в проводных сетях),

- возможность анализа пакета только на сетевом уровне ЭМВОС.

Задачей изобретения является повышение защищенности за счет увеличения количества анализируемых параметров и проведения дополнительного анализа пакета на канальном уровне ЭМВОС, расширение области применения (возможность использования в беспроводных сетях).

Поставленная задача достигается тем, что в известное устройство определения состояния сети связи, содержащее блок управления, блок нормировки, блок выделения параметров, блок управления, первый выход которого подключен к первому входу блока нормировки, а первый вход к первому входу того же блока, дополнительно введены блок определения режима, блок принятия решения, блок хранения и сравнения MAC-адресов, счетчик повторно идущих подряд кадров, блок контроля состояния соединения, блок проверки наличия двух одинаковых МАС-адресов, блок распознавания фреймов с запросом на разрыв соединения от неподключенного пользователя, первый вход блока определения режима является информационным входом устройства, первый и второй выходы подключены соответственно к первому и второму входам блока выделения параметров, а третий выход подключен соответственно ко второму входу блока нормировки, первый выход блока выделения параметров подключен соответственно к первому входу блока распознавания фреймов с запросом на разрыв соединения от неподключенного пользователя, а выходы блока выделения параметров со второго по четвертый подключены соответственно ко входам с первого по третий блока контроля состояния соединения, пятый выход блока выделения параметров подключен ко входу счетчика повторно идущих подряд кадров, а шестой и седьмой выходы подключены соответственно ко второму и третьему входам блока хранения и сравнения MAC-адресов, на первый вход которого подается статическая информация о разрешенных адресах, первый и второй выходы блока хранения и сравнения MAC-адресов подключены соответственно к шестому и седьмому входам блока нормировки, первый выход блока контроля состояния соединения подключен ко второму входу блока распознавания фреймов с запросом на разрыв соединения от неподключенного пользователя, а второй выход блока контроля состояния соединения подключен ко входу блока проверки наличия двух одинаковых МАС-адресов, выход которого подключен к четвертому входу блока нормировки, выход счетчика повторно идущих подряд кадров подключен к пятому входу блока нормировки, выход блока распознавания фреймов с запросом на разрыв соединения от неподключенного пользователя подключен к третьему входу блока нормировки, выходы со второго по седьмой блока нормировки подключены соответственно ко входам со второго по седьмой блока принятия решения, второй и третий выходы блока управления подключены соответственно к третьему и второму входам блока определения режима, а четвертый выход блока управления подключен к первому входу блока принятия решения, первый выход которого подключен ко второму входу блока управления.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "Новизна". Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из современного уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "Изобретательский уровень".

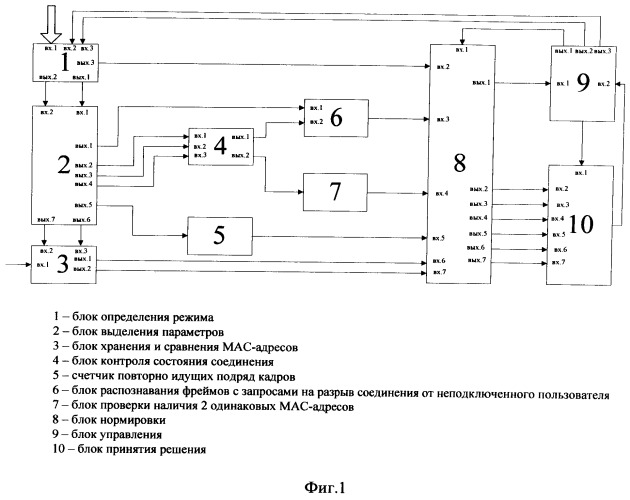

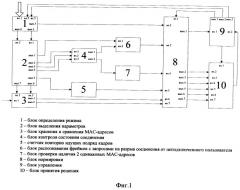

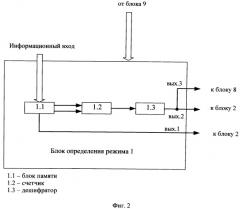

Заявленное устройство поясняется следующими чертежами, где приведено:

фиг.1 - устройство определения состояния сети связи;

фиг.2 - структурная схема блока определения режима;

фиг.3 - структурная схема блока выделения параметров;

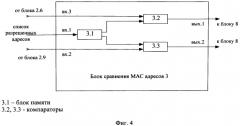

фиг.4 - структурная схема блока хранения и сравнения MAC-адресов;

фиг.5 - структурная схема блока состояния соединения;

фиг.6 - структурная схема счетчика повторно идущих подряд кадров;

фиг.7 - структурная схема блока распознавания фреймов с запросами на разрыв соединения от неподключенного пользователя;

фиг.8 - структурная схема блока проверки наличия двух одинаковых MAC-адресов;

фиг.9 - структурная схема блока нормировки;

фиг.10 - алгоритм работы блока управления;

фиг.11 - алгоритм работы блока принятия решения.

Устройство определения состояния сети связи, показанное на фиг.1, содержит блок определения режима 1, блок выделения параметров 2, блок хранения и сравнения MAC-адресов 3, блок контроля состояния соединения 4, счетчик повторно идущих подряд кадров 5, блок распознавания фреймов с запросами на разрыв соединения от неподключенного пользователя 6, блок проверки наличия двух одинаковых MAC-адресов 7, блок нормировки 8, блок управления 9, блок принятия решения 10.

Первый вход блока определения режима 1 является информационным входом устройства, первый и второй выходы подключены соответственно к первому и второму входам блока выделения параметров 2, а третий выход подключен соответственно ко второму входу блока нормировки 8, первый выход блока выделения параметров 2 подключен соответственно к первому входу блока распознавания фреймов с запросом на разрыв соединения от неподключенного пользователя 6, выходы со второго по четвертый блока выделения параметров подключены соответственно к входам с первого по третий блока контроля состояния соединения 4, пятый выход подключен ко входу счетчика повторно идущих подряд кадров 5, шестой и седьмой выходы блока выделения параметров подключены соответственно ко второму и третьему входам блока хранения и сравнения MAC-адресов 3, на первый вход которого подается статическая информация о разрешенных адресах, первый и второй выходы блока хранения и сравнения MAC-адресов 3 подключены соответственно к шестому и седьмому входам блока нормировки 8, первый выход блока контроля состояния соединения 4 подключен соответственно ко второму входу блока распознавания фреймов с запросом на разрыв соединения от неподключенного пользователя 6, второй выход подключен соответственно к входу блока проверки наличия двух одинаковых MAC-адресов 7, выход счетчика повторно идущих подряд кадров 5 подключен к пятому входу блока нормировки 8, выход блока распознавания фреймов с запросом на разрыв соединения от неподключенного пользователя 6 подключен к третьему входу блока нормировки 8, выход блока проверки наличия двух одинаковых MAC-адресов 7 подключен к четвертому входу блока нормировки 8, первый выход блока нормировки 8 подключен к первому входу блока управления 9, выходы со второго по седьмой включительно подключены соответственно ко входам со второго по седьмой блока принятия решения 10, второй и третий выходы блока управления 9 подключены соответственно к третьему и второму входам блока определения режима 1, а его первый выход подключен к первому входу блока нормировки 8, четвертый выход подключен к первому входу блока принятия решения 10, выход которого подключен ко второму входу блока управления 9.

Блок определения режима предназначен для распознавания типа фрейма с точки зрения режима передачи информации (между станциями, между точками доступа, между станцией и точкой доступа) и подачи сигнала на входы блока выделения параметров и блока нормировки. Его структурная схема представлена на фиг.2.

Первый блок памяти 1.1 предназначен для хранения и последующего считывания с него на первый счетчик 1.2, первый блок памяти 2.1 блока выделения параметров байтов данных фреймов, поступающих с демодулирующего устройства, и подачи команды об окончании записи пришедших данных пакета на первый счетчик 1.2.

Первый счетчик 1.2 отсчитывает 1 байт в цифровой последовательности для определения значения полей "From DS" и "To DS".

Первый блок дешифрации 1.3 предназначен для определения в последовательности поступающих данных значений полей "From DS" и "To DS" и подачи управляющего сигнала на блок выделения параметров и блок нормировки.

Блок выделения параметров предназначен для анализа фрейма подуровня MAC и подачи извлеченных характеристических параметров (MAC-адресов отправителя и получателя, значений полей "Повтор", "Тип", "Подтип", команды "Разрыв соединения") на вход остальных блоков. Его структурная схема представлена на фиг.3

Первый блок памяти 2.1 предназначен для хранения и последующего считывания с него на второй 2.7, третий 2.10, четвертый 2.12, пятый 2.14 счетчики байтов данных фреймов, поступающих с первого блока памяти 1.1 блока определения.

Первый переключатель 2.2 становится в положение "а" или "б" в зависимости от команды, поступившей с первого дешифратора 1.3 блока определения режима.

Первый счетчик 2.3а (2.3б) отсчитывает 4 байта (10 байт) в цифровой последовательности для определения 6 байт MAC-адреса пользователя.

Первый блок дешифрации 2.4а (2.4б) предназначен для определения в последовательности поступающих данных MAC-адреса, перевода его в шестнадцатеричный вид и подачи управляющего сигнала разрешения записи этого значения во второй блок памяти 2.6.

Второй переключатель 2.5 становится в положение "а" или "б" в зависимости от команды, поступившей с первого дешифратора 1.3 блока определения режима.

Второй блок памяти 2.6 предназначен для записи в него и хранения значения 6 байт MAC-адреса пользователя и выдачи этого значения на блоки хранения и сравнения MAC-адресов 3 и контроля состояния соединения 4.

Второй счетчик 2.7 отсчитывает 16 байт в цифровой последовательности для определения 6 байт MAC-адреса пользователя.

Второй дешифратор 2.8 предназначен для определения в последовательности поступающих данных MAC-адреса, перевода его в шестнадцатеричный вид и подачи управляющего сигнала разрешения записи этого значения во второй блок памяти 2.9.

Третий блок памяти 2.9 предназначен для записи в него и хранения значения 6 байт MAC-адреса пользователя и выдачи этого значения на блок хранения и сравнения MAC-адресов.

Третий счетчик 2.10 предназначен для отсчета 2 бит для нахождения значения поля "Тип" фрейма и подаче управляющего сигнала о разрешении его записи в третий блок дешифрации 2.11.

Третий блок дешифрации 2.11 служит для определения числового значения поля "Тип" в двоичном виде, т.е. определения типа фрейма (управление, контроль или данные), подачи управляющего сигнала на четвертый счетчик 2.12 и выдачи этого значения на блок контроля состояния соединения 4.

Четвертый счетчик 2.12 предназначен для отсчета 4 бит для нахождения значения поля "Подтип" фрейма и подаче управляющего сигнала о разрешении его записи в четвертый блок дешифрации 2.13.

Четвертый блок дешифрации 2.13 служит для определения числового значения поля "Подтип" в двоичном виде, подачи управляющего сигнала на пятый счетчик 2.14 и выдачи этого значения на блок контроля состояния соединения 4 и первый компаратор 2.17.

Пятый счетчик 2.14 предназначен для отсчета 11 бит для нахождения значения поля "Повтор" фрейма и подаче управляющего сигнала о разрешении его записи в четвертый блок дешифрации 2.15.

Пятый блок дешифрации 2.15 служит для определения числового значения поля "Повтор" в двоичном виде и выдачи этого значения на счетчик повторно идущих подряд кадров 5.

Первый ключ 2.16 включается в случае поступления на первый и второй переключатели, 2.2 и 2.5 соответственно, команды на переключение в положение "а".

Первый компаратор 2.17 предназначен для сравнения числового значения поля "Подтип" с комбинациями "1100" и "1010", т.е. выделения фреймов с запросами на разрыв соединения или отмену аутентификации, и выдачи сигнала на блок распознавания фреймов с запросом на разрыв соединения от неподключенного пользователя 6.

Блок хранения и сравнения MAC-адресов 3 предназначен для выявления пользователей сети с неразрешенными MAC-адресами и подачи сигнала об этом в блок нормировки 8. Вариант схемы блока хранения и сравнения MAC-адресов 3 представлен на фиг.4.

Блок контроля состояния соединения 4 предназначен для обнаружения фреймов с ответами на запрос ассоциации (повторной ассоциации) и выдачи этого значения на блок проверки наличия двух одинаковых MAC-адресов 7 и блок распознавания фреймов с запросами на разрыв соединения от неподключенного пользователя 6. Вариант схемы данного блока представлен на фиг.5.

Счетчик повторно идущих подряд кадров 5 предназначен для подсчета повторяющихся кадров и выдачи этого значения на блок нормировки 8. Вариант схемы данного блока представлен на фиг.6.

Блок распознавания фреймов с запросами на разрыв соединения от неподключенного пользователя 6 предназначен для обнаружения факта отправки фреймов с запросом на разрыв соединения или отмену аутентификации от пользователя, который не подключен к сети (не прошел фазу ассоциации), и выдачи этого значения на блок нормировки 8. Вариант схемы данного блока представлен на фиг.7.

Блок проверки наличия двух одинаковых MAC-адресов 7 предназначен для обнаружения факта подключения к сети пользователей с одинаковыми MAC-адресами и выдачи этого значения на блок нормировки 8. Вариант схемы данного блока представлен на фиг.8.

Блок нормировки 8 предназначен для нормирования входных величин для равноценного учета их в процессе принятия решения и выдачи полученных значений на блок управления 9. Вариант схемы блока нормировки представлен на фиг.9.

Блок управления 9 предназначен для подачи управляющих сигналов "стирание" и "запись" на первый блок памяти 1.1 для разрешения считывания следующего пакета информации и подачи управляющих сигналов на считывание информации из блока нормировки 8 в блок принятия решения 10. Вариант схемы блока управления представлен на фиг.10.

Блок принятия решения 10 предназначен для принятия решения о состоянии сети в данный момент времени на основе анализа поступающих на него нормированных числовых значений характеристических параметров, определения состояния каждого из характеристических параметров.

Блок определения режима содержит блок памяти 1.1, который может быть реализован на микросхемах ОЗУ К185РУ4 (Справочник по интегральным микросхемам / Б.В. Тарабрин, С.В. Якубовский, Н.А. Баранов и др.; Под ред. Б.В. Тарабрина. - 2-е изд., перераб. и доп. - М.: Энергия, 1980. - С.215).

Схема счетчика 1.2 известна и описана, например, на фиг.6, 7, 8 патент РФ №2219577, МПК G06F 17/40 и может быть реализована на элементах "И", счетчиках и дешифраторах. Схемы элементов "И" известны и описаны, например, в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.40, рис.1.23. В частности, такая схема может быть реализована на микросхеме К555ЛИ2. Счетчик может быть реализован на микросхемах серии К555, см., например. Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987. стр.90, рис.1.66. Дешифратор может быть реализован на микросхемах дешифраторов, имеющих четыре разряда, см., например, Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.133, рис.1.95. В частности, такая схема может быть реализована на микросхеме К555ИД3.

Схема первого 1.3 блока дешифрации известна (см., например, фиг.2 и фиг.3 патента РФ №2219577, МПК G06F 17/40) и может быть реализована на элементах "И", дешифраторах и элементах "И-НЕ". Схемы элементов "И" известны и описаны, например, в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь. 1987, на стр.40, рис.1.23. В частности, такая схема может быть реализована на микросхеме К555ЛР12. В качестве дешифраторов может быть использованы микросхемы серии 555, например, К555ИД10 (Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.137, рис.1.98). В качестве элемента "И-НЕ" может быть использована, например, микросхема К155ЛА3 (Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.41, рис.1.24).

Блок выделения параметров содержит пять счетчиков, пять блоков дешифации, один компаратор, три блока памяти, два переключателя и ключ.

Первый 2.1, второй 2.6, третий 2.9 блоки памяти могут быть реализованы на микросхемах ОЗУ К185РУ4 (Справочник по интегральным микросхемам / Б.В. Тарабрин, С. В. Якубовский, Н.А. Баранов и др.; Под ред. Б.В. Тарабрина. - 2-е изд., перераб. и доп. - М.: Энергия, 1980. - С.215).

Схемы первого 2.3, второго 2.7, третьего 2.10, четвертого 2.12, пятого 2.14 счетчиков известны и описаны, например, на фиг.6, 7, 8 патент РФ №2219577, МПК G06F 17/40 и могут быть реализованы на элементах "И", счетчиках и дешифраторах. Схемы элементов "И" известны и описаны, например, в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.40, рис.1.23. В частности, такая схема может быть реализована на микросхеме К555ЛИ2. Счетчики могут быть реализованы на микросхемах серии К555, см., например, Шило В.Л. Популярные цифровые микросхемы: Справочник. - М: Радио и связь, 1987. стр.90, рис.1.66. Дешифратор может быть реализован на микросхемах дешифраторов, имеющих четыре разряда, см., например, Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.133, рис.1.95. В частности, такая схема может быть реализована на микросхеме К555ИД3.

Схемы первого 2.4, второго 2.8, третьего 2.11, четвертого 2.13, пятого 2.15 блоков дешифрации известны (см., например, фиг.2 и фиг.3 патента РФ №2219577, МПК G06F 17/40) и могут быть реализованы на элементах "И", дешифраторах и элементах "И-НЕ". Схемы элементов "И" известны и описаны, например, в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь. 1987, на стр.40, рис.1.23. В частности, такая схема может быть реализована на микросхеме К555ЛР12. В качестве дешифраторов могут быть использованы микросхемы серии 555, например, К555ИД10 (Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.137, рис.1.98). В качестве элемента "И-НЕ" может быть использована, например, микросхема К155ЛА3 (Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.41, рис.1.24). Схемы переключателей 2.2, 2.5 и ключа 2.16 описаны в книге Батушев В.А. Микросхемы и их применение: Справочное пособие - М.: Радио и связь, 1983. Схема компаратора 2.17 для сравнения двух N-разрядных слов описана в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.183-184, 187, рис.1.135. Она может быть реализована на микросхеме К555СП1.

Блок хранения и сравнения MAC-адресов содержит компараторы 3.2, 3.3. Схемы компараторов для сравнения двух N-разрядных слов известны и описаны в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.183-184, 187, рис.1.135. Они могут быть реализованы на микросхемах К555СП1. Блок памяти 3.1 может быть реализован на микросхемах ОЗУ К185РУ4 (Справочник по интегральным микросхемам / Б.В. Тарабрин, С.В. Якубовский, Н.А. Баранов и др.; Под ред. Б.В. Тарабрина. - 2-е изд., перераб. и доп. - М.: Энергия, 1980. - С.215).

Блок контроля состояния соединения содержит компараторы 4.1, 4.2, 4.3, схемы которых описаны в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.183-184, 187, рис.1.135. Они могут быть реализованы на микросхемах К555СП1. Сумматоры 4.4 и 4.5 могут быть реализованы на микросхемах, описанных в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.34-39, рис.1.21. В частности, такая схема может быть реализована на микросхеме К155ЛЕ5. Блок памяти 4.6 может быть реализован на микросхемах ОЗУ К185РУ4 (Справочник по интегральным микросхемам / Б.В. Тарабрин, С.В. Якубовский, Н.А. Баранов и др.; Под ред. Б.В. Тарабрина. - 2-е изд., перераб. и доп. - М.: Энергия, 1980. - С.215).

Счетчик 5.1 может быть реализован на микросхемах серии К500, см., например, Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987. стр.314, рис.2.33.

Схема компаратора 6.1 известна и описана в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, стр.183-184, 187, рис.1.135. Она может быть реализована на микросхеме К555СП1.

Блок памяти 7.1 может быть реализован на микросхемах ОЗУ К185РУ4 (Справочник по интегральным микросхемам / Б.В. Тарабрин, С.В. Якубовский, Н.А. Баранов и др.; Под ред. Б.В. Тарабрина. - 2-е изд., перераб. и доп. - М.: Энергия, 1980. - С.215). Компаратор 7.2 может быть реализован на микросхеме К555СП1.

Блок памяти 8.1 может быть реализован на микросхемах ОЗУ К185РУ4 (Справочник по интегральным микросхемам / Б.В. Тарабрин, С.В. Якубовский, Н.А. Баранов и др.; Под ред. Б.В. Тарабрина. - 2-е изд., перераб. и доп. - М.: Энергия, 1980. - С.215).

Блоки управления и принятия решения могут быть реализованы на микропроцессорах TMS32010 (Ланне А.А. «Цифровой процессор TMS32010 и его применение». - Л.: ВАС, 1990. - 296 с.). Блоки управления и принятия решения представляют собой последовательностные логические схемы и могут быть синтезированы по известным правилам (Гутников B.C., Лопатин В.В. и др. «Электронные устройства информационно-измерительной техники»: Учебное пособие. - Л.: ЛПИ им. Калинина, 1980, стр.73-76, рис.42; Гутников B.C. «Интегральная электроника в измерительных устройствах». - Л.: Энергия, 1980. - 248 с.).

Устройство работает следующим образом. Первый блок памяти 1.1 блока определения режима предназначен для хранения и последующего считывания с него байтов данных фрейма. При получении с выхода блока управления 9 управляющих сигналов "стирание" и "запись" (логическая "1") производится заполнение ячеек ОЗУ первого блока памяти 1.1 байтами пакета, поступившими с демодулирующего устройства. После того как записаны все байты очередного пакета анализируемого протокола, на втором выходе блока памяти 1.1 формируется разрешение на побайтное считывание информации (логическая "1"). С первого выхода первого блока памяти 1.1 байты фрейма последовательно поступают на первый вход первого 1.2 счетчика и первый вход блока памяти 2.1.

При поступлении на вход первого счетчика 1.2 сигнала с блока памяти 1.1 (логическая "1") считывается 1 байт для определения значения полей "From DS" и "To DS".

Первый блок дешифрации 1.3 предназначен для определения в последовательности поступающих данных значений полей «From DS» и «To DS». В случае получения комбинации полей «10» или «01» на выход дешифратора соответственно подается команда «00» или «01». В противном случае на выход подается логическая «1», что означает недопустимый режим работы.

Первый блок памяти 2.1 блока выделения параметров предназначен для хранения и последующего считывания с него байтов данных фрейма. При получении с выхода блока управления 9 управляющих сигналов «стирание» и «запись» (логическая «1») на блок определения режима 1 производится заполнение ячеек ОЗУ первого блока памяти 2.1 байтами пакета, поступившими с блока памяти 1.1. После того как записаны все байты очередного пакета анализируемого протокола, на втором выходе блока памяти 2.1 формируется разрешение на побайтное считывание информации (логическая «1»). С первого выхода первого блока памяти 2.1 байты пакетов последовательно поступают на второй 2.7, третий 2.10, четвертый 2.12, пятый 2.14 счетчики.

При поступлении на вход первого переключателя 2.2 и второго переключателя 2.5 сигнала «01» с дешифратора 1.3 они устанавливаются в положение «а», при сигнале «00» - в положение «б».

При нахождении переключателей в положении «а» происходит следующее. При поступлении на вход первого счетчика 2.3а сигнала с блока памяти 2.1 (логическая «1») считываются 4 байта для определения 6 байт MAC-адреса пользователя. Затем первый дешифратор 2.4а переводит MAC-адрес в шестнадцатеричный вид и подает разрешающий сигнал на запись во второй блок памяти 2.6 полученного результата.

В случае нахождения переключателей в положении «б» происходит следующее. При поступлении на вход первого счетчика 2.36 сигнала с блока памяти 2.1 (логическая «1»), считываются 10 байт для определения 6 байт MAC-адреса пользователя. Затем первый дешифратор 2.46 переводит MAC-адрес в шестнадцатеричный вид и подает разрешающий сигнал на запись во второй блок памяти 2.6 полученного результата.

Во второй блок памяти 2.6 записывается и хранится значение 6 байт MAC-адреса пользователя. По первому выходу значение передается на блок хранения и сравнения MAC-адресов 3, где в блоке 3.2 сравнивается полученное значение с разрешенными значениями из блока 3.1, и блок контроля состояния соединения 4, если первый ключ 2.16 будет находиться во включенном состоянии. При этом на втором выходе вырабатывается сигнал для запуска второго счетчика 2.7, который отсчитывает 16 байт для определения 6 байт MAC-адреса пользователя. На втором дешифраторе 2.8 происходят преобразование MAC-адреса в шестнадцатеричный вид и подача управляющего сигнала о разрешении его записи в третий блок памяти 2.9.

Третий блок памяти 2.9 хранит значение MAC-адреса пользователя и по первому выходу передает его на блок хранения и сравнения MAC-адресов 3, где в блоке 3.3 сравнивается полученное значение с разрешенными значениями из блока 3.1. При этом на втором выходе вырабатывается сигнал для запуска третьего счетчика 2.10, который отсчитывает 2 бита для нахождения значения поля «Тип» и подает управляющий сигнал о разрешении его записи в третий блок дешифрации 2.11.

Третий блок дешифрации 2.11 определяет числовое значение поля «Тип» в двоичном виде и по первому выходу передает его на блок контроля состояния соединения 4. При этом на втором выходе вырабатывается сигнал для запуска четвертого счетчика 2.12, который отсчитывает 4 бита для нахождения значения поля «Подтип» фрейма и подает управляющий сигнал о разрешении его записи в четвертый блок дешифрации 2.13.

Четвертый блок дешифрации 2.13 определяет числовое значение поля «Подтип» в двоичном виде и по первому выходу передает его на первый компаратор 2.17 и на блок контроля состояния соединения 4. При этом на втором выходе вырабатывается сигнал для запуска пятого счетчика, который отсчитывает 11 бит для нахождения значения поля «Повтор» фрейма и подает управляющий сигнал о разрешении его записи в пятый блок дешифрации 2.15.

Пятый блок дешифрации 2.15 определяет числовое значение поля «Повтор» в двоичном виде и по первому выходу передает его на счетчик повторно идущих подряд кадров 5.

Первый ключ 2.16 во включенном состоянии обеспечивает передачу MAC-адреса пользователя на блок контроля состояния соединения 4. Включение ключа 2.16 происходит при подаче на него комбинации «01» от первого блока дешифрации 1.3.

Первый компаратор 2.17 сравнивает значения поля «Подтип», полученные от четвертого дешифратора 2.13, с комбинациями «1100» и «1010». При нахождении одной из данных комбинаций в ходе сравнения на выход компаратора подается сигнал логическая «1», который поступает на вход блока распознавания фреймов с запросами на разрыв соединения от неподключенного пользователя 6.

При получении с первых выходов второго 2.6 и третьего 2.9 блоков памяти на второй и третий входы блока хранения и сравнения MAC-адресов 3 MAC-адресов они сравниваются с имеющимся списком разрешенных адресов. При несовпадении адресов на выходе компаратора формируется сигнал логическая «1», который поступает на 6 и 7 входы блока нормировки 8.

В блоке контроля состояния соединения 4 на первый вход поступает значение поля «Тип». Значение поля в компараторе 4.1 сравнивается с комбинацией «00». При равенстве значений на выход компаратора подается сигнал логическая «1», означающий, что данный фрейм является управляющим. Параллельно на второй вход подается значение поля «Подтип», которое сравнивается с комбинациями «0001» и «0011» в компараторах 4.2 и 4.3 соответственно. При наличии в поле фрейма одной из комбинаций, один компаратор выдаст значение логическая «1», а второй - логический «0». С выходов компараторов 4.2 и 4.3 значения поступают на сумматор по модулю два 4.4. Сформированная на выходе сумматора 4.4 логическая «1» будет означать о предположении, что в кадре передается ответ на запрос ассоциации, т.е. о том, что соединение установлено. Значения с выходов компаратора 4.1 и сумматора 4.4 поступают на входы элемента «И» 4.5. При поступлении логических «1» с компаратора 4.1 и сумматора 4.4 предположение о передаче ответа на запрос ассоциации подтверждается. При этом на выходе элемента «И» 4.5 формируется логическая «1», которая включает ключ 4.7 и является разрешающей командой блоку памяти 4.6 для записи MAC-адреса, поступающего из второго блока памяти 2.6. Выходы блока памяти 4.6 подключены к первому входу блока проверки наличия двух одинаковых MAC-адресов 7 и второму входу блока распознавания фреймов с запросами на разрыв соединения от неподключенного пользователя 6.

С выхода дешифратора 2.12 значения поступают на вход счетчика 5.1, который считает приходящие логические «1». Обнуление счетчика происходит при поступлении на него логического «0». С выхода счетчика 5.1 значения поступают на блок нормировки 8.

На входы компаратора 6.1 подаются сигналы с компаратора 2.17 и блока памяти 4.6. Сигнал логический «0», приходящий из блока памяти 4.6, означает, что пользователь не подключен к сети. А сигнал логическая «1» из компаратора 2.17 означает, что фрейм содержит запрос на разрыв соединения. При соответствующих входных значениях компаратор 6.1 будет формировать на выходе логическую «1», отправляемую на вход блока нормировки 8.

На вход блока памяти 7.1 поступают все MAC-адреса, подключенные к сети. С выходов блока памяти 8.1 полученные адреса поступают на компаратор 7.2. Таким образом происходит сравнение между собой всех адресов. При совпадении адресов на выходе компаратора 7.2 формируется сигнал логическая «1», поступающий на вход блока нормировки 8.

С выходов блоков определения режима 1, хранения и сравнения MAC-адресов 3, распознавания фреймов с запросами на разрыв соединения от неподключенного пользователя 6, проверки наличия двух одинаковых MAC-адресов 7 и счетчика повторно идущих подряд кадров 5 поступают значения на блок памяти 8.1. При получении значений со всех пяти входов на блок управления подается сигнал о готовности считывания на блок принятия решения в виде логической «1». С выходов блока нормировки значения подаются на блок принятия решения 10.

При поступлении сигнала из блока нормировки 8 на блок управления 9 начинает работу алгоритм управления. При поступлении на первый вход сигнала от блока нормировки 8 на четвертом выходе формируется сигнал на считывание информации блоком принятия решения 10. Далее блок управления 9 дожидается сигнала на второй вход с блока принятия решения 10. Получив сигнал на второй вход, блок управления по первому и второму выходу последовательно выдает логические «1» (сигналы «стирание» и «запись»), которые поступают на блок определения режима 1.

При поступлении сигнала от блока управления 9 на входы блока принятия решения 10 начинает работу алгоритм принятия решения.

Если на третий вход поступает логическая «1», то проверяется условие поступления логической «1» на четвертый вход. При выполнении этого условия на первый выход блока принятия решения выдается значение логической «1». При невыполнении условия на второй выход блока принятия решения выдается значение логической «1».

Если на третьем входе не выполняется условие, то проверяется наличие логической «1» на четвертом входе. При выполнении этого условия на второй выход блока принятия решения выдается значение логической «1». При невыполнении условия происходит проверка поступления логической «1» на входы шесть и семь.

Если на вход шестого или седьмого входа поступит логическая единица, то проверяется значение на входе пятого блока. Если значение больше 45, то проверяется условие поступления на второй вход логической «1». При выполнении этого условия на второй выход блока принятия решения выдается значение логической «1», при невыполнении - значение логической «1» подается на третий выход.

Если на пятом входе значение меньше 45, то проверяется условие наличия логической «1» на втором входе. При выполнении этого условия на третий выход блока принятия решения выдается значение логической «1». При невыполнении условия на четвертый выход блока принятия решения выдается значение логической «1».

При невыполнении условия поступления на шестой и седьмой входы логической «1» проверяется значение на пятом входе. Если значение на входе больше 10, то значение сравнивается со следующим пределом. Если значение меньше 25, то на четвертый вход подается логическая «1», если больше - идет сравнение со следующим значением. Если на пятом входе поступило значение больше чем 45, то на третий выход подается логическая «1», если меньше - на четвертый выход.

Если значение на пятом входе меньше 10, то проверяется второй вход. При поступлении на него логической «1» на пятый выход блока принятия решения выдается значение логической «1». При невыполнении условия логическая «1» выдается на шестой выход. После проверки выполнения данных условий в соответствии с алгоритмом блок принятия решения выдает сигнал на второй вход блока управления 9.

Устройство готово к проведению а