Твердотельное устройство считывания изображений

Иллюстрации

Показать всеИзобретение относится к твердотельному устройству считывания изображений, включающему блоки аналого-цифрового преобразования. Техническим результатом является обеспечение возможности сравнивать пиксельный сигнал с различными опорными сигналами для преобразования пиксельного сигнала в цифровой сигнал с высокой точностью, наряду с уменьшением масштаба схемы. Датчик изображения содержит множество наборов единичных пикселей, выводящих пиксельный сигнал на основании электрического заряда, генерируемого посредством фотоэлектрического преобразования, и блок преобразования, преобразующий пиксельный сигнал в цифровой сигнал. Источник опорных сигналов генерирует опорные сигналы и подает сгенерированные сигналы на блок преобразования через линии сигналов. Блок преобразования каждого набора содержит компаратор, который сравнивает уровень опорного сигнала с уровнем пиксельного сигнала, схему подсчета, которая считает время на основании обработки сравнения, схему выбора, которая выбирает среди линий сигналов линию, которая должна быть избирательно подсоединена к входу компаратора, и ключ, который избирательно подсоединяет выбранную линию к входу компаратора и избирательно подсоединяет нагрузку к одной невыбранной из линий сигналов. 2 н. и 8 з.п. ф-лы, 29 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится к твердотельному устройству считывания изображений и, более точно, к твердотельному устройству считывания изображений, включающему в себя блоки аналого-цифрового преобразования.

УРОВЕНЬ ТЕХНИКИ

Датчик изображения, выполненный с использованием технологии CMOS и включающий в себя A/D преобразователь (далее будет упоминаться в качестве "A/D преобразователь столбца") для выполнения аналого-цифрового (A/D) преобразования для каждого столбца единичных пикселей, выполненных в матричной топологии, используется в качестве твердотельного устройства считывания изображений. В качестве способа A/D преобразования используется множество компараторов, чтобы соответствующим образом сравнивать пиксельные сигналы с опорными сигналами, которые имеют различные показатели изменений в соответствии со временем, таким образом выполняя A/D преобразование на основании сравнения по времени (см опубликованный патент Японии №2007-281987 (литературный источник 1)).

Кроме того, предложен способ выбора из множества опорных сигналов, каждый из которых характеризуется линейно изменяющимся напряжением, опорного сигнала, соответствующего пиксельному сигналу, исходя из результата определения уровня пиксельного сигнала, и сравнения выбранного опорного сигнала и пиксельного сигнала друг с другом, тем самым выполняя A/D преобразование на основании сравнения по времени (см опубликованный патент Японии №2006-352597 (литературный источник 2)).

Однако для способа, использующего множество компараторов, описанных в литературном источнике 1, масштаб схемы велик. Кроме того, литературный источник 2 не описывает способ подачи множества опорных сигналов во время сравнения пиксельного сигнала с опорным сигналом, который был выбран из множества опорных сигналов, каждый из которых характеризуется линейно изменяющимся напряжением.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

В одном аспекте твердотельное устройство считывания изображений, имеющее множество наборов единичных пикселей, выводящих пиксельный сигнал, и блок преобразования, преобразующий пиксельный сигнал в цифровой сигнал, содержит: генератор опорных сигналов, выполненный с возможностью генерировать множество опорных сигналов и подавать множество опорных сигналов на блок преобразования через соответствующую одну из множества линий сигналов; причем устройство отличается тем, что блок преобразования каждого набора содержит: компаратор, выполненный с возможностью сравнивать уровень опорного сигнала с уровнем пиксельного сигнала, счетчик, выполненный с возможностью считать время на основании сравнения, селектор, выполненный с возможностью выбирать из множества линий сигналов линию сигналов, которая должна быть подсоединена к входу компаратора, и соединительный узел, выполненный с возможностью избирательно подсоединять выбранную линию сигналов к входу компаратора и избирательно подсоединять нагрузку к невыбранной линии сигналов из множества линий сигналов.

В другом аспекте твердотельное устройство считывания изображений, имеющее множество наборов единичных пикселей, выводящих пиксельный сигнал, и блок преобразования, преобразующий пиксельный сигнал в цифровой сигнал, содержит: генератор опорных сигналов, выполненный с возможностью генерировать множество опорных сигналов и подавать множество опорных сигналов на блок преобразования; причем устройство отличается тем, что блок преобразования каждого набора содержит: компаратор, выполненный с возможностью сравнивать уровень опорного сигнала с уровнем пиксельного сигнала, и счетчик, выполненный с возможностью считать время на основании сравнения, при этом компаратор содержит: множество блоков ввода опорных сигналов, выполненных с возможностью вводить соответствующим образом множество опорных сигналов, и селектор, выполненный с возможностью избирательно разрешать операцию ввода одному из множества блоков ввода опорных сигналов.

Согласно этим аспектам, обеспечивается возможность сравнивать пиксельный сигнал с различными опорными сигналами для преобразования пиксельного сигнала в цифровой сигнал с высокой точностью, наряду с уменьшением масштаба схемы.

Дополнительные признаки настоящего изобретения станут очевидными из последующего описания примерных вариантов осуществления со ссылкой на прилагаемые чертежи.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

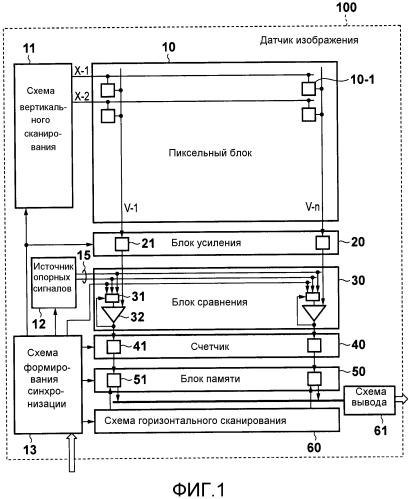

Фиг. 1 - принципиальная схема для разъяснения компоновки датчика изображения, служащего в качестве твердотельного устройства считывания изображений согласно варианту осуществления.

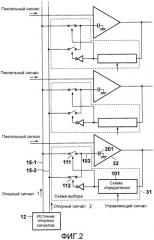

Фиг. 2 - принципиальная схема для разъяснения компоновки общей схемы выбора.

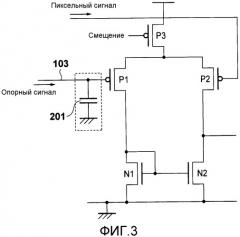

Фиг. 3 - принципиальная схема, показывающая компоновку общего компаратора.

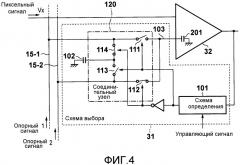

Фиг. 4 - принципиальная схема, показывающая компоновку схемы выбора согласно первому варианту осуществления.

Фиг. 5 - временная диаграмма для разъяснения работы схемы выбора согласно первому варианту осуществления.

Фиг. 6 - временная диаграмма для разъяснения работы схемы выбора согласно второму варианту осуществления.

Фиг. 7 - временная диаграмма для разъяснения работы схемы выбора согласно третьему варианту осуществления.

Фиг. 8 - принципиальная схема, показывающая компоновку схемы выбора согласно четвертому варианту осуществления.

Фиг. 9 - принципиальная схема, показывающая компоновку схемы выбора согласно пятому варианту осуществления.

Фиг. 10 - принципиальная схема, показывающая компоновку схемы выбора согласно шестому варианту осуществления.

Фиг. 11 - временная диаграмма для разъяснения работы схемы выбора согласно шестому варианту осуществления.

Фиг. 12 - принципиальная схема, показывающая компоновку схемы выбора согласно седьмому варианту осуществления.

Фиг. 13 - временная диаграмма для разъяснения работы схемы выбора согласно седьмому варианту осуществления.

Фиг. 14 - принципиальная схема, показывающая компоновку схемы выбора и компаратора согласно восьмому варианту осуществления.

Фиг. 15 - временная диаграмма для разъяснения работы схемы выбора и компаратора согласно восьмому варианту осуществления.

Фиг. 16 - принципиальная схема, показывающая компоновку схемы выбора согласно девятому варианту осуществления.

Фиг. 17 - принципиальная схема, показывающая компоновку схемы выбора согласно десятому варианту осуществления.

Фиг. 18 - принципиальная схема, показывающая компоновку схемы выбора согласно одиннадцатому варианту осуществления.

Фиг. 19 - принципиальная схема, показывающая компоновку схемы выбора согласно двенадцатому варианту осуществления.

Фиг. 20 - временная диаграмма для разъяснения работы схемы выбора и компаратора согласно двенадцатому варианту осуществления.

Фиг. 21 - принципиальная схема, показывающая компоновку схемы выбора согласно тринадцатому варианту осуществления.

Фиг. 22 - принципиальная схема, показывающая компоновку схемы выбора согласно четырнадцатому варианту осуществления.

Фиг. 23 - принципиальная схема, показывающая компоновку схемы выбора согласно пятнадцатому варианту осуществления.

Фиг. 24 - принципиальная схема, показывающая компоновку схемы выбора и компаратора согласно шестнадцатому варианту осуществления.

Фиг. 25 - принципиальная схема, показывающая компоновку схемы выбора согласно семнадцатому варианту осуществления.

Фиг. 26 - принципиальная схема, показывающая компоновку схемы выбора согласно восемнадцатому варианту осуществления.

Фиг. 27 - принципиальная схема для разъяснения компоновки датчика изображения, служащего в качестве твердотельного устройства считывания изображений согласно девятнадцатому варианту осуществления.

Фиг. 28 - принципиальная схема, показывающая компоновку управления задним затвором.

Фиг. 29 - принципиальная схема, показывающая компоновку схемы выбора согласно девятнадцатому варианту осуществления.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Твердотельное устройство считывания изображений и способ аналогово-цифрового (A/D) преобразования для него, согласно варианту осуществления настоящего изобретения, подробно будут описаны ниже со ссылкой на прилагаемые чертежи.

Первый вариант осуществления

Компоновка устройства

Компоновка датчика 100 изображения, служащего в качестве твердотельного устройства считывания изображений, согласно варианту осуществления, будет описана со ссылкой на принципиальную схему, показанную на Фиг.1. Датчик 100 изображения будет упоминаться в качестве датчика изображения, реализованного с использованием технологии CMOS, который выполняет фотоэлектрическое преобразование изображения объекта, полученного посредством приема света, и выводит электрический сигнал в качестве цифрового сигнала. Датчик 100 изображения включает в себя нижеследующие основные блоки схем.

Пиксельный блок 10 служит в качестве области фотоэлектрического преобразования. Схема 11 вертикального сканирования сканирует пиксельный блок 10. Блок 20 усиления усиливает выходной аналоговый пиксельный сигнал из пиксельного блока 10. Источник 12 опорных сигналов служит в качестве блока генерирования опорных сигналов, который генерирует опорный сигнал с линейно изменяющимся напряжением и т.п.

Блок 30 сравнения сравнивает пиксельный сигнал с опорным сигналом. Счетчик 40 считает период сравнения блока 30 сравнения (подробности его будут описаны позже). Блок 50 памяти удерживает значение подсчета и выполняет битовый сдвиг и вычисление удерживаемых данных. Блок 30 сравнения, счетчик 40 и блок 50 памяти формируют основную часть блока аналого-цифрового преобразования (ADC).

Схема 60 горизонтального сканирования сканирует блок 50 памяти для передачи удерживаемых данных в блоке 50 памяти на схему 61 вывода. Схема 13 формирования синхронизации (TG) контролирует время операции каждого из вышеприведенных блоков схемы.

Множество единичных пикселей 10-1 выполнено в пиксельном блоке 10. Фиг. 1, тем не менее, для простоты показывает только четыре пикселя. Компоновка единичных пикселей 10-1 хорошо известна, и ее подробное описание будет опущено. Заметим, что единичный пиксель 10-1 включает в себя элемент фотоэлектрического преобразования, пиксельный усилитель, передаточный ключ для управления передачей электрического заряда, сформированного элементом фотоэлектрического преобразования, на электрод затвора пиксельного усилителя, и ключ сброса для сброса остаточных зарядов на элементе фотоэлектрического преобразования и электроде затвора. Соответствующие пиксельные строки, последовательно возбуждаемые возбуждающими импульсами X-l, X-2,..., выводятся из схемы 11 вертикального сканирования, и сигналы сброса соответствующих пикселей и значащие сигналы, служащие в качестве сигналов фотоэлектрического преобразования, отправляются на блок 20 усиления через множество линий сигналов от V-1 по V-n в столбцах.

Каждый из блоков с 20 по 50 включает в себя множество схем, число которых равно числу линий сигналов в столбцах. Отметим, что в дальнейшем ряд схем, соответствующих каждой линии сигналов в столбцах, могут упоминаться как «столбец».

Блок 20 усиления включает в себя множество схем 21 усиления, соответствующих конкретным столбцам. Каждая схема 21 усиления может иметь только функцию простого усиления вводимого сигнала из пикселя или может иметь функцию двойной коррелированной выборки (CDS) выполнения обработки для получения разности между значащим сигналом и сигналом сброса. Заметим, что если блок 20 усиления не предусмотрен, блок ввода блока 30 сравнения выполняет обработку CDS. Хотя блок 20 усиления не является обязательным, усиление сигнала снижает влияние шума, формируемого блоком 30 сравнения.

Источник 12 опорных сигналов включает в себя цифро-аналоговый преобразователь (DAC), который формирует опорный сигнал с напряжением, которое нарастает, или опорный сигнал (в дальнейшем упоминается как «опорный сигнал определения») с предварительно определенным напряжением и подает множество опорных сигналов или опорных сигналов определения на все столбцы через линии 15 опорных сигналов. Альтернативно, источник 12 опорных сигналов может подавать постоянный ток на линии 15 опорных сигналов для заряда емкостей соответствующих столбцов, тем самым формируя опорные сигналы или опорные сигналы определения.

Блок 30 сравнения включает в себя множество наборов схем 31 выбора и компараторов 32, соответствующих конкретным столбцам. Каждый компаратор 32 сравнивает сигнал сброса пикселя соответствующего столбца с опорными сигналами и затем сравнивает значащий сигнал пикселя с опорным сигналом определения в качестве опорного сигнала при выборе опорного сигнала. Схема 31 выбора служит в качестве блока выбора для выбора опорного сигнала на основании результата обработки сравнения. Компаратор 32 сравнивает значащий сигнал пикселя с выбранным опорным сигналом.

Счетчик 40 включает в себя множество схем 41 подсчета, каждая из которых считает время, предоставляемое TG 13 и соответствующее каждому столбцу. Схема 41 подсчета начинает считать время, когда соответствующий компаратор 32 начинает обработку сравнения значащего сигнала пикселя с выбранным опорным сигналом, и заканчивает считать время, когда выходной сигнал компаратора 32 инвертирован (обработка сравнения оканчивается).

Блок 50 памяти включает в себя множество схем 51 памяти, соответствующих конкретным столбцам. Каждая схема 51 памяти удерживает результат подсчета соответствующей схемы 41 подсчета в качестве результата A/D преобразования. В соответствии с импульсом сканирования, вводимым из схемы 60 горизонтального сканирования, блок 50 памяти передает данные (результат A/D преобразования), удерживаемые каждой схемой 51 памяти на схему 61 вывода.

Схема выбора

Компоновка каждой схемы 31 выбора будет описана со ссылкой на принципиальную схему на Фиг. 2.

Схема 31 выбора включает в себя схему 101 определения и ключи 111 и 112. Схема 101 определения управляет состояниями открытия/закрытия ключей 111 и 112 согласно управляющему сигналу, вводимому из TG 13, и вводит опорный сигнал 1 или 2 на компаратор 32 посредством переключения ключей 111 и 112 на основании результата обработки сравнения значащего сигнала пикселя с опорным сигналом определения посредством компаратора 32. Заметим, что при замкнутом состоянии ключа, сигнал или ток может проходить через ключ, и при разомкнутом состоянии ключа сигнал или ток не может проходить через ключ.

Емкость 201 внутри компаратора 32 является емкостью (в дальнейшем упоминается как "емкость нагрузки"), служащей в качестве нагрузки узла 103 подключения опорного сигнала. Другими словами, емкость 201 является эквивалентом значения емкости (упоминаться как "входная емкость") на входе компаратора 32 и значения паразитной емкости, такой как линия проводного соединения.

Фиг. 3 показывает компоновку компаратора 32. Узел 103 подключения опорного сигнала подсоединен к затвору MOS-транзистора. Есть емкость (емкость затвора) между другим выводом и затвором транзистора MOS. Также есть паразитная емкость в узле 103 подключения опорного сигнала. Эти емкости будут коллективно упоминаться в качестве емкости 201 нагрузки узла 103 подключения опорного сигнала.

Посредством формирования схем 31 выбора, как показано на Фиг. 2, число емкостей 201, подсоединенных к линии 15-1 или 15-2 опорных сигналов, изменяется в зависимости от числа соединений между столбцами и линиями 15-1 или 15-2 опорных сигналов для каждого цикла A/D преобразования. Другими словами, нагрузка каждой линии опорных сигналов изменяется для каждого цикла A/D преобразования. Поскольку нагрузка линии 15-1 или 15-2 опорных сигналов изменяется, также изменяется уровень опорного сигнала в каждом столбце, таким образом ухудшая точность A/D преобразования.

Согласно варианту осуществления, колебания нагрузки линий опорных сигналов подавляются посредством подключения такой же нагрузки к линии опорных сигналов, которая не подсоединена к компараторам 32, как и когда она подсоединена. Будет описан случай, в котором переключаются два опорных сигнала. Тем не менее, даже если используются три или более опорных сигнала, колебания нагрузки можно подавлять посредством подсоединения такой же нагрузки к линии опорных сигналов, которая не подсоединена к компараторам 32, как и когда она подсоединена. Опорные сигналы могут иметь такие же или отличные градиенты изменения напряжения.

Компоновка схемы 31 выбора, согласно первому варианту осуществления, будет описана со ссылкой на принципиальную схему на Фиг. 4.

Схема 31 выбора включает в себя схему 101 определения и ключи 111, 112, 113 и 114. Схема 101 определения управляет состояниями размыкания/замыкания ключей со 111 по 114, согласно управляющему сигналу, вводимому из TG 13, и вводит опорный сигнал 1 или 2 на компаратор 32 посредством переключения ключей со 111 по 114 на основании обработки результата сравнения значащего сигнала пикселя с опорным сигналом определения посредством компаратора 32.

Один конец каждого из ключей 111 и 112 подсоединяется к узлу 103 подключения опорного сигнала. Другой конец ключа 111 подсоединяется к линии 15-1 опорных сигналов, и другой конец ключа 112 подсоединяется к линии 15-2 опорных сигналов. Один конец каждого из ключей 113 и 114 подсоединяется к потенциалу GND земли через емкость 102. Другой конец ключа 113 подсоединяется к линии 15-2 опорных сигналов, и другой конец ключа 114 подсоединяется к линии 15-1 опорных сигналов. Емкость 102 имеет значение емкости, почти равное емкости 201 нагрузки. Более точно, значение емкости 102 определяется так, чтобы значение емкости, когда линия опорных сигналов подсоединяется к выходу компаратора 32, почти равнялось тому, когда он подсоединяется к емкости 102, в отношении линии опорных сигналов.

Исходя из результата обработки сравнения компаратором 32 значащего сигнала пикселя с опорным сигналом определения, схема 101 определения управляет состояниями размыкания/замыкания ключей со 111 по 114 для выборочного подсоединения линии 15-1 или 15-2 опорных сигналов к узлу 103 подключения опорного сигнала и подсоединяет емкость 102 к невыбранной линии опорных сигналов. Другими словами, ключи со 111 по 114 функционируют в качестве соединительного узла 120, который выборочно подсоединяет выбранную линию опорных сигналов к узлу 103 подключения опорного сигнала и выборочно подсоединяет невыбранную линию опорных сигналов к емкости 102.

Работа схемы 31 выбора, согласно первому варианту осуществления, будет описана со ссылкой на временную диаграмму, показанную на Фиг. 5.

Для ввода опорного сигнала 1 в компаратор 32 схема 31 выбора замыкает ключ 111 и размыкает ключ 114, тем самым избирательно подсоединяя линию 15-1 опорных сигналов к узлу 103 подключения опорного сигнала. В то же время, схема 31 выбора размыкает ключ 112 и замыкает ключ 113, тем самым избирательно подсоединяя емкость 102 к линии 15-2 опорных сигналов. В это время пиксель выводит сигнал сброса. В ходе периода (преобразование N) преобразования уровня шума компаратор 32 сравнивает сигнал сброса пикселя с опорным сигналом 1 с линейно изменяющимся напряжением. Когда уровень опорного сигнала 1 и сигнала сброса пикселя становится одинаковым, выход компаратора инвертируется.

В ходе периода определения после того, как пиксельный сигнал Vx переключится на значащий сигнал, опорный сигнал 1 поддерживает опорное напряжение Vr определения в качестве опорного сигнала определения, и обработка сравнения выполняется для каждого столбца. Другими словами, в ходе периода определения источник 12 опорных сигналов подает опорный сигнал определения с опорным напряжением Vr определения вместо опорного сигнала с изменением напряжения.

В столбце, в котором результат обработки сравнения значащего сигнала Vx пикселя с опорным сигналом Vr определения указывают, что значащий сигнал Vx является большим, чем опорный Vr сигнал определения (Vx>Vr), ключи 111 и 113 разомкнуты, а ключи 112 и 114 замкнуты. В результате, узел 103 подсоединения опорного сигнала избирательно подсоединяется к линии 15-2 опорных сигналов, и емкость 102 избирательно подсоединяется к линии 15-1 опорных сигналов. Другими словами, опорный сигнал 2 выбран для сравнения со значащим сигналом. В столбце, в котором результат обработки сравнения указывает, что Vx≤Vr, ключи не переключаются (ключи 111 и 113 остаются в замкнутом состоянии, а ключи 112 и 114 остаются в разомкнутом состоянии). Другими словами, опорный сигнал 1 выбран для сравнения со значащим сигналом.

В ходе периода (преобразования S) преобразования уровня сигнала компаратор 32 сравнивает значащий сигнал Vx пикселя с опорным сигналом 1 или 2 с линейно изменяющимся напряжением. Когда уровень опорного сигнала 1 или 2 и значащего сигнал Vx пикселя становится одинаковым, выход компаратора 32 инвертируется. Заметим, что опорные сигналы 1 и 2 имеют одинаковый исходный уровень Vmin напряжения и различные градиенты изменения напряжения.

Каждая схема 41 подсчета счетчика 40 считает период, когда начинается период преобразования N или период преобразования S до того, как выходной сигнал Vout компаратора 32 соответствующего столбца инвертирован, и сохраняет результат подсчета в соответствующей схеме 51 памяти. Схема 51 памяти столбца, в котором опорный сигнал 2 был выбран для сравнения со значащим сигналом, выполняет для результата подсчета битовый сдвиг пропорционально отношению между градиентами опорных сигналов 1 и 2.

Как описано выше, когда Vx≤Vr, опорный сигнал 1 с небольшим градиентом используется для выполнения A/D преобразования высокого разрешения, и когда Vx>Vr, опорный сигнал 2 с большим градиентом используется для выполнения преобразования с низким разрешением A/D, таким образом сокращая время преобразования. В это время нагрузка линии опорных сигналов почти постоянно не зависит от того, является ли опорный сигнал линии сигналов используемым в обработке сравнения, и колебания нагрузки линии опорных сигналов, зависящие от пиксельного сигнала, подавляются, тем самым позволяя предотвращать снижение точности A/D преобразования.

Второй вариант осуществления

Твердотельное устройство считывания изображений и способ A/D преобразования для него, согласно второму варианту осуществления настоящего изобретения, будут описаны ниже. Заметим, что во втором варианте осуществления такие же компоненты, как в первом варианте осуществления, указаны теми же самыми ссылочными номерами, и их подробное описание будет опущено.

Работа схемы 31 выбора, согласно второму варианту осуществления, будет описана со ссылкой на временную диаграмму, показанную на Фиг. 6.

Для ввода опорного сигнала 1 в компаратор 32 схема 31 выбора замыкает ключ 111 и размыкает ключ 114, тем самым избирательно подсоединяя линию 15-1 опорных сигналов к узлу 103 подключения опорного сигнала. В то же время, схема 31 выбора размыкает ключ 112 и замыкает ключ 113, тем самым избирательно подсоединяя емкость 102 к линии 15-2 опорных сигналов. В это время пиксель выводит сигнал сброса. В ходе периода преобразования N компаратор 32 сравнивает сигнал сброса пикселя с опорным сигналом 1 с линейно изменяющимся напряжением. Когда опорный сигнал 1 и сигнал сброса пикселя становятся одинакового уровня, выход компаратора инвертируется.

В ходе периода определения после того, как пиксельный сигнал Vx переключается на значащий сигнал, схема 31 выбора размыкает ключ 111 и замыкает ключ 114, тем самым избирательно подсоединяя емкость 102 к линии 15-1 опорных сигналов. В это же время схема 31 выбора замыкает ключ 112 и размыкает ключ 113, тем самым избирательно подсоединяя линию 15-2 опорных сигналов к узлу 103 подключения опорного сигнала. Опорный сигнал 2 имеет исходный уровень Vr и смещен на Voff (=Vr-Vmin) по отношению к опорному сигналу 1. Поэтому в ходе периода определения компаратор 32 сравнивает опорный Vr сигнал определения со значащим сигналом Vx пикселя.

В столбце, в котором результат обработки сравнения указывает, что Vx>Vr, ключи не переключаются (ключи 111 и 113 остаются в разомкнутом состоянии, а ключи 112 и 114 остаются в замкнутом состоянии). В результате, опорный сигнал 2 выбран для сравнения со значащим сигналом. В столбце, в котором результат обработки сравнения указывает, что Vx≤Vr, ключи 111 и 113 в замкнутом состоянии, а ключи 112 и 114 в разомкнутом состоянии. В результате, узел 103 подключения опорного сигнала избирательно подсоединяется к линии 15-1 опорных сигналов, и емкость 102 избирательно подсоединяется к линии 15-2 опорных сигналов. Другими словами, опорный сигнал 1 выбран для сравнения со значащим сигналом.

В ходе периода преобразования S компаратор 32 сравнивает значащий сигнал Vx пикселя с опорным сигналом 1 или 2 с линейно изменяющимся напряжением. Когда уровни опорного сигнала 1 или 2 и значащего сигнала Vx становятся одинаковыми, выход компаратора 32 инвертируется. Заметим, что опорный сигнал 1 имеет напряжение, которое увеличивается от Vmin до Vr, и опорный сигнал 2 имеет напряжение, которое увеличивается от Vr до Vr+Voff. Опорные сигналы имеют одинаковый градиент изменения напряжения.

Каждая схема 41 подсчета счетчика 40 считает с периода, когда начинается период преобразования N или период преобразования S до того, как выходной сигнал Vout компаратора 32 из соответствующего столбца инвертирован, и сохраняет результат подсчета в соответствующей схеме 51 памяти. Схема 51 памяти столбца, в котором опорный сигнал 2 был выбран для сравнения со значащим сигналом, добавляет для результата подсчета значение подсчета для смещения Voff между опорными сигналами 1 и 2.

Как описано выше, посредством выбора из двух опорных сигналов, которые были смещены относительно друг друга, опорного сигнала, который должен сравниваться со значащим сигналом, согласно значащему сигналу пикселя, можно сократить период преобразования по сравнению со случаем, в котором один опорный сигнал используется для выполнения A/D преобразования. В это время нагрузка линии опорных сигналов почти постоянно не зависит от того, является ли опорный сигнал линии сигналов используемым в обработке сравнения, и колебания нагрузки линии опорных сигналов, зависящие от пиксельного сигнала, подавляются, тем самым позволяя предотвратить снижение точности A/D преобразования.

Третий вариант осуществления

Твердотельное устройство считывания изображений и способ A/D преобразования для него, согласно третьему варианту осуществления настоящего изобретения, будут описаны ниже. Заметим, что в третьем варианте осуществления такие же компоненты, как в первом и во втором вариантах осуществления, указаны теми же самыми ссылочными номерами, и их подробное описание будет опущено.

Работа схемы 31 выбора, согласно третьему варианту осуществления, будет описана со ссылкой на временную диаграмму, показанную на Фиг. 7.

Для ввода опорного сигнала 1 в компаратор 32 схема 31 выбора замыкает ключ 111 и размыкает ключ 114, тем самым избирательно подсоединяя линию 15-1 опорных сигналов к узлу 103 подключения опорного сигнала. В то же время, схема 31 выбора размыкает ключ 112 и замыкает ключ 113, тем самым избирательно подсоединяя емкость 102 к линии 15-2 опорных сигналов. В это время пиксель выводит сигнал сброса. В ходе периода преобразования N компаратор 32 сравнивает сигнал сброса пикселя с опорным сигналом 1 с линейно изменяющимся напряжением. Когда уровни опорного сигнала 1 и сигнала сброса пикселя становятся одинаковыми, выход компаратора инвертируется.

В ходе периода определения после того, как пиксельный сигнал Vx переключается на значащий сигнал, схема 31 выбора размыкает ключ 111 и замыкает ключ 114, тем самым избирательно подсоединяя емкость 102 к линии 15-1 опорных сигналов. В это же время схема 31 выбора замыкает ключ 112 и размыкает ключ 113, тем самым избирательно подключая линию 15-2 опорных сигналов к узлу 103 подключения опорного сигнала. Опорный сигнал 2 имеет исходный уровень Vr. Поэтому в ходе периода определения компаратор 32 сравнивает опорный сигнал Vr определения со значащим сигналом Vx пикселя.

В столбце, в котором результат обработки сравнения указывает, что Vx>Vr, ключи не переключаются (ключи 111 и 113 остаются в разомкнутом состоянии, а ключи 112 и 114 остаются в замкнутом состоянии). Другими словами, опорный сигнал 2 выбран для сравнения со значащим сигналом. В столбце, в котором результат обработки сравнения указывает, что Vx≤Vr, ключи 111 и 113 в замкнутом состоянии, а ключи 112 и 114 в разомкнутом состоянии. В результате, узел 103 подключения опорного сигнала избирательно подсоединяется к линии 15-1 опорных сигналов, и емкость 102 избирательно подсоединяется к линии 15-2 опорных сигналов. Другими словами, опорный сигнал 1 выбран для сравнения со значащим сигналом.

В ходе периода преобразования S компаратор 32 сравнивает значащий сигнал Vx пикселя с опорным сигналом 1 или 2 с линейно изменяющимся напряжением. Когда уровни опорного сигнала 1 или 2 и значащего сигнала Vx становятся одинаковыми, выход компаратора 32 инвертируется. Заметим, что опорный сигнал 1 имеет напряжение, которое увеличивается от Vmin до Vr, и опорный сигнал 2 имеет напряжение, которое увеличивается от Vr до Vmax. Опорные сигналы имеют различные градиенты изменения напряжения.

Каждая схема 41 подсчета счетчика 40 считает с периода, когда начинается период преобразования N или период преобразования S, до того, как выходной сигнал Vout компаратора 32 из соответствующего столбца инвертирован, и сохраняет результат подсчета в соответствующей схеме 51 памяти. Схема 51 памяти столбца, в котором опорный сигнал 2 был выбран для сравнения со значащим сигналом, выполняет для результата подсчета битовый сдвиг пропорционально отношению между градиентами опорных сигналов 1 и 2. Схема 51 памяти также добавляет к значению подсчета, претерпевшему битовый сдвиг, значение подсчета для смещения Voff (=Vr-Vmin) между опорными сигналами 1 и 2.

Как описано выше, посредством выбора из двух опорных сигналов, которые были смещены относительно друг друга и имеют различные градиенты изменения напряжения, опорного сигнала, который должен сравниваться со значащим сигналом, можно сократить период преобразования по сравнению со случаем, в котором для выполнения A/D преобразования используется один опорный сигнал. В это время нагрузка линии опорных сигналов почти постоянно не зависит от того, является ли опорный сигнал линии сигналов используемым в обработке сравнения, и колебания нагрузки линии опорных сигналов, зависящие от пиксельного сигнала подавляются, тем самым позволяя предотвращать снижение точности A/D преобразования.

Четвертый вариант осуществления

Твердотельное устройство считывания изображений и способ A/D преобразования для него, согласно четвертому варианту осуществления настоящего изобретения, будут описаны ниже. Заметим, что в четвертом варианте осуществления, такие же компоненты, как в вариантах осуществления с первого по третий, указаны теми же самыми ссылочными номерами, и их подробное описание будет опущено.

Компоновка схемы 31 выбора согласно четвертому варианту осуществления будет описана со ссылкой на принципиальную схему на Фиг. 8. В отличие от компоновки по первому варианту осуществления, показанной на Фиг. 4, емкость 104 подсоединена между линией 15-1 опорных сигналов и ключом 111, и емкость 105 подсоединена между линией 15-2 опорных сигналов и ключом 112. Хотя не показано, предусмотрены компоненты, такие как ключ для испускания зарядов, накопленных в каждой емкости в ходе периода, отличного от периода преобразования или периода определения.

Источник 12 опорных сигналов по третьему варианту осуществления подает постоянный ток в качестве опорного сигнала. Напряжение в линии опорных сигналов изменяется непрерывно в связи с подаваемым постоянным током и емкостью нагрузки линии опорных сигналов. Другими словами, в третьем варианте осуществления градиент опорного сигнала определяется на основании значения тока и емкости нагрузки линии опорных сигналов. Напряжение узла 103 подключения опорного сигнала получается делением напряжения в линии опорных сигналов на значения емкости 104 и емкости 201 нагрузки или на значения емкости 105 и емкости 201 нагрузки. Если эти значения емкостей равны друг другу, напряжение узла 103 подключения опорного сигнала является половиной напряжения в линии опорных сигналов.

В четвертом варианте осуществления функционирование, если не учитывать того, что градиент и напряжение опорного сигнала определяются на основании значения постоянного тока, емкости нагрузки и отношения между значениями емкостей, осуществляется таким же образом, как и в вариантах осуществления с первого по третий, при этом получаются такие же результаты, как в описанных ранее вариантах осуществления.

Пятый вариант осуществления

Твердотельное устройство считывания изображений и способ A/D преобразования для него, согласно пятому варианту осуществления настоящего изобретения, будут описаны ниже. Заметим, что в пятом варианте осуществления, такие же компоненты, как в вариантах осуществления с первого по четвертый, указаны теми же самыми ссылочными номерами, и их подробное описание будет опущено.

Компоновка схемы 31 выбора согласно пятому варианту осуществления будет описана со ссылкой на принципиальную схему на Фиг. 9. Заметим, что в пятом варианте осуществления часть компоновки схемы 31 выбора включена в компаратор 32.

Входной транзистор М1 компаратора 32 имеет вывод затвора, подсоединенный к узлу 103 подключения опорного сигнала, истоковый вывод, подсоединенный к стоковому выводу транзистора М3, и стоковый вывод, подсоединенный к стоковому выводу транзистора М5.

Входной транзистор M2 имеет характеристики, эквивалентные характеристикам транзистора Ml. Транзистор M2 имеет вывод затвора, подсоединенный к соединительному узлу ключей 113 и 114, истоковый вывод, подсоединенный к стоковому выводу транзистора M3, и плавающий стоковый вывод. Вследствие этого, транзистор M2 является вспомогательным транзистором, который не работает. Заметим, что транзисторы М1 и М2 имеют одинаковые размеры (одинаковую ширину затвора и одинаковую длину затвора) для того, чтобы представлять эквивалентные характеристики.

Транзистор М4 имеет вывод затвора, в который вводится пиксельный сигнал Vx, истоковый вывод, подсоединенный к стоковому выводу транзистора М3, и стоковый вывод, подсоединенный к стоковому выводу транзистора М6 и входу схемы 101 определения в качестве выхода компаратора 32.

В пятом варианте осуществления нагрузка линии опорных сигналов каждого столбца является одним из транзисторов М1 и М2, которые имеют эквивалентные характеристики, и нагрузка всегда является постоянной, тем самым подавляя колебания нагрузки линии опорных сигналов, зависящие от пиксельного сигнала. Другими словами, транзистор М2 функционирует в качестве емкости 102 в вариантах осуществления с первого по третий. Таким образом, схема 101 определения, соединительный узел 120 и транзистор М2 формируют схему 31 выбора. Как само собой разумеющееся, эквивалентные транзисторы М1 и М2 выполняют одинаковую операцию для колебаний напряжения или колебаний нагрузки множества линий опорных сигналов.

В пятом варианте осуществления функционирование, если не учитывать того, что вспомогательный транзистор М2 используется вместо емкости 102, осуществляется таким же образом, как и в вариантах осуществления с первого по третий, и при этом получаются такие же результаты, как и в описанных ранее вариантах осуществления.

Шестой вариант осуществления

Твердотельное устройство считывания изображений и способ A/D преобразования для него, согласно шестому варианту осуществления настоящего изобретения, будут описаны ниже. Заметим, что в шестом варианте осуществления такие же компоненты, как в вариантах осуществления с первого по пятый, указаны теми же самыми ссылочными номерами, и их подробное описание будет опущено.

Компоновка схемы 31 выбора согласно шестому варианту осуществления будет описана со ссылкой на принципиальную схему на Фиг. 10. Есть некоторые моменты, отличные от компоновки в четвертом варианте осуществления, показанной на Фиг. 8. Во-первых, есть одна линия опорных сигналов. Во-вторых, емкость 106 подсоединена между потенциалом GND земли и точкой соединения ключа 112 и емкости 1