Устройство контроля ошибок в цифровых системах передачи на базе технологии ethernet

Иллюстрации

Показать всеИзобретение относится к устройству контроля ошибок в цифровых системах передачи на базе технологии АТМ. Технический результат заключается в повышении надежности обнаружения одиночных и кратных ошибок в кадре Ethernet переменой длины и обнаружения в проверяемой цифровой системе передачи данных перемежающихся одиночных и кратных отказов. Устройство содержит счетчик единичных импульсов передачи, блок управления передачи, блок памяти передачи, блок определения параметров передачи, цифровую систему передачи, счетчик единичных импульсов приема, блок управления приема, блок памяти приема, блок определения параметров приема, компаратор, блоки анализа кадра передачи и блок анализа кадра приема. 2 з.п. ф-лы, 4 ил.

Реферат

Изобретение относится к радиотехнике, а именно к контролю функционирования цифровых систем передачи данных на базе технологии Ethernet.

Известно устройство Ethernet, принципы построения и функционирования которого определены стандартом 802.3 IEEE. Наряду с функциями синхронизации, предварительного установления соединения и разделения среды в нем реализуется возможность контроля целостности кадра с помощью 32-разрядного циклического избыточного кода (Cyclic Redundancy Code, CRC-32) (согласно Brayer, K; Hammond, J L Jr. (December 1975). "Evaluation of error detection polynomial performance on the AUTOVON channel" in National Telecommunications Conference, New Orleans, La. Conference Record 1: 8-21 to 8-25, New York: Institute of Electrical and Electronics Engineers и Ross N. Wiliams / Anarchriz. Всё o CRC32 // Ross N. Williams).

Однако данное устройство имеет недостатки:

- каждая обнаруженная ошибка не обязательно связана с ошибкой одного бита информации;

- несколько битовых ошибок в одном блоке данных дают только одну ошибку для блока;

- возможна компенсация ошибочных символов одного знака ошибочными символами другого знака в блоке данных.

Наиболее близким по своей технической сущности к заявленному устройству является устройство контроля ошибок в цифровых системах передачи на базе технологии ATM [Патент на изобретение №2408985 от 10.01.11 г.], содержащее блок коммутации передачи, счетчик единичных импульсов передачи, блок управления передачи, блок памяти передачи, блок определения параметров передачи, цифровую систему передачи, блок коммутации приема, счетчик единичных импульсов приема, блок управления приема, блок памяти приема, компаратора, блок определения параметров приема, электронный ключ, выход которого является информационным выходом устройства контроля ошибок в цифровых системах передачи на базе технологии ATM, второй вход которого соединен с выходом компаратора, второй вход компаратора подключен ко второму выходу блока коммутации приема, первый выход которого соединен с первым входом счетчика единичных импульсов приема, второй вход которого подключен к первому выходу блока управления приема, пятый выход которого соединен с третьим входом блока коммутации приема, второй вход которого подключен к шестому выходу блока управления приема, второй выход которого соединен с четвертым входом блока памяти приема, первый выход которого подключен к первому входу компаратора. Пятый вход блока памяти приема соединен с выходом счетчика единичных импульсов приема, а первый и второй входы блока памяти приема подключены соответственно к первому и второму выходам блока определения параметров приема, первый вход которого соединен с вторым выходом блока памяти приема, третий вход которого подключен к третьему выходу блока управления приема, четвертый выход которого соединен с вторым входом блока определения параметров приема, а вход блока управления приема подключен ко второму выходу проверяемой цифровой системы передачи, являющийся ее выходом синхронизации, и к четвертому входу блока коммутации приема, первый вход которого соединен с первым входом электронного ключа и с первым выходом проверяемой цифровой системы передачи, являющимся ее информационным входом, второй вход которой является ее входом синхронизации и соединен с входом блока управления передачи, с пятым входом блока объединения, с четвертым входом блока коммутации передачи и с входом частоты синхронизации устройства контроля ошибок в цифровых системах передачи на базе технологии ATM, а первый вход проверяемой цифровой системы передачи подключен к выходу блока объединения, второй вход которого подключен к первому выходу блока памяти передачи, второй выход которого соединен с первым входом блока определения параметров передачи, второй вход которого подключен к четвертому выходу блока управления передачи, второй и третий выходы которого соединены соответственно с четвертым и третьим входами блока памяти передачи, первый вход которого подключен к первому выходу блока определения параметров передачи, второй выход которого соединен со вторым входом блока памяти передачи, пятый вход которого подключен к выходу счетчика единичных импульсов передачи, второй вход которого соединен с первым выходом блока управления передачи, седьмой и восьмой выходы которого подключены соответственно к четвертому и третьему входу блока объединения, а пятый и шестой выходы подключены соответственно к третьему и второму входам блока коммутации передачи, выход которого соединен с первым входом счетчика единичных импульсов передачи, а первый вход блока коммутации передачи подключен к информационному входу устройства контроля ошибок в цифровых системах передачи на базе технологии ATM и к первому входу блока объединения.

При такой схеме построения устройство-прототип позволяет обнаружить перемеживающиеся одиночные и кратные отказы.

Однако данное устройство имеет недостатки:

- подходит для сетей с архитектурой точка-точка;

- отсутствие возможности анализа кадров переменной длины.

Задачей изобретения является: разработка устройства, обеспечивающего обнаружение одиночных и кратных ошибок в кадре Ethernet переменной длины, контроль технического состояния проверяемой цифровой системы передачи данный различной архитектуры и обнаружение в ней перемежающихся одиночных и кратных отказов.

Для решения задачи изобретения в известное устройства контроля ошибок в цифровых системах передачи на базе технологии ATM, содержащее счетчик единичных импульсов передачи, блок управления передачи, блок памяти передачи, блок определения параметров передачи, цифровую систему передачи, счетчик единичных импульсов приема, блок управления приема, блок памяти приема, компаратора, блок определения параметров приема, дополнительно введены блоки анализа кадра передачи и блок анализа кадра приема, первый выход которого является информационным выходом цифровой системы передачи, а второй выход соединен с первым входом счетчика единичных импульсов приема, третий, четвертый выходы и третий и четвертый входы подключены соответственно к третьему, второму входам, к шестому и пятому выходам блока управления приема, второй и третий выходы которого соединены соответственно с четвертым и третьим входами блока памяти приема, четвертый выход блока управления приема соединен со вторым входом блока определения параметров приема, а первый выход - со вторым входом счетчика единичных импульсов приема, выход которого соединен с пятым входом блока памяти приема, второй выход которого подключен к первому входу блока определения параметров приема, а первый и второй входы блока памяти приема соединены соответственно с первым и вторым выходами блока определения параметров приема, первый выход блока памяти приема подключен к первому входу компаратора, второй вход которого соединен с пятым выходом блока анализа кадра приема, а выход компаратора подключен к четвертому входу блока управления приема, первый вход которого соединен со вторым входом блока анализа кадра приема и вторым выходом цифровой системы передачи, первый вход которой подключен к первому выходу блока анализа кадра передачи, а второй вход - к первому входу блока управления передачи, к входу частоты синхронизации и ко второму входу блока анализа кадра передачи, первый вход которого соединен с информационным входом устройства контроля ошибок в цифровых системах передачи на базе технологии Ethernet, третий, четвертый выходы, четвертый и пятый входы блока анализа кадра передачи подключены соответственно к третьему, второму входам и пятым, шестым выходам блока управления передачи, первый выход которого подключен ко второму входу счетчика единичных импульсов передачи, а второй и третий выходы подключены соответственно к четвертому и третьему входам блока памяти передачи, четвертый, седьмой и восьмой выходы блока управления передачи подключены соответственно ко второму, четвертому и третьему входам блока определения параметров передачи, первый, второй выходы и первый вход блока определения параметров передачи подключены соответственно к первому, второму входам и второму выходу блока памяти передачи, первый выход которого является информационной шиной и подключен к третьему входу блока анализа кадра передачи, второй выход которого соединен с первым входом счетчика единичных импульсов передачи, выход которого подключен к пятому входу блока памяти передачи.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями признаков, тождественным всем признакам заявленного устройства контроля ошибок в цифровых системах передачи на базе технологии Ethernet, отсутствуют, поэтому изобретение соответствует условию патентоспособности "Новизна".

Результаты поиска известных решений в данной и смежной областях техники с целью выявления признаков, совпадающих с отличительными от прототипов признаками заявленного изобретения, показали, что они не следуют явным образом из уровня техники. Из определенного заявителем уровня техники не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "Изобретательский уровень".

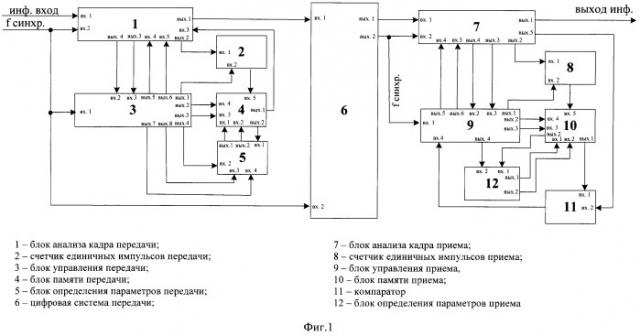

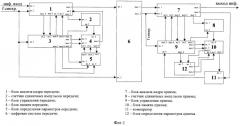

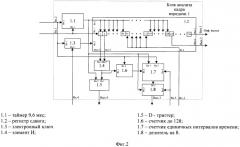

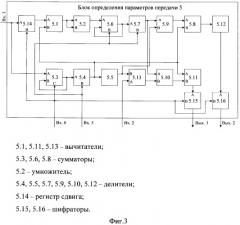

Заявленный объект изобретения поясняется чертежами, на которых показаны:

на фиг. 1 - структурная схема устройства контроля ошибок в цифровых системах передачи на базе технологии Ethernet;

на фиг. 2 - структурная схема блока анализа кадра передачи;

на фиг. 3 - структурная схема блока определения параметров передачи;

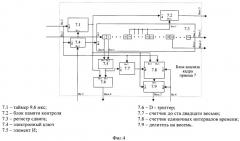

на фиг. 4 - структурная схема блока анализа кадра приема.

Устройство контроля ошибок в цифровых системах передачи на базе технологии Ethernet, показанное на фиг. 1, состоит из блока анализа кадра передачи 1, счетчика единичных импульсов передачи 2, блока управления передачи 3, блока памяти передачи 4, блока определения параметров передачи 5, цифровой системы передачи 6, блока анализа кадра приема 7, счетчика единичных импульсов приема 8, блока управления приема 9, блока памяти приема 10, компаратора 11, блока определения параметров приема 12. Первый выход блока анализа кадра приема 7 является информационным выходом цифровой системы передачи (локальной сети) 6, а второй выход соединен с первым входом счетчика единичных импульсов приема 8, третий, четвертый выходы и третий и четвертый входы подключены соответственно к третьему, второму входам, к шестому и пятому выходам блока управления приема 9, второй и третий выходы которого соединены соответственно с четвертым и третьим входами блока памяти приема 10, четвертый выход блока управления приема 9 соединен со вторым входом блока определения параметров приема 12, а первый выход - со вторым входом счетчика единичных импульсов приема 8, выход которого соединен с пятым входом блока памяти приема 10, второй выход которого подключен к первому входу блока определения параметров приема 12, а первый и второй входы блока памяти приема 10 соединены соответственно с первым и вторым выходами блока определения параметров приема 12, первый выход блока памяти приема 10 подключен к первому входу компаратора 11, второй вход которого соединен с пятым выходом блока анализа кадра приема 7, а выход компаратора 11 подключен к четвертому входу блока управления приема 9, первый вход которого соединен со вторым входом блока анализа кадра приема 7 и вторым выходом цифровой системы передачи 6, первый вход которой подключен к первому выходу блока анализа кадра передачи 1, а второй вход - к первому входу блока управления передачи 3, к входу частоты синхронизации и ко второму входу блока анализа кадра передачи 1, первый вход которого соединен с информационным входом устройства контроля ошибок в цифровых системах передачи на базе технологии Ethernet, третий, четвертый выходы, четвертый и пятый входы блока анализа кадра передачи 1 подключены соответственно к третьему, второму входам и пятым, шестым выходам блока управления передачи 3, первый выход которого подключен ко второму входу счетчика единичных импульсов передачи 2, а второй и третий выходы подключены соответственно к четвертому и третьему входам блока памяти передачи 4, четвертый, седьмой и восьмой выходы блока управления передачи 3 подключены соответственно ко второму, четвертому и третьему входам блока определения параметров передачи 5, первый, второй выходы и первый вход блока определения параметров передачи 5 подключены соответственно к первому, второму входам и второму выходу блока памяти передачи 4, первый выход которого является информационной шиной и подключен к третьему входу блока анализа кадра передачи 1, второй выход которого соединен с первым входом счетчика единичных импульсов передачи 2, выход которого подключен к пятому входу блока памяти передачи 4.

Блок анализа кадра передачи 1 (фиг. 2) предназначен для отбрасывания из кадра Ethernet преамбулы, начального ограничителя кадра (Start-of-frame-delimiter), поля контрольной суммы (Frame Check Sequence, FCS), выделения заголовка и блока данных для последующего анализа. Блок анализа кадра передачи содержит таймер 9.6 мкс 1.1, регистр сдвига 1.2, электронный ключ 1.3, элемент И 1.4, D-триггер 1.5, счетчик до ста двадцати восьми 1.6, счетчик единичных интервалов времени 1.7, делитель на восемь 1.8, выход которого является третьим выходом блока анализа кадра передачи 1. Третий вход делителя на восемь 1.8 подключен к пятому входу блока анализа кадра передачи 1 и к четвертому входу счетчика единичных интервалов времени 1.7, третий вход которого подключен ко второму входу счетчика до ста двадцати восьми 1.6, к первому входу электронного ключа 1.3, ко второму входу блока анализа кадра передачи 1 и ко второму входу таймера 9.6 мкс 1.1, выход которого соединен с первым входом счетчика единичных интервалов времени вторым входом делителя на восемь 1.8, вторым входом D-триггера 1.5 и с третьим входом регистра сдвига 1.2, первый, второй выходы и четвертый вход которого подключены соответственно к первому и второму выходам и к третьему входу блока анализа кадра передачи 1, четвертый выход которого подключен к выходу D-триггера 1.5, а четвертый вход - ко второму входу электронного ключа 1.3, выход которого соединен со вторым входом регистра сдвига 1.2, первый вход которого подключен к первому входу таймера 9.6 мкс 1.1 и к первому входу блока анализа кадра передачи 1, а третий и четвертый выходы регистра сдвига 1.2 подключены соответственно ко второму и первому входу элемента И 1.4, выход которого соединен с первым входом D-триггера 1.5 и с первым входом счетчика до ста двадцати восьми 1.6, выход которого соединен со вторым входом счетчика единичных интервалов времени 1.7, выход которого подключен к первому входу делителя на восемь, выход которого соединен с третьим выходом блока кадра передачи 1.

Счетчик единичных импульсов передачи 2 и счетчик единичных импульсов приема 8 идентичны и предназначены для определения числа единичных символов в каждом j-м из n шестиразрядных сегментов выделенных последовательностей N(1)j и представления этого числа в двоичном коде.

Блок управления передачи 3 и блок управления приема 9 идентичны и предназначены для выработки управляющих сигналов с целью реализации требуемого алгоритма преобразования сигнала и могут быть реализованы на микроконтроллере фирмы Atmel AT 89S8253.

Блок памяти передачи 4 и блок памяти приема 10 идентичны и предназначены для запоминания значений числа единичных символов в каждом j-м из n шестиразрядных сегментов, а также значений параметров усечения Y и K поля анализируемых данных кадра Ethernet, хранения их и выдачи требуемых значений в соответствующие блок определения параметров передачи 5 и блок определения параметров приема 12. В качестве блока памяти может быть использовано устройство на микросхеме памяти К537РУ8 [Корнейчук В.И., Тарасенко В.П. Вычислительные устройства на микросхемах: Справочник. - К.: Техника, 1988. С.85-87].

Блок определения параметров передачи 5 (фиг. 3) и блок определения параметров приема 12 идентичны и предназначены для определения значений параметров информационных последовательностей: математического ожидания m(1), дисперсии d(1), вероятности появления единичного символа p(1), а также значений параметров усечения Y и K. Структурная схема блока определения параметров передачи 5 (фиг. 3) и блока определения параметров приема 12 состоит из вычитателей 5.1, 5.11, 5.13, сумматоров 5.3, 5.6, 5.8, умножителя 5.2, делителей 5.4, 5.5, 5.7, 5.9, 5.10, 5.12, регистра сдвига 5.14, шифраторов 5.15, 5.16.

Первый вход блока определения параметров подключен к входам А регистра сдвига 5.14 и сумматора 5.3, выход которого соединен с его же входом В и с входом А делителя 5.4, выход которого подключен к входу делителя 5.5, к входу А вычитателя 5.11, к входам В вычитателя 5.8 и сумматора 5.1. Вход А сумматора 5.1 соединен с выходом регистра сдвига 5.14, а выход сумматора 5.1 подключен параллельно к входам А и В умножителя 5.2, выход которого соединен с входом А сумматора 5.6. Выход сумматора 5.6 подключен к его же входу В и к входу А делителя 5.7, выход которого соединен с входами А делителей 5.10 и 5.9, выход которого подключен к входу А сумматора 5.8, выход которого соединен с входом делителя 5.12. Выход делителя 5.12 подключен к входу А шифратора 5.16, выход которого является втором выходом блока определения параметров 5, первый выход которого соединен с выходом шифратора 5.15, вход А которого подключен к выходу вычитателя 5.11, вход В которого соединен с выходом делителя 5.10, вход В которого подключен к выходу вычитателя 5.13, вход А которого соединен со вторым входом блока определения параметров 5. Вход В вычитателя 5.13 соединен со входом В делителя 5.9 и с выходом делителя 5.5. Третий вход блока определения параметров 5 соединен с входами В делителей 5.4 и 5.7 и входом С сумматора 5.6. Четвертый вход блока определения параметров 5 соединен со входами В шифраторов 5.15, 5.16 регистра сдвига 5.14 и входом С сумматора 5.3.

Блок анализа кадра приема 7 (фиг. 4) содержит таймер 9.6 мкс 7.1, блок памяти контроля 7.2, регистр сдвига 7.3, электронный ключ 7.4, элемент И 7.5, D-триггер 7.6, счетчик до ста двадцати восьми 7.7, счетчик единичных интервалов времени 7.8, делитель на восемь 7.9, выход которого является третьим выходом блока анализа кадра приема 7, третий вход делителя на восемь 7.9 подключен к четвертому входу блока анализа кадра приема 7 и к четвертому входу счетчика единичных интервалов времени 7.8, третий вход которого подключен ко второму входу счетчика до ста двадцати восьми 7.7, к первому входу электронного ключа 7.4, ко второму входу блока анализа кадра приема 7 и ко второму входу таймера 9.6 мкс 7.1, выход которого соединен: с первым входом счетчика единичных интервалов времени 7.8, со вторым входом делителя на восемь 7.9, со вторым входом D-триггера 7.6 и с первым входом блока памяти контроля 7.2, выход которого соединен с пятым выходом блока анализа кадра передачи 7, а второй вход блока памяти контроля 7.2 соединен с пятым выходом регистра сдвига 7.3, первый и второй выходы которого подключены соответственно к первому и второму выходам блока анализа кадра приема 7, четвертый выход которого подключен к выходу D-триггера 7.6, а третий вход - ко второму входу электронного ключа 7.4, выход которого соединен со вторым входом регистра сдвига 7.3, первый вход регистра сдвига 7.3 подключен к первому входу таймера 9.6 мкс 7.1 и к первому входу блока анализа кадра приема 7, а третий и четвертый выходы регистра сдвига 7.3 подключены соответственно ко второму и первому входу элемента И 7.5, выход которого соединен с первым входом D-триггера 7.6 и с первым входом счетчика до ста двадцати восьми 7.7, выход которого соединен со вторым входом счетчика единичных интервалов времени 7.8, выход которого подключен к первому входу делителя на восемь 7.9.

Компаратор 11 предназначен для сравнения значений параметров усечения Y и K, вычисленных в блоке определения параметров приема 12, со значениями Υ0 и Κ0, вычисленными в блоке определения параметров передачи 5 и принятии решения о наличии или отсутствии ошибки в принятом кадре Ethernet.

Заявленное устройство контроля ошибок в цифровых системах передачи работает следующим образом.

На первом этапе производится определение значений параметров усечения K0, Y0 информационных байтов кадра Ethernet и замена на передающей стороне цифровой системы передачи этими значениями байтов контрольной суммы текущего кадра.

При поступлении на первый вход блока анализа кадра передачи 1 кадра Ethernet (преамбула, включающая в себя семь синхронизирующих байт 01010101) на выходе (Сброс) таймера 9,6 мкс 1.1 появляется сигнал логического «0», поступающий на третий вход регистра сдвига 1.2 (1-12272), тем самым разрешая в него запись. При появлении последовательности начального ограничителя кадра (Start-of-frame-delimiter, SFD 10101011) на выходе элемента И 1.4 появляется сигнал логической «1», поступающий на первый вход счетчика до ста двадцати восьми 1.6, запуская его и переводя D-триггер 1.5 в состояние «1», поступая на его первый вход, на четвертом выходе блока анализа кадра передачи 1 появится сигнал «Начало кадра» (логическая «1»), поступающий на второй вход устройства управления 3. Счетчик до ста двадцати восьми 1.6 по завершении отсчета 128 импульсов синхронизации сформирует сигнал «Начало счета» (логическая «1») ,поступающий с его выхода на второй вход счетчика единичных интервалов времени 1.7. Счетчик единичных интервалов времени 1.7 начинает считать количество единичных интервалов времени импульсов синхронизации, поступающих на третий вход.

При окончании кадра на первом входе таймера 9,6 мкс 1.1 пропадает сигнал и через интервал времени 9,6 мкс на его выходе появится сигнал логической «1», который, поступая:

- на третий вход регистра сдвига 1.2, сбрасывает с 1 по 96 и с 113 по 128 бит информации с конца пакета (96 - последовательность нулей, полученная за последние 9,6 мкс и 16 из 32 бит поля контрольной суммы (Frame Check Sequence, FCS), содержащейся в конце кадра Ethernet);

- на первый вход счетчика единичных интервалов времени 1.7, останавливая его.

В результате с 129 ячейки регистра сдвига 1.2 на втором выходе блока анализа кадра передачи 1 формируется последовательность импульсов кадра Ethernet без контрольной суммы, поступающая на первый вход счетчика единичных импульсов передачи 2. На четвертом выходе блока анализа кадра 1 появится сигнал окончания кадра (логический «0»), поступающий на второй вход блока управления передачи 3. По команде с шестого выхода блока управления передачи 3 на пятый вход блока анализа кадра 1 останавливается подсчет значения интервалов синхронизации счетчиком единичных интервалов времени 1.7 и осуществляется деление этого количества делителем на восемь 1.8, а по поступающей команде с пятого выхода блока управления передачи 3 на четвертый вход блока анализа кадра передачи 1 прекращается тактирование регистра сдвига 1.2. С выхода делителя на восемь 1.8 (третий выход блока анализа кадра передачи 1) на третий вход блока управления передачи 3 подается значение N, необходимое для вычисления параметров усечения.

При поступлении с четвертого выхода блока анализа кадра передачи 1 сигнала «Начало кадра» на второй вход блока управления передачи 3 он формирует управляющий сигнал «Загрузка», поступающий с первого выхода блока управления передачи 3 на второй вход 8-разрядного счетчика единичных импульсов передачи 2. Счетчик единичных импульсов передачи 2 начинает подсчет числа S(1) единичных символов «1» в каждом 8-миазрядном сегменте. После поступления каждого 8-го символа производится считывание значений счетчика единичных импульсов передачи 1.7 путем подачи управляющего сигнала «Код адреса» с третьего выхода блока управления передачи 3 на третий вход блока памяти передачи 4 при наличии сигнала «Запись», поступающего со второго выхода блока управления передачи 3, на четвертый вход блока памяти передачи 4. Значения Sj(1) чисел «1», представленных в двоичном коде, с выхода счетчика единичных импульсов передачи 2 поступают на пятый вход блока памяти передачи 4, являющийся его информационным D-входом, и в соответствии с кодовой комбинацией на адресном X-входе (третий вход) и управляющем Z-входе (четвертый вход) производится запись значений Sj в соответствующие ячейки блока памяти передачи 4. После этого происходит обнуление счетчика единичных импульсов передачи 2 по сигналу «Очистка» на его втором входе.

Параллельно с занесением в блок памяти передачи 4 значений чисел «1» Sj в блоке определения параметров передачи 5 производится вычисление значений математического ожидания mj(1) и дисперсии dj(1) числа «1» в 8-разрядном сегменте и вероятности pj(1) появления «1» в j-й позиции 8-разрядного сегмента, и по результатам вычисления mj(1), dj(1), pj(1) определяют значения параметров усечения K0, Y0.

Со второго выхода блока памяти передачи 4 производится последовательное считывание значений S1j. Эти значения подаются на первый вход сумматора 5.3 и вход регистра сдвига 5.14 блока определения параметров передачи 5, показанного на фиг. 3. В сумматоре 5.3 производится суммирование всех j-x значений S1j выделенных N 8-разрядных сегментов путем сложения каждого j-го значения S1j с суммой предыдущих, поступающих с выхода сумматора 5.3 на его второй вход: ∑ j = 1 N S 1 j . При подаче на первый вход сумматора 5.3 N-го значения S1j и получения на его выходе суммарного значения единичных символов S1 в выделенных N 8-разрядных сегментах это значение считывают.

Сигнал с выхода сумматора 5.3 подается на вход делителя 5.4 с коэффициентом деления N, значение которого поступает с восьмого выхода блока управления передачи 3. В делителе 5.4 выполняется операция деления на число N, то есть производится вычисление среднего значения: m 1 = [ ∑ j = 1 N S 1 j ] / N .

Значение m1 с выхода делителя 5.4 подается на первый вход делителя 5.5, второй вход вычитателя 5.1, второй вход сумматора 5.8 и первый вход вычитателя 5.11. В делителе 5.5 с постоянным коэффициентом деления выполняется операция деления на число 8, то есть производится вычисление вероятности p1 появления "1" в каждой позиции 8-разрядных сегментов: p 1 = [ ∑ j = 1 N S 1 j ] / N × 8 . Значение p1 подается ее второй вход вычитателя 5.13 и второй вход делителя 5.9. В вычитателе 5.13, на первый вход которого подается число "один", представленное в двоичном коде, производится вычисление: 1-p1.

Значение 1-p1 считывается и подается на второй вход второго делителя.

После вычисления значения m1 и подачи его на второй вход вычитателя 5.1 производится вычисление значения дисперсии d1. С выхода регистра сдвига 5.14, время задержки которого определяется временем, необходимым для вычисления значения m1, производится последовательное считывание j-x значений S1j выделенных N 8-разрядных сегментов и подача этих значений на первый вход вычитателя 5.1. В вычитателе 5.1 производится вычисление разности S1j-m1.

Сигнал с выхода вычитателя 5.1 подается на первый и второй входы умножителя 5.2, в котором производится вычисление [S1j-m1]2, результат которого подается на первый вход сумматора 5.6.

После этого производится обнуление вычитателя 5.1 и умножителя 5.2.

В сумматоре 5.6 производится сложение разностей [S1j-m1]2 N раз путем добавления каждого значения [S1j-m1]2 к сумме предыдущих, поступающих с выхода сумматора 5.6 на его второй вход. При подаче на первый вход сумматора 5.6 N-го значения [S1j-m1]2 и выполнения вычислений суммарного значения ∑ j = 1 N [ S 1 j − m 1 ] 2 производится считывание этого значения с выхода сумматора 5.6 на вход делителя 5.7 и обнуление второго сумматора 5.6.

В делителе 5.7 с коэффициентом деления N производится вычисление дисперсии: d 1 = ∑ j = 1 N [ S 1 j − m 1 ] 2 / N . После вычисления d1 производится считывание значения d1, которое подается на первые входы делителей 5.9 и 5.10. На второй вход делителя 5.9 подается значение вероятности p1. В делителе 5.9 производится вычисление отношения d1/p1, результат которого подается на первый вход третьего сумматора 5.8.

В сумматоре 5.8, на второй вход которого подано значение m1, производится вычисление значения m1+d1/p1.

Результат суммирования подается на вход делителя 5.12, в котором производится вычисление и квантование параметра усечения K0=(m1+d1/p1)/8. После вычисления и квантования производится считывание значения K0 и подача этого значения на вход шифратора 5.16, где осуществляется преобразование значения K0 в восьмиразрядный двоичный код. С выхода шифратора 5.16 значение K0 поступает на второй выход блока определения параметров передачи 5 и далее на второй вход блока памяти передачи 4, в котором производится запись значений K0 в соответствующие ячейки памяти.

Параллельно с вычислением значения K0 производится вычисление значения параметра Y0. На второй вход делителя 5.10 подается значение 1-p1, а на его первый вход подано значение d1. В делителе 5.10 производится вычисление отношения d1/(1-p1), результат которого подается на второй вход вычитателя 5.11. В вычитателе 5.11, на первый вход которого подано значение m1, производится вычисление и квантование параметра усечения Y0=m1-d1/(1-p1). После вычисления и квантования производится считывание значения Y0 и подача этого значения на вход шифратора 5.15, где значение Y0 преобразуется в восьмиразрядный двоичный код. С выхода шифратора 5.15 значение Y0 поступает на первый выход блока определения параметров передачи 5 и далее на первый вход блока памяти передачи 4, в котором производится запись значений Y0 в соответствующие ячейки памяти. С первого выхода блока памяти передачи 4 производится считывание восьмиразрядных двоичных значений параметров усечения K0, Y0 на третий вход блока анализа кадра передачи 1, в котором записываются ячейки регистра сдвига с 97 по 112. Далее происходит сброс всех значений в элементах блока определения параметров передачи 5 по командам с седьмого выхода блока управления передачи 3, поступающей на четвертый вход блока определения параметров передачи 5. После чего по команде с пятого выхода блока управления передачи 3 на четвертый вход блока анализа кадра передачи 1 возобновляется тактирование регистра сдвига 1.2, и модифицированный кадр Ethernet с первого выхода блока анализа кадра передачи 1 поступает на первый вход цифровой системы передачи 6.

На втором этапе работы устройства контроля ошибок в цифровых системах передачи на базе технологии Ethernet производится определение значений параметров усечения K, Y информационных байтов кадра Ethernet, принятых цифровой системой передачи 6, выделение значений параметров усечения K0, Y0 информационных байтов в полученном кадре Ethernet и принятие решения о наличии или отсутствии ошибок.

Принятая информационная последовательность импульсов кадра Ethernet (преамбула семь синхронизирующих байт 01010101) с первого выхода цифровой системы передачи 6 поступает на первый вход блока анализа кадра приема 7. На выходе таймера 9,6 мкс 7.1 появляется сигнал логического «0», тем самым устанавливая блок памяти контроля приема 7.2, D-триггер 7.6, счетчик единичных временных интервалов 7.8, делитель на восемь 7.9 в первоначальное состояние и разрешая запись в регистр сдвига 7.3 (1-12240). При появлении последовательности начального ограничителя кадра (Start-of-frame-delimiter, SFD 10101011) на выходе элемента И 7.5 появляется сигнал логической «1», запускающий счетчик до ста двадцати восьми 7.7 и переводящий D-триггер 7.6 в состояние «1», на четвертом выходе блока анализа кадра приема 7 появится сигнал «Начало кадра» (логическая «1»). Счетчик до ста двадцати восьми 7.7 по завершении счета сформирует сигнал «Начало счета» (логическая «1») на втором входе счетчика единичных интервалов времени 7.8. Счетчик единичных интервалов времени 7.8 начинает считать количество единичных интервалов.

При окончании кадра на первом входе таймера 9,6 мкс 7.1 пропадает сигнал и через интервал времени 9,6 мкс на его выходе появится сигнал логической «1», по которому: происходит запись из регистра сдвига 7.3 значений двух последних байтов кадра Ethernet в блок памяти контроля приема 7.2; останавливается счетчик единичных интервалов времени 7.8 и осуществляется деление делителем на восемь 7.9. В результате на втором выходе блока анализа кадра приема формируется последовательность импульсов кадра Ethernet без контрольной суммы, которая поступает на первый вход счетчика импульсов приема 8, являющийся его информационным входом. На четвертом выходе блока анализа кадра приема 7 формируется сигнал окончания кадра, поступающий на второй вход блока управления приема 9. С третьего выхода блока анализа кадра приема 7 на третий вход блока управления приема 9 подается значение N, необходимое для вычисления параметров усечения.

Принцип работы блока определения параметров приема 12, блока памяти приема 10, счетчика единичных импульсов приема 8 идентичны принципу работы блока определения параметров передачи 5, блока памяти передачи 4, счетчика единичных импульсов передачи 2, которые рассмотрены выше.

В компараторе 11 производится сравнение значений параметров усечения K0, Y0, вычисленных для информационных байтов переданного кадра Ethernet, со значениями параметров усечения K, Υ, вычисленными для информационных байтов принятого кадра Ethernet.

В результате сравнения на выходе компаратора 11 при совпадении параметров усечения будет формироваться сигнал «0», а при несовпадении - сигнал «1», которые поступают на вход блока управления приема 9. При поступлении сигнала «0» на четвертый вход блок управления приема 9, на шестом выходе которого формируется команда возобновления тактирования регистра сдвига 7.3, поступающая на третий вход блока анализа кадра приема 7, и информационная последовательность поступает на первый выход блока анализа кадра приема 7, являющегося информационным выходом устройства контроля ошибок в цифровых системах передачи на базе технологии Ethernet. В случае появления на четвертом входе блока управления приема 9 сигнала «1» принятый кадр Ethernet отбрасывается как принятый с ошибкой.

Входящие в общую структуру устройства контроля ошибок в цифровых системах передачи на базе технологии Ethernet элементы являются типовыми и могут быть технически реализованы в настоящее время при использовании имеющейся элементной базы.

Схемы счетчиков известны и могут быть реализованы на микросхеме К176ИЕ2 [Шило В.Л. Популярные цифровые микросхемы". - М.: Радио и связь, 1987. С. 235-236, рис. 2.36, а].

Используемые в заявленном устройстве элементы И-НЕ и регистр сдвига могут быть выполнены на микросхемах К155ЛА3 и микросхеме К155ИР1.

Схемы сумматоров и вычитателей могут быть реализованы, например, на микросхеме К155ИП4 [Батушев В.А., Вениаминов В.Н. и др. Микросхемы и их применение: Справочное пособие. - М.: Радио и связь, 1983. С. 129-130].

Схема умножителя может быть реализована на микросхеме К155ИП4 [Батушев В.А., Вениаминов В.Н. и др. Микросхемы и их