Преобразование инициируемого сообщениями прерывания в уведомление о генерированном адаптером ввода-вывода событии

Иллюстрации

Показать всеГруппа изобретений относится к компьютерной технике и может быть использована для обработки прерываний в вычислительной среде. Техническим результатом является облегчение управления запросами прерывания. Описано преобразование одного или нескольких запросов, инициируемых сообщениями прерываний, поступающих от одного или нескольких адаптеров ввода-вывода, в уведомления о генерированном адаптером ввода-вывода событии. Каждое уведомление содержит набор из одного или нескольких конкретных индикаторов в системной памяти и запрос прерывания, при этом первый из индикаторов является индикатором ожидающего ответа запроса адаптерного прерывания. Пока запрос адаптерного прерывания ожидает ответа, последующие запросы, инициируемые сообщениями прерываний, преобразуются в уведомления, но без генерирования дополнительных запросов адаптерного прерывания. 2 н. и 6 з.п. ф-лы, 34 ил.

Реферат

Область техники

Настоящее изобретение относится в целом к обработке прерываний в вычислительной среде, более точно к обработке прерываний, генерируемых адаптерами вычислительной среды.

Уровень техники

Инициируемое сообщениями прерывание (MSI) является одним из способов, которым функция адаптера, такая как функция шины взаимодействия периферийных компонентов (PCI), генерирует прерывание центрального процессора (ЦП), чтобы уведомить операционную систему о возникновении какого-либо события или о присутствии какого-либо состояния. MSI является альтернативой, заменяющей выделенный вывод прерываний в каждом устройстве. Когда функция адаптера сконфигурирована на использование MSI, она запрашивает прерывание путем выполнения MSI-операции записи заданного числа байтов данных в особый адрес. Комбинация этого особого адреса и уникального значения данных именуется вектором MSI.

Некоторые функции адаптера поддерживают только один вектор MSI; другие функции адаптеров поддерживают множество векторов MSI. Для функций, которые поддерживают множество векторов MSI, используется одинаковый особый адрес с различными значениями данных.

Во многих вычислительных платформах драйвер устройства автоматически конфигурируется как обработчик прерываний, привязанный к вектору MSI. Тем самым вектор MSI эффективно привязывается к записи в векторе прерываний ЦП. Соответственно, когда функция адаптера поддерживает множество векторов MSI и сконфигурирована на использование множества векторов MSI, она расходует соответствующее число записей в векторе прерываний ЦП.

В заявке US 2007/0271559 A1 на имя Easton и др. под названием "Virtualization of Infiniband Host Channel Adapter Interruptions", опубликованной 22 ноября 2007 г., описаны способ, система, программный продукт, способ и структура компьютерных данных для обеспечения двух уровней виртуализации сервера. Первый гипервизор позволяет множеству логических разделов совместно использовать набор ресурсов и обеспечивает первый уровень виртуализации. Второй гипервизор позволяет множеству независимых виртуальных машин совместно использовать ресурсы, которые выделены одному логическому разделу, и обеспечивает второй уровень виртуализации. Все события для всех виртуальных машин в пределах одного логического раздела группируются в очередь принадлежащих одному разделу событий для приема уведомлений о событии от совместно используемых ресурсов этого одного логического раздела. Машина оповещает о запросе прерывания для сгруппированных событий из очереди принадлежащих одному разделу событий с целью разделения сгруппированных событий из очереди принадлежащих одному разделу событий на отдельные виртуализированные очереди событий, которые распределяются из расчета на каждую виртуальную машину.

В заявке US 2005/0289271 A1 на имя Martinez и др. под названием "Circuitry to Selectively Produce MSI Signals", опубликованной 29 декабря 2005 г., в некоторых вариантах осуществления описана микросхема, содержащая схему регистра состояния, связанную с проводниками и служащую для приема сигналов прерывающих событий и передачи сигналов источника, которые соответствуют сигналам прерывающих событий. Микросхема также содержит схему управляющего регистра для передачи активирующих источник сигналов выборочным источникам прерываний и логическую схему повторной активации, связанную с проводниками и служащую для приема сигналов прерывающих событий и передачи сигнала повторной активации. Микросхема дополнительно содержит первую логическую схему для приема сигналов источника, активирующих источник сигналов и сигнала повторной активации и генерирования сигнала первоначального прерывания и логическую схему генерирования импульсов сигнала инициируемого сообщениями прерывания (MSI) для приема сигнала первоначального прерывания и передачи сигнала MSI в ответ на него. Также описаны и заявлены другие варианты осуществления.

В патенте US 7562366 под названием "Transmit Completion Event Batching", выданном 14 июля 2009 г. на имя Pope и др., описан способ управления очередью передачи данных для применения в хост-машине и устройстве сопряжения с сетью. В общих чертах, хост-машина записывает дескрипторы буфера данных в очередь дескрипторов передачи, а устройство сопряжения с сетью записывает события с целью уведомления хост-машины о завершении им обработки буфера передаваемых данных. Каждый из дескрипторов события завершения передачи уведомляет хост-машину о завершении обработки одного из множества буферов передаваемых данных.

В публикации "Chapter 6: Configuration Space" in: PCI-SIG: "PCI Local Bus Specification Revision 3.0", 3 февраля 2004 г., ХР002638677, стр.213-254 описано устройство PCI, имеющее память, в которой хранится конфигурационное пространство.

В заявке US 2006/195617 A1 на имя Arndt Richard L и др., поданной 31 августа 2006 г., описан хорошо известный номер функции подключенного к шине устройства (BDF, от английского - Bus-Device Function).

Раскрытие изобретения

Согласно одной из особенностей настоящего изобретения предложено средство, облегчающее управление запросами прерывания, поступающими от адаптеров.

Преодоление недостатков известного уровня техники и обеспечение преимуществ достигается за счет предложенного способа по п.1 и соответствующей системы и компьютерного программного продукта для управления запросами прерывания в вычислительной среде.

Краткое описание чертежей

Одна или несколько особенностей настоящего изобретения конкретно охарактеризованы и отдельно заявлены в формуле изобретения, следующей за описанием. Перечисленные выше и другие задачи, признаки и преимущества изобретения станут ясны из следующего далее подробного описания в сочетании с сопровождающими его чего чертежами, на которых:

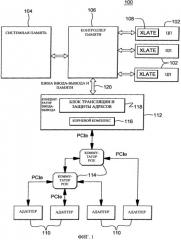

на фиг.1 проиллюстрирован один из вариантов осуществления вычислительной среды, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

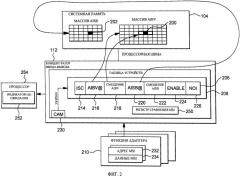

на фиг.2 - один из вариантов осуществления дополнительных подробностей показанных на фиг.1 системной памяти и концентратора ввода-вывода согласно одной из особенностей настоящего изобретения,

на фиг.3A-3Б - примеры распределения векторов разрядов адаптерных прерываний согласно одной из особенностей настоящего изобретения,

на фиг.3В-3Г - примеры распределения суммарных разрядов адаптерных прерываний согласно одной из особенностей настоящего изобретения,

на фиг.4 - один из вариантов осуществления общего представления логики, выполняемой во время инициализации с целью конфигурирования функции адаптера для уведомления о генерированном адаптером ввода-вывода событии согласно одной из особенностей настоящего изобретения,

на фиг.5 - один из вариантов осуществления логики, выполняемой с целью регистрации, обеспечивающей преобразование инициируемого сообщениями прерывания (MSI) в уведомление о генерированном адаптером ввода-вывода событии согласно одной из особенностей настоящего изобретения;

на фиг.6A - один из вариантов осуществления логики с целью преобразования запроса MSI в уведомление о генерированном адаптером ввода-вывода событии согласно одной из особенностей настоящего изобретения;

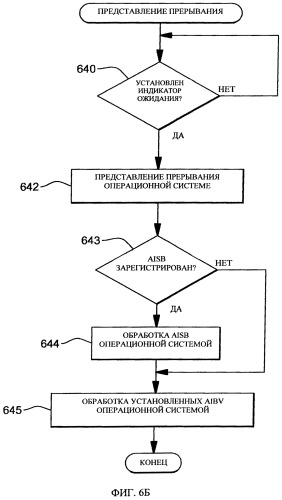

на фиг.6Б - один из вариантов осуществления логики с целью представления операционной системе уведомления о генерированном адаптером ввода-вывода событии согласно одной из особенностей настоящего изобретения,

на фиг.7A - один из вариантов осуществления команды изменения управления функцией шины PCI (Modify PCI Function Controls), используемой согласно одной из особенностей настоящего изобретения,

на фиг.7Б - один из вариантов осуществления поля, используемого проиллюстрированной на фиг.7A командой изменения управления функцией шины PCI согласно одной из особенностей настоящего изобретения,

на фиг.7B - один из вариантов осуществления другого поля, используемого проиллюстрированной на фиг.7A командой изменения управления функцией шины PCI согласно одной из особенностей настоящего изобретения,

на фиг.7Г - один из вариантов осуществления содержимого блока информации о функциях (function information block (FIB)), используемого согласно одной из особенностей настоящего изобретения,

на фиг.8 - один из вариантов осуществления общего представления логики команды изменения управления функцией шины PCI согласно одной из особенностей настоящего изобретения,

на фиг.9 - один из вариантов осуществления логики, связанной с операцией регистрации адаптерных прерываний, которая может быть задана командой изменения управления функцией шины PCI согласно одной из особенностей настоящего изобретения,

на фиг.10 - один из вариантов осуществления логики, связанной с операцией отмены регистрации адаптерных прерываний, которая может быть задана командой изменения управления функцией шины PCI согласно одной из особенностей настоящего изобретения,

на фиг.11A - один из вариантов осуществления команды вызова логического процессора (Call Logical Processor), используемой согласно одной из особенностей настоящего изобретения,

на фиг.11Б - один из вариантов осуществления блока запроса, используемого проиллюстрированной на фиг.11A командой вызова логического процессора для операции формирования списков согласно одной из особенностей настоящего изобретения,

на фиг.11B - один из вариантов осуществления блока ответа для проиллюстрированной на фиг.11Б операции формирования списков согласно одной из особенностей настоящего изобретения,

на фиг.11Г - один из вариантов осуществления записи в списке функций, используемой согласно одной из особенностей настоящего изобретения,

на фиг.12A - один из вариантов осуществления блока запроса, используемого проиллюстрированной на фиг.11A командой вызова логического процессора для операции запроса функции согласно одной из особенностей настоящего изобретения,

на фиг.12Б - один из вариантов осуществления блока ответа для проиллюстрированной на фиг.12A операции запроса функции согласно одной из особенностей настоящего изобретения,

на фиг.13A - один из вариантов осуществления блока запроса, используемого проиллюстрированной на фиг.11A командой для операции запроса группы функций согласно одной из особенностей настоящего изобретения,

на фиг.13Б - один из вариантов осуществления блока ответа для проиллюстрированной на фиг.13A операции запроса группы функций согласно одной из особенностей настоящего изобретения,

на фиг.14 - один из вариантов осуществления компьютерного программного продукта, в котором содержится одна или несколько особенностей настоящего изобретения,

на фиг.15 - один из вариантов осуществления хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг.16 - один из дополнительных примеров компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг.17 - другой пример компьютерной системы, представляющей собой компьютерную сеть, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг.18 - один из вариантов осуществления различных элементов компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг.19A - один из вариантов осуществления блока выполнения проиллюстрированной на фиг.18 компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг.19Б - один из вариантов осуществления блока перехода проиллюстрированной на фиг.18 компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг.19B - один из вариантов осуществления блока загрузки/сохранения проиллюстрированной на фиг.18 компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения, и

на фиг.20 - один из вариантов осуществления эмулируемой хост-компьютерной системы, эмулируемой хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

Подробное описание осуществления изобретения

Согласно одной из особенностей настоящего изобретения предложено средство преобразования запроса инициируемого сообщениями прерывания (MSI) в уведомление о генерированном адаптером ввода-вывода событии. MSI генерируется адаптером и преобразуется в уведомление о генерированном адаптером событии, в котором установлен один или несколько конкретных индикаторов, и запрашивается представление прерывания операционной системе (или другому программному обеспечению, такому как другие программы и т.д. Используемый в описании термин "операционная система" включает драйверы операционной системы). В одном из частных вариантов осуществления запрос прерывания передается операционной системе в результате не каждого запроса MSI, и вместо этого один запрос прерывания соответствует множеству запросов MSI.

Используемый в описании термин "адаптер" означает адаптер любого типа (например, адаптер памяти, сетевой адаптер, адаптер обработки, криптографический адаптер, адаптер на основе шины PCI, адаптеры ввода-вывода другого типа и т.д.). В одном из вариантов осуществления адаптер содержит одну функцию. Тем не менее, в других вариантах осуществления адаптер может содержать множество функций. В зависимости от того, содержит ли адаптер одну функцию или множество функций, применима одна или несколько особенностей настоящего изобретения. Кроме того, в представленных примерах термин адаптер используется взаимозаменяемо с термином функция адаптера (например, функция шины PCI), если не указано иное.

Далее со ссылкой на фиг.1 будет описан один из вариантов осуществления вычислительной среды, в которой содержится и используется одна или несколько особенностей настоящего изобретения. В одном из примеров вычислительной средой 100 является сервер System z®, предлагаемый International Business Machines Corporation. Основой сервера System z® является z/Architecture®, предлагаемая International Business Machines Corporation. Подробности, касающиеся z/Architecture, описаны в публикации IBM №SA22-7832-07 под названием "z/Architecture-Principles of Operation" (февраль 2009 г.). IBM®, System z® и z/Architecture® являются зарегистрированными товарными знаками International Business Machines Corporation (Армонк, штат Нью-Йорк, США). Другие названия, используемые в заявке, могут являться зарегистрированными товарными знаками, товарными знаками или названиями продуктов International Business Machines Corporation или других компаний.

В одном из примеров вычислительная среда 100 содержит один или несколько центральных процессоров (ЦП) 102, связанных с системной памятью 104 (иначе называемой основной памятью) посредством контроллера 106 памяти. Для доступа к системной памяти 104 центральный процессор 102 передает запрос чтения или записи, в котором содержится адрес, используемый для доступа к системной памяти. Поскольку адрес, содержащийся в запросе, обычно не может непосредственно использоваться для доступа к системной памяти, он транслируется в адрес, который может непосредственно использоваться для доступа к системной памяти. Адрес преобразуется посредством механизма 108 трансляции (XLATE). Например, адрес транслируется из виртуального адреса в действительный или абсолютный адрес с использованием, например, динамической трансляции адреса (DAT).

Запрос, содержащий адрес (при необходимости транслированный), принимается контроллером 106 памяти. В одном из примеров контроллер 106 памяти состоит из аппаратного обеспечения и используется для арбитража при доступе к системной памяти и для обеспечения непротиворечивости памяти. Этот арбитраж осуществляется применительно к запросам, принимаемым от ЦП 102, а также запросам, принимаемым от одного или нескольких адаптеров 110. Подобно центральным процессорам адаптеры передают системной памяти 104 запросы на получение доступа к системной памяти.

В одном из примеров адаптером 110 является адаптер шины межсоединения периферийных компонентов (PCI) или адаптер на основе шины PCI Express (PCIe), содержащей одну или несколько функций шины PCI. Функция шины PCI передает запрос, который маршрутизируется в концентратор 112 ввода-вывода (например, концентратор шины PCI) посредством одного или нескольких коммутаторов (например, коммутаторов шины PCIe) 114. В одном из примеров концентратор ввода-вывода состоит из аппаратного обеспечения, включающего один или несколько конечных автоматов.

Концентратор ввода-вывода содержит, например, корневой комплекс 116, который принимает запрос от коммутатора. В запросе содержится адрес ввода-вывода, который используется, например, для осуществления прямого доступа к памяти (DMA) или передачи запроса инициируемого сообщениями прерывания (MSI). Этот адрес предоставляется блоку 118 трансляции и защиты адресов, который осуществляет доступ к информации, используемой для DMA или запроса MSI.

В случае DMA блок 118 трансляции и защиты адресов может транслировать адрес в адрес, применимый для доступа к системной памяти. Затем инициированный адаптером запрос, содержащий транслированный адрес, предоставляется контроллеру 106 памяти посредством, например, шины 120 ввода-вывода и памяти. Контроллер памяти осуществляет арбитраж и в соответствующее время пересылает системной памяти запрос с транслированным адресом.

В случае запроса MSI блок 118 трансляции и защиты адресов получает информацию для облегчения преобразования запроса MSI в уведомление о генерированном адаптером ввода-вывода событии. Поскольку описанные варианты осуществления относятся к обработке прерываний, дополнительные подробности, касающиеся концентратора ввода-вывода и системной памяти в том, что касается обработки прерываний, описаны со ссылкой на фиг.2. Хотя на фиг.2 не показан контроллер памяти, он может использоваться. Концентратор ввода-вывода может быть связан с системной памятью 104 и/или процессором 254 напрямую или посредством контроллера памяти.

Как показано на фиг.2, в одном из примеров системная память 104 содержит одну или несколько структур данных, применимых для облегчения обработки прерываний. В этом примере системная память 104 содержит вектор 200 разрядов адаптерного прерывания (AIBV, от английского - Adapter Interruption Bit Vector) и необязательный суммарный разряд 202 адаптерного прерывания (AISB, от английского - Adapter Interruption Summary Bit), соответствующий конкретному адаптеру. Для каждого адаптера может иметься AIBV и соответствующий AISB.

В одном из примеров вектор 200 разрядов адаптерного прерывания представляет собой одномерный битовый массив из одного или нескольких разрядов в основном запоминающем устройстве, привязанных к адаптеру (например, функции шины PCI). Разряды в векторе разрядов адаптерного прерывания отображают номера векторов MSI. Разряд, который приравнен в AIBV к единице, указывает состояние или тип события для соответствующего адаптера. В примере с функцией шины PCI каждый разряд в соответствующем AIBV отображает вектор MSI. Соответственно, если функция шины PCI поддерживает только вектор MSI, ее AIBV содержит один разряд; если функция шины PCI поддерживает множество векторов MSI, ее AIBV содержит по одному разряду на вектор MSI. В примере, проиллюстрированном на фиг.2, функция шины PCI поддерживает множество векторов MSI (например, 3), и, соответственно, AIBV 200 содержит множество разрядов (например, 3). Каждый разряд соответствует конкретному событию, например, когда для нулевого разряда AIBV установлено значение, равное единице, он обозначает завершенную операцию; когда для единичного разряд AIBV установлено значение, равное единице, он соответствует событию ошибки; и т.д. Как показано, в этом примере установлен единичный бит.

В одном из частных вариантов осуществления с целью указания AIBV для функции шины PCI используется определенная команда (например, команда изменения управления функцией шины PCI). В частности, команда передается операционной системой и указывает идентификатор функции шины PCI, адрес ячейки основного запоминающего устройства в области, в которой содержится AIBV, смещение от этой ячейки до первого разряда AIBV и число разрядов, входящих в AIBV. В частности, с помощью этой команды параметры адаптерного прерывания копируются из блока информации о функциях, в котором хранится такая информация (например, полученная в результате инициализации и/или конфигурирования) в запись в таблице устройств адаптера (описанную далее) и/или запись в таблице функций (описанную далее).

В одном из примеров идентификатором функции шины PCI является дескриптор функции. Дескриптор функции включает, например, разрешающий индикатор, который указывает, активирован ли дескриптор функции шины PCI; номер функции шины PCI, который указывает функцию (является статическим идентификатором); и номер экземпляра, указывающий конкретный экземпляр этого дескриптора функции. Например, при каждом активировании дескриптора функции номер экземпляра увеличивается, и указывается новый номер экземпляра. Дескриптор функции используется для обнаружения записи в таблице функций, в которой содержится одна или несколько записей. Например, в качестве индекса в таблице функций для обнаружения конкретной записи в таблице функций используется один или несколько разрядов дескриптора функции. Запись в таблице функций содержит информацию о соответствующей функции шины PCI. Например, она может содержать различные индикаторы состояния соответствующей функции адаптера и один или несколько индексов записей в таблице устройств, которые используются для обнаружения записей в таблице устройств для этой функции адаптера. (В одном из вариантов осуществления дескриптором для операционной системы является просто непрозрачный идентификатор адаптера.)

AIBV может находиться на любой байтовой границе и любой битовой границе. Это позволяет операционной системе гибко упаковывать AIBV множества адаптеров в смежный битовый и байтовый диапазон. Например, как показано на фиг.3A, в одном из примеров операционная система выделила общую область памяти в местоположении X, содержащую пять смежных AIBV. Адаптеры, соответствующие каждому AIBV, обозначены буквами A-E. Случай, когда каждый разряд AIBV отображает адаптер, дополнительно обозначен числами 0-n. Свободные разряды обозначены буквой "u" нижнего регистра.

Один из дополнительных примеров проиллюстрирован на фиг.3Б. В этом примере операционная система выделила три однозначно определяемые области памяти в местоположениях X, Y и Z, содержащие AIBV для пяти адаптеров ввода-вывода. Область памяти в местоположении X содержит AIBV для адаптеров A и B, область памяти в местоположении Y содержит AIBV только для адаптера C, а область памяти в местоположении Z содержит AIBV для адаптеров D и E. Случай, когда каждый разряд AIBV отображает адаптер ввода-вывода, дополнительно обозначен числами 0-n. Свободные разряды обозначены буквой "u".

Как показано на фиг.2, помимо AIBV, в этом примере адаптер имеет AISB 202, который содержит один разряд, соответствующий адаптеру. AISB, равный единице, указывает, что в качестве значения одного или нескольких разрядов AIBV, который соответствует AISB, установлена единица. AISB является необязательным, и может быть предусмотрен один AISB для каждого адаптера, один AISB каждого выбранного адаптера или один AISB для группы адаптеров.

В одном из частных случаев реализации функции шины PCI с целью указания AISB для функции шины PCI используется определенная команда (например, команда изменения управления функцией шины PCI). В частности, команда передается операционной системой и указывает идентификатор функции шины PCI (например, дескриптор), адрес ячейки основного запоминающего устройства в области, в которой содержится AISB, смещение от этой ячейки до AISB и управление разрешением суммарного уведомления об адаптерном прерывании с указанием суммарного разряда.

AISB может находиться на любой байтовой границе и любой битовой границе. Это позволяет операционной системе гибко упаковывать AISB множества адаптеров в смежный битовый и байтовый диапазон. В одном из примеров, проиллюстрированных на фиг.3B, операционная система выделила общую область памяти в местоположении X, содержащую девять смежных AISB. Адаптеры, соответствующие каждому AISB, обозначены буквами A- I. Свободные разряды обозначены буквой "u" нижнего регистра.

Один из дополнительных примеров распределения проиллюстрирован на фиг.3Г, где операционная система выделила три однозначно определяемых адреса хранения AISB в местоположениях X, Y и Z, в которых содержатся AISB каждого из трех адаптеров. Адаптеры, соответствующие каждому AISB, обозначены буквами A-C. Свободные разряды обозначены буквой "u" нижнего регистра.

Кроме того, программа также может выделить один AISB множеству функций шины PCI. В этом случае множество AIBV соответствует одному суммарному разряду. Соответственно, таким AISB является тот, который указывает, что операционной системе следует просмотреть множество AIBV.

Как показано на фиг.2, в одном из примеров AIBV и AISB указаны в адресах, которые содержатся в записи 206 в таблице 208 устройств, находящейся в концентраторе 112 ввода-вывода. В одном из примеров таблица 208 устройств находится в блоке трансляции и защиты адресов концентратора ввода-вывода.

Таблица 208 устройств содержит одну или несколько записей 206, каждая из которых закреплена за конкретной функцией адаптера 210. Запись 206 содержит несколько полей, которые могут быть заполнены с использованием, например, упомянутых выше команд. Значения одного или нескольких из полей зависят от политики и/или конфигурации. Примеры полей включают:

поле 214 подкласса прерываний (ISC): указывает подкласс прерываний. В поле ISC указан маскируемый класс адаптерного прерывания, для которого может быть установлен приоритет его обработки операционной системой,

поле 216 адреса AIBV (@): указывает, например, абсолютный адрес начала ячейки запоминающего устройства, в которой хранится AIBV для конкретной функции адаптера, которая соответствует этой записи в таблице устройств,

поле 218 смещения AIBV: указывает смещение в ячейке основного запоминающего устройства к началу AIBV,

поле 220 адреса AISB (@): указывает, например, абсолютный адрес начала ячейки запоминающего устройства, в которой хранится AISB для этой функции шины PCI, если операционная система указала AISB,

поле смещения AISB: указывает смещение в ячейке основного запоминающего устройство к AISB,

поле 224 управления разрешением суммарного уведомления об адаптерном прерывании (Enable) 224: указывает, имеется ли AISB,

поле 226 числа прерываний (NOI) 226: указывает максимальное число векторов MSI, допустимых для этой функции шины PCI, при этом ноль означает их отсутствие.

В других вариантах осуществления записи в таблице устройств (DTE) могут содержать больше, меньше или другую информацию.

В одном из вариантов осуществления местоположение записи в таблице устройств, которую использует адаптер для конкретного запроса прерывания, определяют с использованием идентификатора запросчика (RID) (и/или части адреса), содержащегося в запросе, передаваемом адаптером (например, функцией 210 шины PCI). В запросе содержится идентификатор запросчика (например, 16-разрядное значение, указывающее, например, номер шины, номер устройства и номер функции), а также адрес, используемый для прерывания. Запрос, содержащий RID и адрес, передается, например, посредством коммутатора 114, например, ассоциативной памяти (САМ) 230, которая используется для получения заданного значения. Например, в САМ содержится множество записей, каждая из которых соответствует индексу в таблице устройств. Каждая запись в САМ содержит значение RID. Если, например, принятый RID соответствует значению, содержащемуся в записи в САМ, для определения местонахождения записи в таблице устройств используется соответствующий индекс из таблицы устройств. Иными словами, выводимые из САМ данные используются для индексации в таблице 208 устройств. Если соответствие отсутствует, принятый пакет отбрасывается. (В других вариантах осуществления не требуется САМ или другое средство поиска, и RID используется в качестве индекса.) Обнаруженная DTE используется при обработке запроса прерывания, как описано в изобретении.

Чтобы запросить прерывание, функция адаптера 210 передает пакет концентратору ввода-вывода. В этом пакете содержится адрес 232 MSI и сопутствующие данные 234. Концентратор ввода-вывода сравнивает по меньшей мере часть принятого адреса со значением в регистре 250 сравнения MSI. В случае соответствия запрашивается прерывание (например, MSI) в противоположность операции DMA. Причина запроса (т.е. тип произошедшего события) указывается в сопутствующих данных 234. Например, для указания конкретного вектора прерывания (т.е. вектора MSI), который указывает причину (событие), используется один или несколько младших разрядов данных.

Согласно одной из особенностей настоящего изобретения запрос прерывания, принимаемый от адаптера, преобразуется в уведомление о генерированном адаптером ввода-вывода событии. Иными словами, устанавливается один или несколько индикаторов (например, один или несколько AIBV и необязательно AISB), и у операционной системы запрашивается прерывание, если оно уже не запрошено. В одном из вариантов осуществления множество запросов прерывания (например, MSI) от одного или нескольких адаптеров, объединяются в один запрос прерывания, передаваемый операционной системе, но с указанием соответствующих AIBV и AISB. Например, если концентратор ввода-вывода, который уже принял запрос MSI, в свою очередь передал запрос прерывания процессору и прерывание все еще отложено (например, по той или иной причине запрос прерывания не был передан операционной системе (например, прерывания заблокированы)), то, если концентратор принимает один или несколько других MSI, он не запрашивает дополнительные прерывания. Множество запросов MSI заменяются и отображаются единственным запросом прерывания. Тем не менее, устанавливается один или несколько AIBV и необязательно один или несколько AISB.

Дополнительные подробности преобразования MSI (или другого адаптерного запроса прерывания) в уведомление о генерированном адаптером ввода-вывода событии описаны далее со ссылкой на фиг.4-6Б. В частности, на фиг.4 показана различная осуществляемая инициализация; на фиг.5 показан процесс регистрации; на фиг.6А показана логика преобразования MSI в уведомление о генерированном адаптером событии; и на фиг.6Б показана логика представления уведомления о генерированном адаптером ввода-вывода событии операционной системе.

Как показано на фиг.4, в одном из примеров для преобразования запроса MSI в уведомление о генерированном адаптером ввода-вывода событии осуществляется определенная инициализация. Во время инициализации операционная система выполняет ряд шагов конфигурирования адаптера на уведомление о генерированном адаптером событии посредством запроса MSI. В этом примере конфигурируется функция шины PCI, хотя в других вариантах осуществления это могут быть другие адаптеры, включая функции адаптеров других типов.

В одном из вариантов осуществления сначала на шаге 400 определяются функции шины PCI в конфигурации. В одном из примеров для получения списка функций шины PCI, относящихся к запрашивающей конфигурации (например, относящихся к конкретной операционной системе) используется команда (например, команда запроса списка, передаваемая операционной системой). Эта информация извлекается из структуры данных конфигурации, в которой она содержится.

Затем на шаге 402 выбирается одна из функций шины PCI и определяется адрес MSI, который должен использоваться для функции шины PCI, и число векторов MSI, поддерживаемых функцией шины PCI. Адрес MSI определяется на основании характеристик концентратора ввода-вывода и системы, в которой он установлен. Число поддерживаемых векторов MSI зависит от политики и является конфигурируемым.

Кроме того, на шаге 410 выделяется AIBV, а также AISB, если он имеется. В одном из примеров операционная система определяет местоположение AIBV с целью обеспечения эффективной обработки одного или нескольких адаптеров, обычно исходя из класса адаптера. Например, AIBV для адаптеров памяти могут находиться вблизи друг друга. Выделенные AIBV и AISB очищаются путем установки на нуль, и определяется операция регистрации адаптерного прерывания (например, с использованием команды изменения управления функцией шины PCI). Эта операция служит для регистрации на шаге 412 AIBV, AISB, ISC числа прерываний (векторов MSI) и управления разрешением суммарного уведомления об адаптерном прерывании, как подробнее описано далее. После этого на шаге 414 считывается/записывается конфигурационное пространство функции шины PCI. В частности, записываются показания счетчика адреса MSI и вектора MSI в соответствии предыдущими показаниями.

После этого на шаге 416 запроса определяется, содержатся ли в списке дополнительные функции. Если это так, обработка продолжается на шаге 402. В противном случае, обработка в режиме инициализации завершается.

Дополнительные подробности регистрации различных параметров описаны со ссылкой на фиг.5. Сначала выбирается запись в таблице устройств (DTE), соответствующая функции шины PCI, для которой осуществляется инициализация. Этот выбор делается, например, управляющим программно-аппаратным обеспечением, которое выбирает доступную запись из таблицы устройств. После этого на шаге 502 в записи в таблице устройств сохраняются различные параметры. Например, для ISC, адреса AIBV, смещения AIBV, адреса AISB, смещения AISB, управления разрешением и числа прерываний (N01) устанавливаются значения, полученные в результате конфигурирования функции. На этом процесс регистрации завершается.

В контексте настоящего изобретения аппаратно-программное обеспечение содержит, например, микрокод, милликод и/или макрокод процессора. Оно содержит, например, команды аппаратного уровня и/или структуры данных, используемые при реализации высокоуровневого машинного кода. В одном из вариантов осуществления оно содержит, например, собственный код, который обычно представляет собой микрокод, содержащий выверенное программное обеспечение или характерный для базового аппаратного обеспечения и управляющий доступом операционной системы к аппаратному обеспечению системы.

Когда в процессе работы функция шины PCI желает генерировать MSI, она обычно предоставляет операционной системе определенную информацию, описывающую состояние. Это приводит к выполнению одного или нескольких шагов с целью преобразования генерированного функцией шины PCI запроса MSI в уведомление операционной системы о генерированном адаптером ввода-вывода событии. Это описано со ссылкой на фиг.6A.

Как показано на фиг.6A, сначала на шаге 600 регистрируется описание события, в связи с которым запрашивается прерывание. Например, функция шины PCI регистрирует описание события в одной или нескольких предусмотренных для адаптеров структурах регистрации описаний событий, хранящихся, например, в системной памяти. Может регистрироваться тип события, а также дополнительная информация. Кроме того, на шаге 601 функцией шины PCI инициируется запрос с указанием адреса MSI и номера вектора MSI, а также идентификатора запросчика. Этот запрос принимается концентратором ввода-вывода, который в ответ на шаге 602 использует содержащийся в запросе идентификатор запросчика для определения местонахождения записи в таблице устройств для функции шины PCI. Концентратор ввода-вывода на шаге 603 запроса сравнивает по меньшей мере часть адреса, содержащегося в запросе, со значением в регистре сравнения MSI. Если они неодинаковы, MSI не запрашивается. Тем не менее, если они одинаковы, вместо операции прямого доступа к памяти указан адрес MSI и запрошено MSI.

После этого на шаге 604 запроса определяется, является ли номер вектора MSI, указанный в запросе, меньшим или равным числу прерываний (NOI), допустимому для этой функции. Если номер вектора MSI является большим, чем NOI, сообщается об ошибке. В противном случае, концентратор ввода-вывода задает функцию установки разряда для установки соответствующего разряда AIBV в запоминающем устройстве. Соответствующий разряд определяется на шаге 605 путем сложения номера вектора MSI и смещения AIBV, указанного в записи в таблице устройств, и сдвига этого числа разрядов от адреса AIBV, указанного в записи в таблице устройств. Кроме того, если