Устройство для преобразования виртуальных адресов в физические адреса

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в повышении надежности преобразования виртуальных адресов в физические адреса за счет введения контроля за преобразуемым виртуальным адресом. Устройство для преобразования виртуальных адресов в физические адреса содержит элемент памяти с таблицей преобразования адресов первого уровня и кэш-память, причем дополнительно введены многоканальный коммутатор запросов преобразования виртуальных адресов, первые группы входов/выходов которого являются соответствующими группами входов/выходов устройства, и блок управления преобразованием, первая группа входов/выходов которого соединена со второй группой входов/выходов многоканального коммутатора запросов, а вторая группа входов/выходов соединена с группой входов/выходов кэш-памяти, причем третья группа входов/выходов блока управления преобразованием является соответствующей группой входов/выходов устройства, при этом блок управления преобразованием включает в себя управляющий конечный автомат и элемент памяти с таблицей преобразования адресов первого уровня, в которую введены поля размера и смещения, а в каждый канал коммутатора запросов дополнительно введена кэш-память. 2 ил.

Реферат

Изобретение относится к области коммуникационных систем, в частности к механизмам взаимодействия адаптерной платы с памятью вычислительного узла.

Известно устройство для преобразования виртуальных адресов в физические адреса, использующееся в коммуникационной системе EXTOLL (см. http://www.extoll.de/), которое содержит входной интерфейс НТАХ Inport, управляемый конечным автоматом FSM, через который поступают заявки на преобразование виртуальных адресов и ответы на запросы чтения удаленной таблицы преобразования, расположенной в памяти вычислительного узла. Выходы входного интерфейса НТАХ Inport соединены с входами ATU Request FIFO и ATU Reorder Buffer соответственно. Выход очереди поступивших запросов на преобразование виртуальных адресов ATU Request FIFO соединен со входом блока формирования запросов чтения удаленной таблицы преобразования виртуальных адресов ATU Requester, выходы которого соединены со входами последовательной кэш-памяти ранее преобразованных виртуальных адресов TLB и выходным интерфейсом НТАХ Outport. Выход буфера сортировки поступающих ответов на запросы чтения удаленной таблицы преобразования ATU Reorder Buffer соединен с первым входом блока обработки ответов на запросы чтения удаленной таблицы преобразования ATU Responder, второй вход которого соединен со вторым выходом блока формирования запросов чтения удаленной таблицы преобразования виртуальных адресов ATU Requester, третий вход соединен с выходом последовательной кэш-памяти ранее преобразованных виртуальных адресов TLB, а выход соединен со вторым входом выходного интерфейса НТАХ Outport, через который передаются ответы на запросы на преобразование виртуальных адресов и запросы на чтение.

Блоки НТАХ Inport и НТАХ Outport отвечают за взаимодействие с остальной логикой EXTOLL. Request FIFO содержит входящие запросы на преобразование от других блоков EXTOLL. Эти запросы вычитываются блоком ATU Requester. Блок ATU Requester начинает поиск в кэш и одновременно подготавливает запрос на чтение глобальной таблицы преобразования. Когда поиск в кэш завершен, блок Requester либо направляет запрос на чтение глобальной таблицы через НТАХ Outport (в случае кэш-промаха), либо направляет необходимые данные блоку Responder (в случае кэш-попадания). Блок ATU Reorder Buffer принимает входящие ответы, содержащие записи глобальных таблиц преобразования и сортирует их в порядке запросов (так как в системе с HiperTransport ответы на запросы чтения памяти могут приходить в измененном порядке). Отсортированные ответы передаются блоку ATU Responder. Блок ATU Responder получает записи глобальных таблиц либо от блока сортировки, либо из кэш. ATU Responder формирует возвращаемое значение преобразования и передает его через НТАХ Outport блоку, запросившему преобразование.

Вышеуказанное устройство является наиболее близким по технической сущности к заявляемому устройству и поэтому выбрано в качестве прототипа.

Недостатками прототипа являются отсутствие контроля выхода за выделенный массив зарегистрированной памяти, а также одноуровневая система кэширования ранее преобразованных адресов.

Решаемой технической задачей является создание устройства для преобразования виртуальных адресов в физические адреса с повышенной надежностью и производительностью.

Достигаемым техническим результатом является введение контроля за преобразуемым виртуальным адресом, а также введение дополнительного уровня кэширования непосредственно в каналах запроса преобразования виртуальных адресов.

Для достижения технического результата в устройстве для преобразования виртуальных адресов в физические адреса, содержащем элемент памяти с таблицей преобразования адресов первого уровня и кэш память, новым является то, что дополнительно введены многоканальный коммутатор запросов преобразования виртуальных адресов, первые группы входов/выходов которого являются соответствующими группами входов/выходов устройства, и блок управления преобразованием, первая группа входов/выходов которого соединена со второй группой входов/выходов многоканального коммутатора запросов, а вторая группа входов/выходов соединена с группой входов/выходов кэш-памяти, причем третья группа входов/выходов блока управления преобразованием является соответствующей группой входов/выходов устройства, при этом блок управления преобразованием включает в себя управляющий конечный автомат и элемент памяти с таблицей преобразования адресов первого уровня, в которую введены поля размера и смещения, а в каждый канал коммутатора запросов дополнительно введена кэш-память.

Новая совокупность существенных признаков позволяет повысить надежность и производительность. Надежность системы повышается за счет введения в таблице преобразования двух дополнительных полей - размера зарегистрированного блока памяти и смещения этого блока памяти внутри первой страницы памяти. Это позволяет осуществлять контроль выхода за пределы выделенного массива памяти, а также регистрировать память, начинающуюся не с начала страницы. Производительность системы повышается за счет введения дополнительного уровня кэширования непосредственно в каналы запроса преобразования виртуальных адресов.

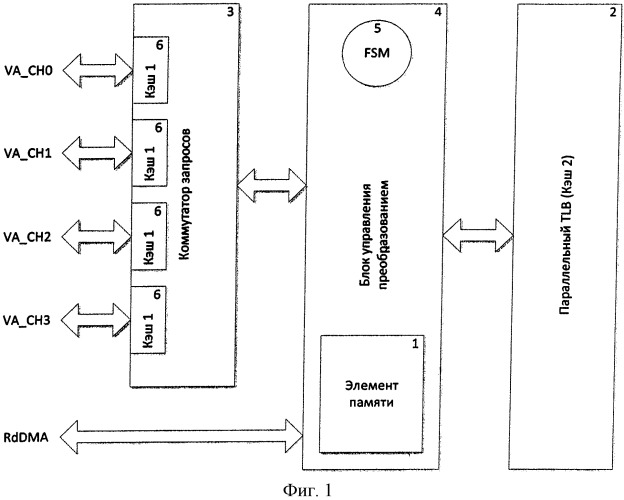

На фигуре 1 представлена блок-схема заявляемого устройства.

Устройство для преобразования виртуальных адресов в физические адреса содержит элемент памяти 1 с таблицей преобразования адресов первого уровня и кэш-память 2, многоканальный коммутатор запросов преобразования виртуальных адресов 3, первые группы входов/выходов которого являются соответствующими группами входов/выходов устройства, и блок управления преобразованием 4, первая группа входов/выходов которого соединена со второй группой входов/выходов многоканального коммутатора запросов 3, а вторая группа входов/выходов соединена с группой входов/выходов кэш-памяти 2, причем третья группа входов/выходов блока управления преобразованием 4 является соответствующей группой входов/выходов устройства, при этом блок управления преобразованием 4 включает в себя управляющий конечный автомат 5 и элемент памяти 1 с таблицей преобразования адресов первого уровня, в которую введены поля размера и смещения, а в каждый канал коммутатора запросов дополнительно введена кэш-память 6.

Устройство работает следующим образом. Каждый канал многоканального коммутатора запросов преобразования виртуальных адресов 3 ожидает запроса на преобразование виртуального адреса. После поступления запроса на преобразование проверяется наличие запрошенного виртуального адреса в кэш-памяти первого уровня 6 ранее преобразованных адресов соответствующего канала. Если удалось найти адрес в кэш-памяти 6, то соответствующий ему физический адрес возвращается через запрашивающий канал. Такая ветвь описывает наиболее быстрый исход преобразования виртуального адреса в физический.

Если в кэш-памяти первого уровня 6 не удалось обнаружить запрашиваемый виртуальный адрес, то многоканальный коммутатор запросов 3 переадресует этот запрос блоку управления преобразованием виртуального адреса 4.

Блок управления преобразованием виртуального адреса 4, получив запрос, обращается к параллельной кэш-памяти второго уровня 2. Если в кэш-памяти второго уровня 2 удается найти соответствующую пару «виртуальный адрес - физический адрес», то преобразование на этом завершается, и найденный физический адрес возвращается многоканальному коммутатору запросов преобразования виртуального адреса 3, который его возвращает запрашивающему каналу и сохраняет его в своей кэш-памяти первого уровня 6.

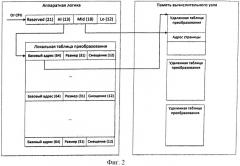

В том случае, если и в кэш-памяти второго уровня 2 не удалось обнаружить виртуальный адрес, то запускается алгоритм преобразования виртуального адреса в физический на основе двухуровневых таблиц преобразования. Структура таблиц преобразования приведена на фигуре 2.

Из таблицы преобразования 1, размещенной в блоке управления преобразованием виртуального адреса 4, для преобразуемого адреса вычитывается описание зарегистрированного блока памяти: физический адрес удаленной таблицы преобразования, размер блока памяти и смещение внутри первой страницы. Затем осуществляется проверка преобразуемого адреса.

Если преобразуемый адрес не выходит за пределы выделенной памяти, то из удаленной таблицы преобразования через канал прямого доступа к памяти RdDMA запрашивается физический адрес, соответствующей заданному виртуальному. После получения ответа от RdDMA, пара «виртуальный адрес - физический адрес» сохраняется в параллельной кэш-памяти второго уровня 2, и результат преобразования возвращается многоканальному коммутатору запросов 3, который его возвращает запрашивающему каналу. Запрашивающий канал также сохраняет преобразованный виртуальный адрес в своей кэш-памяти 6.

В случае ошибки, информация о ней также передается многоканальному коммутатору запросов 3, который передает информацию запрашивающему каналу.

Устройство для преобразования виртуальных адресов в физические адреса прошло проверку и показало свою работоспособность в составе прошивки программируемой логической интегральной схемы, на которой построен адаптерный модуль системы межпроцессорных обменов.

Применение данного устройства позволило в составе адаптерного модуля системы межпроцессорных обменов снизить накладные расходы на обмен данными между адаптерной платой СМПО и памятью вычислительного узла за счет применения метода zero-copy, а также позволило реализовать обмены в парадигме read/write.

На коммуникационных тестах, за счет применения двухуровневого кэширования в устройстве для преобразования виртуальных адресов в физические адреса, удалось получить уменьшение коммуникационной задержки на 1.5 мкс. Дополнительный контроль за выходом виртуального адреса за пределы выделенного адресного пространства позволил повысить надежность устройства за счет исключения операций доступа к незарегистрированным областям памяти вычислительного узла.

Устройство для преобразования виртуальных адресов в физические адреса, содержащее элемент памяти с таблицей преобразования адресов первого уровня и кэш-память, отличающееся тем, что дополнительно введены многоканальный коммутатор запросов преобразования виртуальных адресов, первые группы входов/выходов которого являются соответствующими группами входов/выходов устройства, и блок управления преобразованием, первая группа входов/выходов которого соединена со второй группой входов/выходов многоканального коммутатора запросов, а вторая группа входов/выходов соединена с группой входов/выходов кэш-памяти, причем третья группа входов/выходов блока управления преобразованием является соответствующей группой входов/выходов устройства, при этом блок управления преобразованием включает в себя управляющий конечный автомат и элемент памяти с таблицей преобразования адресов первого уровня, в которую введены поля размера и смещения, а в каждый канал коммутатора запросов дополнительно введена кэш-память.