Трансляция адресов ввода-вывода в адреса ячеек памяти

Иллюстрации

Показать всеИзобретение относится к области трансляции (преобразованию или переводу) адресов в вычислительной среде. Техническим результатом является повышение эффективности трансляции адресов. Описано преобразование адреса, содержащегося в запросе, выдаваемом адаптером, в адрес, непосредственно применимый при доступе к системной памяти. Адрес содержит множество разрядов, в которое входит первая часть разрядов и вторая часть разрядов. Вторая часть разрядов используется для индексации в таблицах трансляции адресов одного или нескольких уровней с целью осуществления преобразования, а первая часть разрядов не учитывается при преобразовании. Первая часть разрядов используется для проверки достоверности адреса. 2 н. и 10 з.п. ф-лы, 25 ил.

Реферат

Предпосылки создания изобретения

Настоящее изобретение относится в целом к трансляции (преобразованию или переводу) адресов в вычислительной среде, более точно, к трансляции адреса ввода-вывода в адрес ячейки памяти, применимый при доступе к системной памяти среды.

Системная память доступна посредством запросов чтения и записи. Эти запросы могут поступать от различных компонентов вычислительной среды, включая центральные процессоры, а также адаптеры. Каждый запрос содержит адрес, который должен использоваться для доступа к системной памяти. Тем не менее, этот адрес обычно не находится во взаимно однозначном соответствии с физическим местоположением в системной памяти. Соответственно, осуществляется трансляция адреса.

Трансляция адреса используется, чтобы преобразовать адрес, который находится в одной форме, непосредственно неприменимой для доступа к системной памяти, в другую форму, непосредственно применимую для доступа к физическому местоположению в системной памяти. Например, виртуальный адрес, содержащийся в запросе, выдаваемом центральным процессором, транслируется в действительный или абсолютный адрес в системной памяти. В качестве одного из дополнительных примеров, адрес шины межсоединения периферийных компонентов (PCI), содержащийся в запросе от адаптера, может быть транслирован в абсолютный адрес в системной памяти.

В заявке US 2008/0168208 A1 под названием "I/O Adaptet LPAR Isolation In A Hypertransport Environment With Assigned Memory Space Indexing A TVT Via Unit Ids", опубликованной 10 июля 2008 г. (заявитель - Gregg), описана система обработки данных и способ обособления множества адаптеров ввода-вывода в системе. В систему обработки данных также входит набор процессоров, мост между хостами и системная шина, соединяющая набор процессоров и мост между хостами. Каждый из адаптеров ввода-вывода имеет соответствующий идентификатор (ID) и выдает мосту между хостами команды, которые содержат один или несколько из ID адаптеров ввода-вывода. В предпочтительном варианте осуществления этими ID являются определяемые протоколом пересылки гипертекста идентификаторы устройства, а команды, выдаваемые адаптерами ввода-вывода, включают поле ID устройства, в котором содержится один или несколько из ID адаптеров ввода-вывода. Каждый ID устройств используется для индексации TVT с целью идентификации уникальных и независимых пространств системной памяти.

В заявке US 2009/0182966 A1 под названием "Dynamic Address Translation with Frame Management", опубликованной 16 июля 2009 г. (заявитель - Greiner и др.), описана функция управления кадрами, определенная для архитектуры компьютерной системы. В одном из вариантов осуществления принимают команду управления кадрами, в которой определен первый и второй общий регистр. В первом общем регистре содержится поле управления кадрами, имеющее ключевое поле с битами защиты доступа и индикатор размера блока. Если в индикаторе размера блока указан блок большого размера, из второго общего регистра получают адрес операнда блока данных большого размера. Блок данных большого размера содержит множество блоков небольшого размера, каждый из которых связан с соответствующим ключом хранения, содержащим множество битов защиты доступа. Если в индикаторе размера блока указан блок большого размера, в качестве битов защиты доступа для каждого соответствующего ключа хранения каждого блока небольшого размера в блоке большого размера устанавливают биты защиты доступа ключевого поля.

Краткое изложение сущности изобретения

Преодоление недостатков известного уровня техники и достижение дополнительных преимуществ обеспечивается в способ трансляции адресов в вычислительной среде. Предлагаемый в изобретении способ может быть реализован в компьютерном программном продукте, содержащем машиночитаемую среду, которая может считываться устройством обработки данных и в которой хранятся команды для выполнения устройством обработки данных с целью осуществления способа. Способ включает, например, получение от адаптера подлежащего трансляции адреса, содержащего множество разрядов, в которое входит первая часть разрядов и вторая часть разрядов; прием значения диапазона адресов, указывающего диапазон допустимых адресов; проверку достоверности адреса с использованием по меньшей мере первой части разрядов и принятого диапазона адресов; и преобразование адреса в адрес ячейки памяти, применимый при доступе к памяти вычислительной среды, причем в ходе преобразования первая часть разрядов не учитывается, а вторая часть разрядов используется для получения информации об адресе из одного или нескольких уровней таблиц трансляции адресов для осуществления преобразования.

Объектом изобретения является также компьютерная система, содержащая компоненты, необходимые для трансляции адресов в вычислительной среде.

Дополнительные признаки и преимущества настоящего изобретения реализуются за счет предложенной в нем методики. В изобретении подробно описаны другие его варианты осуществления и особенности, считающиеся входящими в заявленное изобретение.

Краткое описание чертежей

Одна или несколько особенностей настоящего изобретения конкретно охарактеризованы и отдельно заявлены в формуле изобретения, следующей за описанием. Перечисленные выше и другие задачи, признаки и преимущества изобретения станут ясны из следующего далее подробного описания в сочетании с сопровождающими его чего чертежами, на которых:

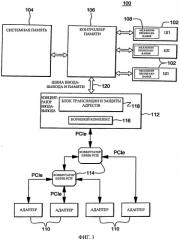

на фиг.1 проиллюстрирован один из вариантов осуществления вычислительной среды, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

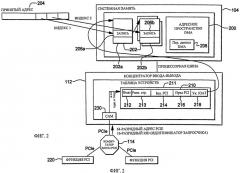

на фиг.2 - один из вариантов осуществления дополнительных подробностей показанных на фиг.1 системной памяти и концентратора ввода-вывода согласно одной из особенностей настоящего изобретения,

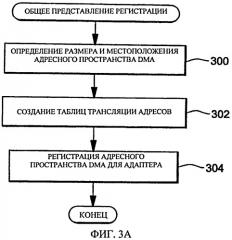

на фиг.3A - один из вариантов осуществления общего представления логики для регистрации адресного пространства прямого доступа к памяти (DMA) для адаптера согласно одной из особенностей настоящего изобретения,

на фиг.3Б - один из вариантов осуществления различных подробностей регистрации адресного пространства DMA для адаптера согласно одной из особенностей настоящего изобретения,

на фиг.4 - один из вариантов осуществления логики для обработки операции DMA согласно одной из особенностей настоящего изобретения,

на фиг.5A - один из примеров уровней трансляции, применяемой, когда при индексации в таблицах трансляции адресов используется весь адрес с целью трансляции адреса и доступа к странице,

на фиг.5Б - один из примеров уровней трансляции, применяемой, когда при индексации в таблицах трансляции адресов не учитывается часть адреса согласно одной из особенностей настоящего изобретения,

на фиг.5В - примеры различных совместимых с динамической трансляцией адреса (DAT) ЦП форматов, применимых согласно одной или нескольким особенностям настоящего изобретения,

на фиг.5Г - примеры различных расширенных форматов трансляции адреса ввода-вывода, применимых согласно одной или нескольким особенностям настоящего изобретения,

на фиг.6A - один из вариантов осуществления команды изменения управления функцией шины PCI (Modify PCI Function Controls), используемой согласно одной из особенностей настоящего изобретения,

на фиг.6Б - один из вариантов осуществления поля, используемого проиллюстрированной на фиг.6A командой изменения управления функцией шины PCI согласно одной из особенностей настоящего изобретения,

на фиг.6В - один из вариантов осуществления другого поля, используемого проиллюстрированной на фиг.6A командой изменения управления функцией шины PCI согласно одной из особенностей настоящего изобретения,

на фиг.6Г - один из вариантов осуществления содержимого блока информации о функциях (function information block (FIB)), используемого согласно одной из особенностей настоящего изобретения,

на фиг.7 - один из вариантов осуществления общего представления логики команды изменения управления функцией шины PCI согласно одной из особенностей настоящего изобретения,

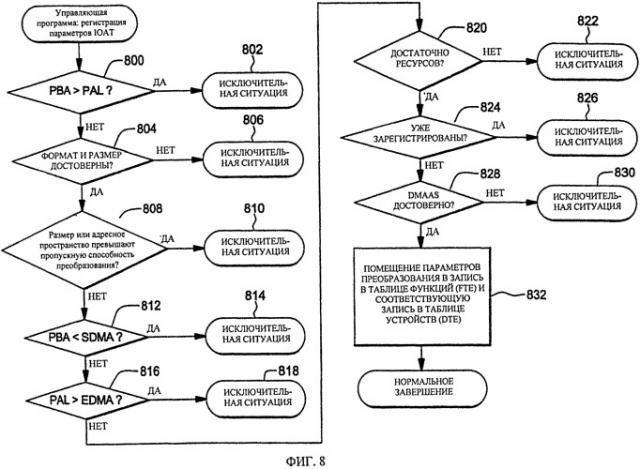

на фиг.8 - один из вариантов осуществления логики, связанной с операцией регистрации параметров трансляции адресов ввода-вывода, которая может быть определена командой изменения управления функцией шины PCI, согласно одной из особенностей настоящего изобретения,

на фиг.9 - один из вариантов осуществления логики, связанной с операцией отмены регистрации параметров трансляции адресов ввода-вывода, которая может быть определена командой изменения управления функцией шины PCI, согласно одной из особенностей настоящего изобретения,

на фиг.10 - один из вариантов осуществления компьютерного программного продукта, в котором содержится одна или несколько особенностей настоящего изобретения,

на фиг.11 - один из вариантов осуществления хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг.12 - один из дополнительных примеров компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг.13 - другой пример компьютерной системы, представляющей собой компьютерную сеть, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг.14 - один из вариантов осуществления различных элементов компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг.15A - один из вариантов осуществления блока выполнения проиллюстрированной на фиг.14 компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг.15Б - один из вариантов осуществления блока перехода проиллюстрированной на фиг.14 компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг.15В - один из вариантов осуществления блока загрузки/сохранения проиллюстрированной на фиг.14 компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения, и

на фиг.16 - один из вариантов осуществления эмулируемой хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

Подробное описание

Согласно одной из особенностей настоящего изобретения предложено средство трансляции адресов в вычислительной среде. В одном из примеров транслируемыми адресами являются адреса, предоставленные адаптером (называемые в описании адресами ввода-вывода), которые должны быть переведены в адреса, применимые для доступа к системной памяти. Для осуществления трансляции адреса используется несколько уровней трансляции адреса, исходя, например, из размера адресного пространства памяти, присвоенного адаптеру, размера одной или нескольких таблиц трансляции адресов, используемых при трансляции, и/или размера страницы (или другого блока памяти), доступ к которой должен осуществляться.

Транслируемый адрес содержит множество разрядов, и в одном из вариантов осуществления при индексации в таблицах трансляции адресов используется лишь часть этих разрядов с целью получения транслированного адреса. Остальные разряды для трансляции не учитываются. Например, адрес содержит старшие разряды и младшие разряды (в зависимости от размера присвоенного адресного пространства). В этом примере младшие разряды используются для индексации в таблицах трансляции адресов, включая таблицу страниц, и для индексации на самой странице. Старшие разряды (независимо от значения, т.е. нулевые или ненулевые) не учитываются для трансляции и не используются для индексации в таблицах трансляции адресов. За счет этого уменьшается число уровней таблиц трансляции адресов, используемых для трансляции (обозначение младших и старших разрядов не зависит от того, как пронумерованы разряды).

В одном из примеров трансляция осуществляется наряду с обеспечением защиты, применимой для сервера корпоративного класса, такого как сервер System z®. В качестве примера, для доступа к памяти используется полный адрес (например, полный 64-разрядный адрес); однако для трансляции используется только часть адреса. Другая часть адреса, которая для трансляции не учитывается, используется для проверки достоверности (например, проверки попадания в диапазон) наряду по меньшей мере с частью адреса, используемой для трансляции. За счет использования для трансляции только части адреса сводятся к минимуму обращения к таблицам трансляции адресов. Это достигается путем осуществления трансляции нескольких уровней, исходя, например, из размера адресного пространства DMA, зарегистрированного для доступа со стороны адаптера, а не размера самого адреса.

Далее со ссылкой на фиг.1 будет описан один из вариантов осуществления вычислительной среды, в которой содержится и используется одна или несколько особенностей настоящего изобретения. В одном из примеров вычислительной средой 100 является сервер System z®, предлагаемый International Business Machines Corporation. Основой сервера System z® является z/Architecture®, предлагаемая International Business Machines Corporation. Подробности, касающиеся z/Architecture®, описаны в публикации IBM №SA22-7832-07 под названием "z/Architecture-Principles of Operation" (февраль 2009 г.). IBM®, System z® и z/Architecture® являются зарегистрированными товарными знаками International Business Machines Corporation (Армонк, штат Нью-Йорк, США). Другие названия, используемые в заявке, могут являться зарегистрированными товарными знаками, товарными знаками или названиями продуктов International Business Machines Corporation или других компаний.

В одном из примеров вычислительная среда 100 содержит один или несколько центральных процессоров (ЦП) 102, связанных с системной памятью 104 (иначе называемой основной памятью) посредством контроллера 106 памяти. Для доступа к системной памяти 104 центральный процессор 102 выдает запрос чтения или записи, в котором содержится адрес, используемый для доступа к системной памяти. Поскольку адрес, содержащийся в запросе, обычно не может непосредственно использоваться для доступа к системной памяти, он транслируется в адрес, который может непосредственно использоваться для доступа к системной памяти. Адрес транслируется посредством механизма 108 трансляции (XLATE). Например, адрес транслируется из виртуального адреса в действительный или абсолютный адрес с использованием, например, динамической трансляции адресов (DAT).

Запрос, содержащий транслированный адрес, принимается контроллером 106 памяти. В одном из примеров контроллер 106 памяти состоит из аппаратного обеспечения и используется для арбитража при доступе к системной памяти и для обеспечения непротиворечивости памяти. Этот арбитраж осуществляется применительно к запросам, принимаемым от ЦП 102, а также запросам, принимаемым от одного или нескольких адаптеров 110. Подобно центральным процессорам адаптеры выдают в системную память 104 запросы на получение доступа к системной памяти.

В одном из примеров адаптером 110 является адаптер шины межсоединения периферийных компонентов (PCI) или адаптер на основе шины PCI Express (PCIe), содержащей одну или несколько функций шины PCI. Функция шины PCI выдает запрос на доступ к системной памяти. Запрос маршрутизируется в концентратор 112 ввода-вывода (например, концентратор шины PCI) посредством одного или нескольких коммутаторов (например, коммутаторов шины PCIe) 114. В одном из примеров концентратор ввода-вывода состоит из аппаратного обеспечения, включающего один или несколько конечных автоматов.

Используемый в описании термин адаптер означает адаптер любого типа (например, адаптер памяти, сетевой адаптер, адаптер обработки, адаптер на основе шины PCI, криптографический адаптер, адаптеры ввода-вывода другого типа и т.д.). В одном из вариантов осуществления адаптер содержит одну функцию. Тем не менее, в других вариантах осуществления адаптер может содержать множество функций. В зависимости от того, содержит ли адаптер одну функцию или множество функций, применима одна или несколько особенностей настоящего изобретения. Кроме того, в представленных примерах термин адаптер используется взаимозаменяемо с термином функция адаптера (например, функция шины PCI), если не указано иное.

Концентратор ввода-вывода содержит, например, корневой комплекс 116, который принимает запрос от коммутатора. Поскольку в запросе содержится адрес ввода-вывода, подлежащий трансляции, корневой комплекс предоставляет адрес блоку 118 трансляции и защиты адресов. Этим блоком является, например, аппаратный блок, который транслирует адрес ввода-вывода в адрес, непосредственно применимый при доступе к системной памяти 104, как более подробно описано далее.

Инициированный адаптером запрос, содержащий транслированный адрес, предоставляется контроллеру 106 памяти посредством, например, шины 120 ввода-вывода и памяти. Контроллер памяти осуществляет арбитраж и в соответствующее время пересылает системной памяти запрос с транслированным адресом.

Дополнительные подробности, касающиеся системной памяти и концентратора ввода-вывода, описаны со ссылкой на фиг.2. В этом варианте осуществления контроллер памяти не показан. Тем не менее, концентратор ввода-вывода может быть связан с системной памятью напрямую или посредством контроллера памяти. В одном из примеров системная память 104 содержит одно или несколько адресных пространств 200. Адресным пространством является конкретная часть системной памяти, которая присвоена конкретному компоненту вычислительной среды, такому как конкретный адаптер. В одном из примеров адресное пространство доступно путем прямого доступа к памяти (DMA), инициированного адаптером, и, соответственно, в рассматриваемых примерах адресное пространство называется адресным пространством DMA. Тем не менее, в других примерах для доступа к адресному пространству не используется прямой доступ к памяти.

Кроме того, в одном из примеров системная память 104 содержит таблицы 202 трансляции адресов, используемые для трансляции адреса, непосредственно неприменимого для доступа к системной памяти, в непосредственно применимый адрес. В одном из вариантов осуществления адресному пространству DMA присвоена одна или несколько таблиц трансляции адресов, которые сконфигурированы, исходя, например, из размера адресного пространства, которому они присвоены, размера самих таблиц трансляции адресов и/или размера страницы (или другого блока памяти).

В одном из примеров предусмотрена определенная иерархия таблиц трансляции адресов. Например, как показано на фиг.2, предусмотрена таблица 202а первого уровня (например, таблица сегментов), на которую указывает указатель 218 IOAT (описанный далее), и таблица 202b второго, более низкого уровня (например, таблица страниц), на которую указывает запись 206а в таблице первого уровня. Один или несколько разрядов принятого адреса 204 используются для индексации в таблице 202a с целью определения местонахождения конкретной записи 206a, которая указывает на конкретную таблицу 202b низкого уровня. Затем один или несколько других разрядов адреса 204 используются для определения местонахождения конкретной записи 206b в этой таблице. В данном примере эта запись обеспечивает адрес, используемый для определения местонахождения правильной страницы, а дополнительные разряды в адресе 204 используются для определения конкретного местонахождения 208 на странице для осуществления передачи данных. Иными словами, адрес, содержащийся в записи 206b, и выбранные разряды принятого адреса 204 PCI используются для обеспечения адреса, непосредственно применимого для доступа к системной памяти. Например, непосредственно применимый адрес формируется путем конкатенации старших разрядов адреса в записи 206b (например, разрядов 63:12 на 4-килобайтовой странице) и выбранных младших разрядов из принятого адреса шины PCI (например, разрядов 11:0 на 4-килобайтовой странице).

В одном из примеров за присвоение адресного пространства DMA конкретному адаптеру отвечает операционная система. Это присвоение осуществляется посредством процесса регистрации, который приводит к инициализации (например, посредством выверенного программного обеспечения) записи 210 в таблице устройств для этого адаптера. Запись содержится в таблице 211 устройств, находящейся в концентраторе 112 ввода-вывода. Например, таблица 211 устройств находится в блоке трансляции адресов и защиты концентратора ввода-вывода.

В одном из примеров запись 210 в таблице устройств содержит несколько полей, таких как следующие поля:

поле 212 формата: в этом поле содержится множество разрядов для обозначения различной информации, включая, например, формат трансляции адреса (включая уровень) таблицы верхнего уровня из таблиц трансляции адресов (например, таблицы первого уровня в приведенном выше примере);

поле 213 размера страницы: в этом поле указан размер страницы (или другого блока памяти) для доступа;

поле 214 базового адреса шины PCI и поле 216 предела адреса шины PCI: эти значения обеспечивают диапазон, используемый для определения адресного пространства DMA и проверки достоверности принятого адреса (например, адреса шины PCI), и

поле 218 указателя IOAT (трансляции адреса ввода-вывода): в этом поле содержится указатель таблицы трансляции адресов наивысшего уровня, используемой для адресного пространства DMA.

В других вариантах осуществления в DTE может содержаться больше, меньше информации или другая информация.

В одном из вариантов осуществления местоположение записи в таблице устройств для использования при конкретной трансляции определяют с использованием идентификатора запросчика (RID), содержащегося в запросе, выдаваемом функцией 220 шины PCI, соответствующей адаптеру (и/или частью адреса). В запросе содержится идентификатор запросчика (например, 16-разрядное значение, указывающее, например, номер шины, номер устройства и номер функции), а также адрес ввода-вывода (например, 64-разрядный адрес шины PCIe) для использования с целью доступа к системной памяти. Запрос, содержащий RID и адрес ввода-вывода, выдается, например, посредством, коммутатора 114, например, ассоциативной памяти (САМ) 230, которая используется для получения заданного значения. Например, в САМ содержится множество записей, каждая из которых соответствует индексу в таблице устройств. Каждая запись в САМ содержит значение RID. Если, например, принятый RID соответствует значению, содержащемуся в записи в САМ, для определения местоположения записи в таблице устройств используется соответствующий индекс из таблицы устройств. Иными словами, выводимые из CAM данные используются для индексации в таблице 211 устройств с целью определения местоположения записи 210 в таблице устройств. Если соответствие отсутствует, принятый пакет отбрасывается и доступ к системной памяти не осуществляется (в других вариантах осуществления не требуется CAM или другое средство поиска и RID используется в качестве индекса).

Затем поля в записи в таблице устройств используются, чтобы гарантировать достоверность адреса и конфигурацию таблиц трансляции адресов. Например, аппаратное обеспечение концентратора ввода-вывода (например, блок трансляции и защиты адреса) проверяет входящий адрес в запросе, чтобы гарантировать, что он находится в границах, установленных базовым адресом 214 шины PCI и пределом 216 адреса шины PCI, которые хранятся в записи в таблице устройств, обнаруженной с использованием RID запроса, в котором содержался адрес. Тем самым гарантируется, что адрес находится в диапазоне, который был ранее зарегистрирован и для которого достоверно сконфигурированы таблицы трансляции адресов.

Согласно одной из особенностей настоящего изобретения для трансляции адреса ввода-вывода (т.е. адреса, предоставленного адаптером или другим компонентом подсистемы ввода-вывода) в системный адрес ячейки памяти (т.е. адрес, непосредственно применимый при доступе к системной памяти) в одном из вариантов осуществления сначала осуществляется процесс регистрации. В ходе этого процесса регистрации с помощью конкретного запросчика, такого как конкретный адаптер или функция адаптера, регистрируется конкретное адресное пространство. Один из примеров общего представления этого процесса регистрации описан со ссылкой на фиг.3A.

Сначала на шаге 300 операционная система, выполняемая в одном из центральных процессоров, связанных с системной памятью, определяет размер и местоположение адресного пространства, доступ к которому должен осуществить адаптер. В одном из примеров размер адресного пространства определяется на основании базового адреса шины PCI и предела шины PCI, установленных операционной системой. Операционная система определяет базовый адрес и предел с использованием одного или нескольких критериев. Например, если операционная система желает, чтобы адреса шины PCI непосредственно соответствовали виртуальным адресам ЦП, устанавливается базовый адрес и предел как таковые. В одном из дополнительных примеров, если желательно дополнительное разобщение адаптеров и/или образов операционной системы, выбираются используемые адреса, обеспечивающие неперекрывающиеся и раздельные адресные пространства. Местоположение также определяется операционной системой на основании, например, характеристик адаптера.

После этого на шаге 302 создается одна или несколько таблиц трансляции адресов, охватывающих адресное пространство DMA. Например, таблицы могут являться совместимыми с таблицами трансляции адресов ЦП, или может быть предусмотрен уникальный формат, поддерживаемый концентратором ввода-вывода. В одном из примеров создание таблиц включает построение таблиц и помещение соответствующих адресов в записи в таблице. В качестве примера, одной из таблиц трансляции является 4-килобайтовая таблица страниц, содержащая 512 64-разрядных записей, каждая из которых содержит 4-килобайтовый адрес страницы, совместимый с присвоенным адресным пространством.

После этого на шаге 304 регистрируется адресное пространство DMA для адаптера, как подробнее описано со ссылкой на фиг.3Б. Поскольку в этом примере считается, что каждому адаптеру соответствует одна функция шины PCI, каждому адаптеру соответствует один идентификатор запросчика. Логика выполняется, например, центральным процессором, связанным с системной памятью, в ответ на запрос операционной системы.

В одном из вариантов осуществления сначала на шаге 310 выбирается доступная запись в таблице устройств, которая соответствует идентификатору запросчика адаптера. Иными словами, идентификатор запросчика используется для определения местонахождения записи в таблице устройств.

Кроме того, на шаге 312 в записи в таблице устройств сохраняется базовый адрес шины PCI и предел шины PCI. Далее на шаге 314 в записи в таблице устройств также сохраняется формат таблицы трансляции адресов высшего уровня (например, поле формата), а также указатель трансляции адреса ввода-вывода (IOAT), используемый для указания таблицы трансляции адресов высшего уровня. На этом процесс регистрации завершается.

После осуществления регистрации адресное пространство DMA и соответствующие таблицы трансляции адресов, а также запись в таблице устройств готовы к использованию. Подробности обработки запроса, выдаваемого запросчиком, например, с целью получения доступа к системной памяти, описаны со ссылкой на фиг.4. Описанная далее обработка осуществляется концентратором ввода-вывода. В одном из примеров за выполнение логики отвечает блок трансляции и защиты адреса.

В одном из вариантов осуществления сначала на шаге 400 концентратор ввода-вывода принимает запрос DMA. Например, функция шины PCI выдает запрос, который пересылается концентратору шины PCI посредством, например, коммутатора шины PCI. На шаге 402 определяется местоположение соответствующей записи в таблице устройств с использованием идентификатора запросчика, содержащегося в запросе. После этого на шаге 404 проверяется, достоверна ли запись в таблице устройств. В одном из примеров достоверность проверяется путем проверки разряда достоверности в самой записи. Этот разряд устанавливается, например, в результате выполнения операционной системой запроса разрешения функции. Если функция разрешена, значение разряда приравнивается, например, к единице (т.е. он является достоверным); в противном случае его значение остается нулевым (т.е. недостоверным). В одном из дополнительных примеров значение разряда может быть установлено после завершения процесса регистрации.

Если запись в таблице устройств является недостоверной, на шаге 405 отображается ошибка. В противном случае на шаге 406 дополнительно определяется, имеет ли адрес шины PCI, содержащийся в запросе, меньшую длину, чем базовый адрес шины PCI, хранящийся в записи в таблице устройств. Если это так, адрес находится вне достоверного диапазона и на шаге 407 сообщается об ошибке. Тем не менее, если длина адреса шины PCI больше или равна длине базового адреса, на шаге 408 дополнительно определяется, не превышает ли длина адреса шины PCI предельное значение шины PCI в записи в таблице устройств. Если длина адреса шины PCI превышает предельное значение, на шаге 409 снова отображается ошибка, поскольку адрес находится вне достоверного диапазона. Тем не менее, если адрес находится в пределах достоверного диапазона, обработка продолжается.

В одном из примеров формат, содержащийся в записи в таблице устройств, используется на шаге 410 для определения разрядов адреса шины PCI в адресе для использования с целью трансляции адреса. Например, если в формате указано, что таблице верхнего уровня является таблица первого уровня, содержащая 4-килобайтовые страницы, для индексации в таблице первого уровня используются разряды 29:21 адреса; для индексации в таблице страниц используются разряды 20:12; а для индексации на 4-килобайтовой странице используются разряды 11:0. Используемые разряды зависят от того, сколько разрядов необходимо для индексации на странице или в таблице заданного размера. Например, в случае 4-килобайтовой страницы с байтовой адресацией для адресации 4096 байтов используется 12 разрядов; а в случае 4-килобайтовой таблицы страниц с 512 записями по 8 байтов каждая для адресации 512 записей используется 9 разрядов и т.д.

Затем на шаге 412 концентратор шины PCI осуществляет выборку соответствующей записи из таблицы трансляции адресов. Например, сначала с использованием указателя IOАТ записи в таблице устройств определяется местоположение таблицы трансляции наивысшего уровня. Затем разряды адреса (следующие за старшими разрядами, используемыми для проверки достоверности, а не для трансляции; например, разрядами 29:21 в приведенном выше примере) используются для определения местоположения конкретной записи в этой таблице.

Далее на основании, например, формата, содержащегося в записи в таблице устройств, на шаге 414 запроса определяется, имеет ли обнаруженная запись трансляции адреса правильный формат. Например, формат в записи в таблице устройств сравнивается с форматом, указанным в записи трансляции адреса. Если они совпадают, формат в записи в таблице устройств является достоверным. Если нет, на шаге 415 сообщается об ошибке; в противном случае обработка продолжается и на шаге 416 запроса определяется, является эта таблица последней для обработки. Иными словами, определяется, существуют ли другие таблицы трансляции адресов, необходимые для получения действительного или абсолютного адреса, или была ли обнаружена запись в таблице низшего уровня. Это определяется на основании известного формата и размера уже обработанных таблиц. Если таблица не является последней, обработка продолжается на шаге 412. В противном случае концентратор ввода-вывода продолжает обработку на шаге 418, чтобы обеспечить выборку или сохранение данных с использованием транслированного адреса. В одном из примеров концентратор ввода-вывода пересылает транслированный адрес контроллеру памяти, который использует его для выборки или сохранения данных в местоположении DMA, указанном в транслированном адресе.

Как описано выше, согласно одной из особенностей настоящего изобретения уменьшается число уровней трансляции и, соответственно, число выборок, необходимых для осуществления трансляции. Это достигается, например, за счет того, что во время трансляции не учитываются старшие разряды адреса, и для прохождения таблиц трансляции используются только младшие разряды, основанные, например, на размере адресного пространства DMA, присвоенного адаптеру. Использование части адреса, а не полного адреса дополнительно рассмотрено в следующих далее примерах.

На фиг.5A проиллюстрирован один из примеров, в котором при трансляции адреса/доступе к памяти используется полный адрес. Согласно этому известному подходу требуются таблицы трансляции шести уровней, включая таблицу страниц. Указатель IOAT указывает начало таблицы высшего уровня (например, таблицы уровня 5 в этом примере), а затем для определения местонахождения записи в таблице используются разряды адреса шины PCI. Каждая запись в таблице трансляции указывает начало таблицы трансляции более низкого уровня или страницу (например, запись в таблице уровня 5 указывает начало таблицы уровня 4 и т.д.)

В этом примере размер адресного пространства DMA (DMAAS) составляет 6 мегабайт, а каждая таблица имеет размер 4 килобайта и содержит максимально 512 8-байтовых записей (за исключением таблицы уровня 5, которая содержит 128 записей с учетом размера адреса). Адрес содержит, например, 64 разряда: FFFF С000 0009 С600. Указатель IOAT указывает начало таблицы уровня 5, а разряды 63:57 адреса шины PCI используются для индексации в таблице уровня 5 с целью определения местоположения начала таблицы уровня 4; разряды 56:48 адреса шины PCI используются для индексации в таблице уровня 4 с целью определения местоположения начала таблицы уровня 3; разряды 47:39 используются для индексации в таблице уровня 3 с целью определения местоположения начала таблицы уровня 2; разряды 38:30 используются для индексации в таблице уровня 2 с целью определения местоположения начала таблицы уровня 1; разряды 29:21 используются для индексации в таблице уровня 1 с целью определения местоположения начала таблицы страниц; разряды 20:12 используются для индексации в таблице страниц с целью определения местоположения начала страницы; и разряды 11:0 используются с целью определения местоположения записи на 4-килобайтовой странице. Таким образом, в этом примере при трансляции/доступе используются все разряды адреса.

В отличие от этого в примере, проиллюстрированном на фиг.5Б, адресное пространство имеет такой же размер (например, 6 мегабайт), а адрес имеет такую же длину, но для трансляции не учитываются некоторые разряды адреса. В этом примере для трансляции не учитываются разряды 63:30 адреса. Указатель IOАТ указывает начало таблицы уровня 1, а разряды 29:21 адреса шины PCI используются для индексации в таблице уровня 1 с целью определения местоположения начала таблицы страниц; разряды 20:12 используются для индексации в соответствующей таблице страниц с целью определения местоположения начала страницы; и разряды 11:0 используются для индексации на 4-килобайтовой странице.

Как показано, таблица 500 уровня 1 содержит три записи 502, в каждой из которых указан адрес одной из трех таблиц 504 страниц. Необходимое число таблиц страниц и, соответственно, число таблиц других уровней зависит, например, от размера адресного пространства DMA, размера таблиц трансляции и/или размера страниц. В этом примере адресное пространство DMA составляет 6 мегабайт, а каждая таблица страниц имеет размер 4 килобайта и содержит до 512 записей. Соответственно, каждая таблица страниц способна отображать до 2 мегабайт памяти (4 килобайта × 512 записей). Таким образом, для отображения 6-мегабайтного адресного пространства требуются три таблицы страниц. В таблице уровня 1 может содержаться три записи, по одной для каждой таблицы страниц, и, соответственно, в этом примере не требуются таблицы трансляции адресов дополнительных уровней.

В одном из дополнительных вариантов осуществления для трансляции адреса могут использоваться таблицы трансляции адресов отличающихся форматов, и могут быть пр