Устройство для ускоренного деления чисел с аппаратным контролем

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

25489I

Со!оз Соеетских

Социалистических

Ресоублик

Зависимое от авт. свидетельства №

Кл. 42m:I, 7/52

Заявлено 16Л!111.1968 (№ 1264576 18-24) с присоединением заявки ¹.ЧПК G ОИ

Приоритет

Опубликовано 17.Х.1969. Бюллетень ¹ 32

Комитет оо делам изобретений и открытий ори Совете Министров

СССР

УДI(681.325.587 (088.8) Дата опубликования описания 9.111.1970 — !

Ав гор изобпетения

В. И. Жук

Филиал № 1 Объединенного конструкторского бюро «Вым !ел»

1,—.- =--- -—

Заявитель

УСТРОЙСТВО ДЛЯ УСКОРЕННОГО ДЕЛЕНИЯ ЧИСЕЛ

С АППАРАТНЫМ КОНТРОЛЕМ

Предлагаемое устройство относится к цифровым устройствам для ускоренного деления чисел, с нахождением на каждом этапе деления з!начений нескольких разрядов частного и с аппаратным контролем деления по мо- 5 дулю.

Известны цифровые устройства для ускоре.iного деления двоичных чисел с нахождени и одновременно значений нескольких разрядов частного и с аппаратным контролем деления 10 по модулю, содержащие регистры делимого, делителя и частного, устройство для нахождения цифр частного, устройство для преобразования частного, устройство для контроля деления по модулю, устройство местного уп- 15 равления и устройство для вычисления остатков. В известных устройствах аппаратный контроль по модулю не обнаруживает в частном и в остатке большого количества ошибок, возникающих в устройстве для нахождения 20 значений очередных цифр промежуточного частного.

Целью предлагаемого устройства является обнаружение ошибок, возникающих вследствие сбоев или неисправностей в аппаратуре 25 для нахождения цифр частного.

Предлагаемое устройство отличается тем, то содержит устройство для сравнения послед!него остатка с предельно допустимыми значениями остатка при данном делителе и 30 выработки сигнала ошибки II дешифраторы несовпадения, входы которых соединены с выходам:1 старших разрядов устройства для

Bb1÷èñëñíèÿ остатков, одни из входов устройства для сравнения соедннены с выходами устройства для вычисления остатков, предназначе:!ными для выдачи последнего остатка, а другие входы соединены с выходами регистра делителя.

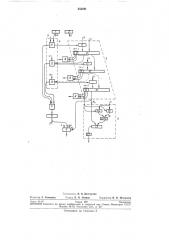

На чергеже показан один из вар!!антов реализации описываемого устройства.

В состав устройства входят регистр 1 делимого ..г, регистр 2 делителя у, устройство для вычисления остатков, устройство 4 для нахождения очередных цифр частного, устройство 5 дчя преобразования частного, регистр

6 частного z, устройство 7 контроля iio модулю, дешифраторы 8 несовпадения между собой такого количества старших разрядов в каждом о 1ередном частичном о;.татке, включая разряд его знака, которое на е г!1шщу больше количества разрядов частного, определяемых одновременно. Устройство 9

c, I ó æ I I T дг1 я с р а в н е и 11 !1 i I o c,1 Ðä! 1 Ã Ã Î остатка с величинами, равными допустимым предельным значениям остатка прп данном делителе, и для формирования по результатам этого сравнения сигнала ошибки в случае выхода величины последнего остатка R» из допустимого диапазона.

254891

Устройство 8 для вычисления остатков R g содержит несколько линеек iver apaëëåëüíûõ сумматоров 10 с входными коммутаторами 11 для ввода кратных делителя у в каждую линейку сумматоров 10.

Устройство 4 для нахождения очередных цифр частного содержит несколько декоднрующих узлов 12 (по одному узлу на каждую линейку сумматоров 10).

Количество дешифраторов 8 соответствует количесгву декодирующих узлов 12 в устройстве 4 и, следовательно, количеству линеек сумматоров в устройстве 8. Каждый дешифратор представляет собой по существу дешифратор несоответствия на (m+1) разрядов, где и — -количество разрядов частного, значения когорых находятся одновременно на одном этапе деления.

Устройство 9 содержит устройство сравнения 18, выполненное в виде сумматора с входными клапанами 14 и 15, сборку ИЛИ 15 и формирователь 17 сигнала ошибки по результатам сравнения в случае выхода величины последнего остатка Rn из допустимого диапазона.

Устройство производит деление за несколько этапов, на каждом из которых определяются одновременно значения двух или более разрядов частного. За один цикл (такт) управления могут быть осуществлены один или несколько этапов деления, а в пределе — все этапы. В последнем случае устройство 8 содержит количество линеек параллельных сумматоров, равное количеству этапов (при этом устройсгво 4 содержит столько же декодирующих узлов и имеется столько ?ке дешифраторов 8).

B первом случае устройство 8 может содер?KBTb .один (два) параллельный сумматор, а устройство 4 один декодирующий узел (при этом имеется всего один дешифратор 8).

Делимое х поступает в регистр 1, нормализованный делитель у — в регистр 2. На каждом этапе при,помощи устройства 4 анализируются значения старших разрядов делителя и предыдущего остатка и в результате этого анализа выбирается очередная цифра,промежуточн зго частного, соответствующая двум или более разрядам окончательного частного.

Затем на каждом этапе устройство 8 вычисляет очередной остаток по формуле

Rs+ > = 2mR () а,.„у .р .. (4) 2гп — 1

amax amln

2m (5) то

R — m пр max — 1 пр min (6) 50

Неравенства (3) и (7) проверяются сравнением 2 — "у и R, Например: (8) () где

a(py

Если неравенства (3) и (7) нарушаются, то выполняются условия (8) или (9), и уст60 ройство 9 формирует сигнал о наличии ошибки.

На каждом этапе при помощи дешифратора 8 производится контроль условия (10), если отрицательные остатки представлены в

65 дополнительном коде, или условия (11), если

Ri+1

R, т — номер этапа деления (i =0, 1, 2,..., Й вЂ” 1); — цифра промежуточного частного, выбранная на (+1) -м этапе из набора аь ..., an (при h)2— набор является избыточным); — остаток, вычисляемый на (i-,-1) -м этапе; — остаток, полученный на i-м этапе; — количество разрядов частного, значение которых одновременно определяется на одном этапе;

2 — основание системы счисления, в которой представлено промежуточное частное.

Прн i=-0 R,=2 — "х.

Устройс1во 4 вырабатывает сигналы, соответствующие очередной цифре а +1 и управляющие устройством 8. Очередная цифра а;+ из устройства 4 поступает в устройство 5, где происходит преобразование цифр промежуточного частного с учетом весов разрядов промежуточного частного. В результате такого преобразования на выходе устройства

5 формируется окончательное частное z, поступающее в .регистр б:

z=a,+а, 2 " +,...,+а,,л 2 +,...,+

+а„2 ", (2) где /г — количество этапов.

Устройство 7 ведет контроль деления по модулю на каждом этапе или на последнем этапе.

По окончании деления производится контроль условия (2) при помощи устройства 9:

R» m,„ < R,:-= Л„ (3) где R — последний остаток (остаток, полученный на последнем этапе), 50 Бпр щщRпр (П1у минимальная и максимальная предельные величины остатка при данном делителе у, на пракгике выбирают

З5 min У

2т 1

Если и условие (4) принимает следующий вид: — 2 " у (R (2 "у (7) 2 — " у — R (O, если R,) О, 2 "у+R (О, если R,(О.

25489i отрицательные остатки представлены в обратном коде:

R,. 2 "+ (%+1(.R.„., Rm,n (Rl, l (Л.„, (10) (11) где R,„è RI„— максимально и минимально возможные величины остатков при максимальном делителе, у,„= 2 — " у „(12) а„„„

RmIn Ушак — 2 У пах (13) г — 1

g,,„„„„— —максимально возможная величина делителя, у „=1 — 2 —" (14) п — количество двоичных разрядов в делителе.

С учетом (12) и (13) условия (10) и (11) могут быть представлены соответственно в виде условий (15) и (16): — 2 — у, — 2 — <+"1 (R<+I (2 — "у„,,„(15) — 2- g (а„(2 ó,„„, (16) RÄ...„(а„(R„,.„„ (18)

Если нарушается условие (17), то значения старших разрядов очередного остатка W I+I, начиная с первого знакового разряда и кончая (т+1)-м разрядом, не совпадают между собой (т. е., количество старших разрядов, начиная с разряда знака, значения которых не одинаковы, равно т+1). В этом случае дешифратор 8 вырабатывает сигнал о наличии ошибки.

Если принять, что (19) H Ry=<, то

Rmax RmIn Y nax — 1 (Ж < (1 — 2 —" (20) (21) Подставив (14) в (15) и (16), получим — 2- (а+, (2 -2-«-- > (17)

При,нарушении условия (17) всегда нарушается - условие (18), аналогичное условию (13):

В этом случае вычисление остатка по формуле (1) ведется при m)2 по модулю 2 " .

Поэтому формирование сигнала ошибки при нарушении неравенства (21) производится так же, как при нарушении неравенства (17). HpII необходи IOcTII использовать одинаковые кратные делителя и множимого и находится по формуле (5). При m)2, как правило, пользуются формулой (5), которая по сравнению с формулой (19) дает большие удобства,при совмещении аппаратуры для деления с аппаратурой для умножения.

Можно показать, что если на некотором этапе деления нарушено условие (18) и не нарушено условие (17). то на последующих этапах деления может произойти нарушение условия (17) пли условия (18), условие (3) оказывается нарушенным на последнем этапе деления.

Таким образом, все ошибки в выборе цифры час гного, искажающие результирующее значение частного, приводят к нарушению условий (17) пли (3); а любое нарушение условий (17) и (3) обнаруживается описанным выше образом.

Предмет изобретения

Устройство для ускоренного деления чисел

30 с аппаратным контролем и нахождением одновременно нескольких разрядов частного, содержащее регистры делимого, делителя и частного, устройство для нахождения цифр частного, устройство для преобразования

55 частного, устройство для вычисления остатков, устройство для контроля деления по модулю, устройство местного управления, от.шчающееея тем, что, с целью обнаружения ошибок в устройстве для нахождения цифр

40 частного, оно содержит устройство для сравнения последнего остатка с предельно допустимыми значениями остатка при данном делителе н выработки сигнала ошибки и дешифраторы несовпадения, входы которых сое45 динены с выходами старших разрядов устройства для вычисления остатков, одни из входов устройства для сравнения соединены с выходами устройства для вычисления остатков, предназначенными для выдачи послед50 него остатка, а другие входы "îåäèíåíû с выходами регистра делителя.

Редактор Е. Семанова

Составитель И. В. Долгушева

Тсхред Л. Я. Левина Корректор В. И. Жолудева

Заказ 414/7 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва К-35, Раугпская наб., д. 4/5

Типография, пр. Сапунова, 2