Формирователь матричных команд

Иллюстрации

Показать всеИзобретение относится к области электронной техники и автоматики и может найти применение в различных системах управления для формирования импульсных команд управления исполнительными элементами командной матрицы. Технический результат заключается в повышении надежности путем исключения условий ложного срабатывания исполнительных элементов командной матрицы при возникновении неисправности в формирователе матричных команд, а также путем исключения условий формирования в любой момент более одной команды при поступлении новых данных на информационные входы формирователя матричных команд. Технический результат достигается за счет того, что формирователь матричных команд содержит шины приема данных 1 и 2 столбцов и строк, вход записи данных 3, регистры 4 и 5 строк, первые дешифраторы 6 и 7 столбцов и строк, группы ключей 8 и 9 коммутации столбцов и строк, матричные шины 10 и 11 столбцов и строк, шины питания +Е и -Е. 1 з.п. ф-лы, 2 ил.

Реферат

Изобретение относится к области электронной техники и автоматики и может найти применение в различных системах управления, в частности в системах управления космических аппаратов, в роботах, роботизированных линиях и т.п.

Известно устройство коммутации с адресным управлением, содержащее дешифратор, поляризованные реле с двумя группами переключающих контактов, коммутационную матрицу, состоящую из столбцов и строк, в узлах которых установлены реле с развязывающими диодами. Контакты реле являются выходами матричных команд (см. а.с. СССР №1274021, кл. Н03К 17/04).

Недостатками указанного устройства является низкое быстродействие, так как установка требуемого положения коммутатора производится в два этапа, а также отсутствие контроля неисправности коммутационной матрицы.

Известно устройство многоканального командного аппарата с электронной коммутацией, предназначенное для формирования импульсных команд управления на блок исполнительных органов, содержащее соединенные последовательно контроллер интерфейсов, блок дешифраторов, блок формирователей команд и блок ключей, выходы которых являются выходами устройства (см. патент РФ №2340925, кл. G05B 11/00).

В качестве блока исполнительных органов для такого устройства может служить командная матрица, входы которой образуют матричные шины столбцов и строк, в узлах которых установлена нагрузка с развязывающими диодами.

Недостатком устройства является возможность формирования в матричных шинах столбцов и строк сразу нескольких команд, что может привести к ложному срабатыванию нагрузок в узлах командной матрицы, которые при формировании одиночных команд не используются.

Наиболее близким к заявляемому устройству по технической сущности и достигаемому техническому результату является формирователь матричных команд, содержащий шины приема данных столбцов и строк (информационные входы устройства), вход записи данных, регистры столбцов и строк, дешифраторы столбцов и строк, группы ключей коммутации столбцов и строк, матричные шины столбцов и строк (выходы устройства, являющиеся входами управления командной матрицы), шины питания +Е и -Е, причем шина питания +Е соединена с группой ключей коммутации столбцов, а шина питания -Е соединена с группой ключей коммутации строк, информационные входы регистра столбцов соединены с входами приема данных столбцов, информационные входы регистра строк соединены с входами приема данных строк, выходы регистра столбцов соединены с входами дешифратора столбцов, выходы которого соединены с входами группы ключей коммутации столбцов, выходы которых соединены с матричной шиной столбов, выходы регистра строк соединены с входами дешифратора строк, выходы которого соединены с входами группы ключей коммутации строк, выходы которых соединены с матричной шиной строк, а вход записи данных соединен с входами синхронизации регистров столбцов и строк (см. описанный прототип в материалах заявки №2013119891 от 29.04.2013 г.).

В узлах столбцов и строк командной матрицы такого устройства установлены реле с развязывающими диодами, причем первая группа контактов реле соединена с шиной питания командной матрицы, а вторая группа контактов реле является выходами командной матрицы. По существенным признакам и выполняемым функциям такое устройство может быть признано прототипом.

Недостатками указанного устройства является отсутствие контроля неисправности своего состояния, позволяющего запрещать исполнение команды, если возникли условия для ложного формирования команды (например, за счет отказов в регистрах, дешифраторах или ключах коммутации столбцов и строк), а также отсутствие блокировки записи новых данных, поступающих на информационные входы формирователя матричных команд для формирования следующей команды во время формирования предыдущей команды.

Задачей предлагаемого изобретения является повышение надежности формирователя матричных команд за счет обеспечения контроля неисправности своего состояния, позволяющего при обнаружении неисправности исключать ложное срабатывание исполнительных элементов командной матрицы, а также за счет исключения условий возможности формирования в любой момент более одной команды.

Указанный технический результат достигается за счет того, что в формирователь матричных команд, содержащий шины приема данных столбцов и строк, вход записи данных, регистры столбцов и строк, первые дешифраторы столбцов и строк, группы ключей коммутации столбцов и строк, матричные шины столбцов и строк, шины питания +Е и -Е, причем шина питания +Е соединена с группой ключей коммутации столбцов, а шина питания -Е соединена с группой ключей коммутации строк, первая группа информационных входов регистра столбцов соединена с шиной приема данных столбцов, первая группа информационных входов регистра строк соединена с шиной приема данных строк, первая группа выходов регистра столбцов соединена с входами первого дешифратора столбцов, выходы которого соединены с входами группы ключей коммутации столбцов, выходы которых соединены с матричной шиной столбцов, первая группа выходов регистра строк соединена с входами первого дешифратора строк, выходы которого соединены с входами группы ключей коммутации строк, выходы которых соединены с матричной шиной строк, введены вторые дешифраторы столбцов строк, схемы контроля состояния столбцов и строк, схемы обнаружения неисправности в столбцах и строках, регистраторы приема данных столбцов и строк, первая и вторая схемы задержки, первый и второй ключи коммутации матричного питания и матричная шина питания, причем шина приема данных столбцов соединена со второй группой информационных входов регистра столбцов, вторая группа выходов которого соединена с входами второго дешифратора столбцов, шина приема данных строк соединена со второй группой информационных входов регистра строк, вторая группа выходов которого соединена с входами второго дешифратора строк, шина питания -Е соединена со схемой контроля состояния столбцов, входы которой соединены с выходами группы ключей коммутации столбцов, а выходы которой соединены с первой группой входов сравнения схемы обнаружения неисправности в столбцах, вторая группа входов сравнения которой соединена с выходами второго дешифратора столбцов, шина питания +Е соединена со схемой контроля состояния строк, входы которой соединены с выходами группы ключей коммутации строк, а выходы которой соединены с первой группой входов сравнения схемы обнаружения неисправности в строках, вторая группа входов сравнения которой соединена с выходами второго дешифратора строк, первая группа входов регистратора приема данных столбцов соединена с выходами первого дешифратора столбцов, вторая группа входов которого соединена с выходами второго дешифратора столбцов, а выход которого соединен через первую схему задержки с управляющим входом схемы обнаружения неисправности в столбцах, выход которой соединен с входом первого ключа коммутации матричного питания, первая группа входов регистратора приема данных строк соединена с выходами первого дешифратора строк, вторая группа входов которого соединена с выходами второго дешифратора строк, а выход которого соединен через вторую схему задержки с управляющим входом схемы обнаружения неисправности в строках, выход которой соединен с входом второго ключа коммутации матричного питания, шина питания +Е соединена с первым ключом коммутации матричного питания, выход которого соединен со вторым ключом коммутации матричного питания, выход которого соединен с матричной шиной питания, а также введены третья и четвертая схемы задержки и элемент ИЛИ, причем выход регистратора приема данных столбцов соединен с первым входом элемента ИЛИ и через третью схему задержки с входом сброса регистра столбцов, выход регистратора приема данных строк соединен со вторым входом элемента ИЛИ и через четвертую схему задержки с входом сброса регистра строк, а вход записи данных соединен с третьим входом элемента ИЛИ, выход которого соединен с входами синхронизации регистров столбцов и строк.

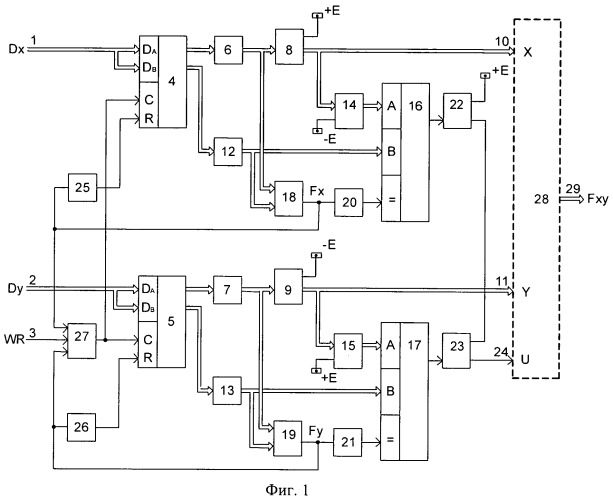

Суть изобретения поясняется функциональными схемами предлагаемого формирователя матричных команд (фиг.1) и подключаемой к нему командной матрицы (фиг.2).

Формирователь матричных команд (фиг.1) содержит шины приема данных 1 и 2 столбцов и строк (информационные входы формирователя, на которые поступают коды данных DX столбцов и DY строк), вход записи данных 3 (вход синхронизации формирователя, на который поступает строб WR для записи данных DX и DY), регистры 4 и 5 столбцов и строк, первые дешифраторы 6 и 7 столбцов и строк, группы ключей 8 и 9 коммутации столбцов и строк, матричные шины 10 и 11 столбцов и строк (выходы формирователя, являющиеся входами управления столбцами Х и строками Y командной матрицы), шины питания +Е и -Е, причем шина питания +Е соединена с группой ключей 8 коммутации столбцов, а шина питания -Е соединена с группой ключей 9 коммутации строк, первая группа информационных входов (входы DA) регистра 4 столбцов соединена с шиной приема данных 1 столбцов, первая группа информационных входов (входы DA) регистра 5 строк соединена с шиной приема данных 2 строк, первая группа выходов регистра 4 столбцов соединена с входами первого дешифратора 6 столбцов, выходы которого соединены с входами группы ключей 8 коммутации столбцов, выходы которых соединены с матричной шиной 10 столбцов, первая группа выходов регистра 5 строк соединена с входами первого дешифратора 7 строк, выходы которого соединены с входами группы ключей 9 коммутации строк, выходы которых соединены с матричной шиной 11 строк, отличающийся тем, что в него введены вторые дешифраторы 12 и 13 столбцов и строк, схемы контроля 14 и 15 состояния столбцов и строк, схемы обнаружения неисправности 16 и 17 в столбцах и строках, регистраторы 18 и 19 приема данных столбцов и строк, первая и вторая схемы задержки 20 и 21, первый и второй ключи 22 и 23 коммутации матричного питания и матричная шина питания 24 (выход формирователя матричных команд, являющийся входом подачи питания U на командную матрицу), причем шина приема данных 1 столбцов соединена со второй группой информационных входов (входы DB) регистра 4 столбцов, вторая группа выходов которого соединена с входами второго дешифратора 12 столбцов, шина приема данных 2 строк соединена со второй группой информационных входов (входы DB) регистра 5 строк, вторая группа выходов которого соединена с входами второго дешифратора 13 строк, шина питания -Е соединена со схемой контроля 14 состояния столбцов, входы которой соединены с выходами группы ключей 8 коммутации столбцов, а выходы которой соединены с первой группой входов сравнения (входы А) схемы обнаружения неисправности 16 в столбцах, вторая группа входов сравнения которой (входы В) соединена с выходами второго дешифратора 12 столбцов, шина питания +Е соединена со схемой контроля 15 состояния строк, входы которой соединены с выходами группы ключей 9 коммутации строк, а выходы которой соединены с первой группой входов сравнения (входы А) схемы обнаружения неисправности 17 в строках, вторая группа входов сравнения которой (входы В) соединена с выходами второго дешифратора 13 строк, первая группа входов регистратора 18 приема данных столбцов соединена с выходами первого дешифратора 6 столбцов, вторая группа входов которого соединена с выходами второго дешифратора 12 столбцов, а выход которого (выход формирования импульсного сигнала FX, определяющего длительность подключения столбцов командной матрицы к шине питания +Е) соединен через первую схему задержки 20 с управляющим входом (вход =) схемы обнаружения неисправности 16 в столбцах, выход которой соединен с входом первого ключа 22 коммутации матричного питания, первая группа входов регистратора 19 приема данных строк соединена с выходами первого дешифратора 7 строк, вторая группа входов которого соединена с выходами второго дешифратора 13 строк, а выход которого (выход формирования импульсного сигнала FY, определяющего длительность подключения строк командной матрицы к шине питания -Е) соединен через вторую схему задержки 21 с управляющим входом (вход =) схемы обнаружения неисправности 17 в строках, выход которой соединен с входом второго ключа 23 коммутации матричного питания, шина питания +Е соединена с первым ключом 22 коммутации матричного питания, выход которого соединен со вторым ключом 23 коммутации матричного питания, выход которого соединен с матричной шиной питания 24, а также введены третья и четвертая схемы задержки 25 и 26 и элемент ИЛИ 27, причем выход регистратора 18 приема данных столбцов соединен с первым входом элемента ИЛИ 27 и через третью схему задержки 25 с входом сброса (R-вход) регистра 4 столбцов, выход регистратора 19 приема данных строк соединен со вторым входом элемента ИЛИ 27 и через четвертую схему задержки 26 с входом сброса (R-вход) регистра 5 строк, а вход записи данных 3 соединен с третьим входом элемента ИЛИ 27, выход которого соединен с входами синхронизации (С-входы) регистров 4 и 5 столбцов и строк.

Группы ключей 8 и 9 коммутации столбцов и строк, а также первый и второй ключи 22 и 23 коммутации матричного питания обеспечивают гальваническую развязку логических цепей от шин питания +Е и -Е.

Схемы контроля 14 и 15 состояния столбцов и строк обеспечивают гальваническую развязку коммутируемых столбцов и строк от логических цепей.

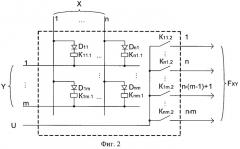

Командная матрица 28, входы управления Х столбцами и Y строками которой соединены с матричными шинами 10 и 11 столбцов и строк, вход подачи питания U которой соединен с матричной шиной питания 24, а группа выходов FXY соединена с выходной шиной 29, реализуется отдельно, не относится к признакам заявленного устройства, которое может обслуживать несколько групп исполнительных органов командной матрицы, распределенных по различным устройствам системы управления в целом. Командная матрица 28 (фиг.2) содержит n столбцов и m строк, образующие входы управления Х и Y, в узлах которых установлены обмотки реле К11.1, …, Kn1.1, …, K1m.1, …, Knm.1 с развязывающими диодами D11, …, Dn1, …, D1m, …, Dnm, причем первые выводы контактов реле К11.2, …, Kn1.2, …, K1m.2, …, Knm.2 соединены с входом подачи питания U, а вторые выводы контактов реле К11.2, …, Kn1.2, …, K1m.2, …, Knm.2 соединены соответственно с выходными цепями 1, …, n, …, n(m-1)+1, …, nm группы выходов FXY. Формирование линейных команд с группы выходов FXY происходит в соответствии с логическим равенством FXY=XYU при замыкании входов управления Х и Y столбцами и строками на соответствующие шины питания +Е и -Е и замыкании входа подачи питания U на шину питания +Е.

Предлагаемый формирователь матричных команд работает следующим образом.

В начальном состоянии первая и вторая группа выходов регистров 4 и 5 столбцов и строк находятся в нулевом состоянии, при котором отсутствуют управляющие воздействия с выходов первых дешифраторов 6 и 7 столбцов и строк на группы ключей 8 и 9 коммутации столбцов и строк, что соответствует отсутствию условий формирования команд управления на матричные шины 10 и 11 столбцов и строк, а также отсутствию информации с выходов схем контроля 14 и 15 о состоянии столбцов и строк и с выходов вторых дешифраторов 12 и 13 о номере выбранных столбцов и строк, поступающие на первую и вторую группу входов сравнения (входы А и В) схем обнаружения неисправности 16 и 17 в столбцах и строках. В этом состоянии с выходов регистраторов 18 и 19 приема данных столбцов и строк, реализующих функции ИЛИ, не формируются сигналы управления Fx и Fy, которые должны поступать через соответствующие первую и вторую схемы задержки 20 и 21 на управляющие входы (вход =) схем обнаружения неисправности 16 и 17 в столбцах и строках для формирования сигнала включения первого и второго ключей 22 и 23 коммутации матричного питания. При этом на матричной шине питания 24 будет отсутствовать напряжение U питания командной матрицы 28. Это состояние сохраняется до тех пор, пока на шины приема данных 1 и 2 столбцов и строк не поступят входные данные Dx и Dy на выбор требуемых столбцов и строк.

При поступлении входных данных Dx и Dy на шины приема данных 1 и 2 столбцов и строк происходит одновременная их подача на две группы входов (входы DA и DB) регистров 4 и 5 столбцов и строк и фиксация в регистрах в дублированном виде на первой и второй группах выходов по стробу записи WR, поступающему с входа записи данных 3 через элемент ИЛИ 27 на их входы синхронизации (С-входы). С этого момента начинается процесс формирования матричной команды. Зафиксированные в первой и второй группах выходов регистров 4 и 5 столбцов и строк дублированные входные данные Dx и Dy дешифрируются первыми дешифраторами 6 и 7 столбцов и строк и вторыми дешифраторами 12 и 13 столбцов и строк. При этом по сигналам активных выходов первых дешифраторов 6 и 7 столбцов и строк открываются соответствующие ключи групп ключей 8 и 9 коммутации столбцов и строк и замыкают шины питания +Е и -Е на соответствующие столбцы и строки матричных шин 10 и 11 столбцов и строк для активизации исполнительных элементов в соответствующем узле командной матрицы 28. Схемы контроля 14 и 15 состояния столбцов и строк отслеживают эти состояния и формируют на своих выходах соответствующие этим состояниям логические уровни, которые при отсутствии неисправности в формирователе повторяют дешифрированные данные с выходов первых дешифраторов 6 и 7 столбцов и строк. Одновременно на соответствующих выходах вторых дешифраторов 12 и 13 столбцов и строк появляются сигналы, дублирующие состояние выходов схем контроля 14 и 15 состояния столбцов и строк. Эти сигналы поступают на входы сравнения А и В схем обнаружения неисправности 16 и 17 в столбцах и строках для анализа.

Если сигналы на входах сравнения А и В схем обнаружения неисправности 16 и 17 в столбцах и строках совпали (случай, когда нет отказов в функциональных элементах формирователя), разрешается прохождение сигналов управления Fx и Fy с выходов регистраторов 18 и 19 приема данных столбцов и строк через соответствующие первую и вторую схемы задержки 20 и 21 и схемы обнаружения неисправности 16 и 17 в столбцах и строках на включение первого и второго ключей 22 и 23 коммутации матричного питания. В результате напряжение с шины питания +Е подается через замкнутые ключи 22 и 23 на матричную шину питания 24 и вход подачи питания U командной матрицы 28 и разрешает в соответствии с логическим равенством FXY=XYU исполнение матричной команды, при этом на выходной шине 29 формируется линейная команда Fxy.

Если сигналы на входах сравнения А и В схем обнаружения неисправности 16 и 17 в столбцах и строках не совпадают (случай, когда в каком-то одном из функциональных элементов произошел отказ, например, при возникновении короткого замыкания или обрыва одного из ключей групп ключей 8 и 9 коммутации столбцов или строк), запрещается прохождение сигналов управления Fx и Fy с выходов регистраторов 18 и 19 приема данных столбцов и строк через соответствующие первую и вторую схемы задержки 20 и 21 и схемы обнаружения неисправности 16 и 17 в столбцах и строках на включение первого и второго ключей 22 и 23 коммутации матричного питания. Схемы задержки 20 и 21 исключают преждевременное включение первого и второго ключей 22 и 23 коммутации матричного питания, пока не завершатся переходные процессы в ключах групп ключей 8 и 9 коммутации столбцов и строк и схемах контроля 14 и 15 состояния столбцов и строк, вызванные их низким быстродействием по сравнению с логическими элементами, которые могут привести при наличии отказов в функциональных элементах формирователя к кратковременному ложному разрешению исполнения матричной команды. В результате ключи 22 и 23 коммутации матричного питания остаются разомкнутыми и напряжение с шины питания +Е не поступает на матричную шину питания 24 и вход подачи питания U командной матрицы 28 и в соответствии с логическим равенством FXY=XYU отсутствует разрешение исполнения матричной команды, при этом на выходной шине 29 линейная команда Fxy не формируется.

Длительность матричной команды определяется временем задержки третьей и четвертой схем задержки 25 и 26, которые задерживают сигналы управления Fx и Fy с выходов регистраторов 18 и 19 приема данных столбцов и строк на сброс в регистрах 4 и 5 столбцов и строк зафиксированных входных данных Dx и Dy на время требуемой длительности матричной команды. Если во время формирования матричной команды поступят новые входные данные Dx и Dy на формирование следующей команды, то запись этих данных по сигналу WR через схему ИЛИ 27 будет заблокирована сигналами управления Fx и Fy.

Таким образом, по сравнению с прототипом в предлагаемом формирователе матричных команд техническим результатом является повышение надежности за счет исключения возможности ложного срабатывания исполнительных элементов командной матрицы либо при любых одиночных отказах в нем функциональных элементов, либо при преждевременном поступлении на информационные входы новых данных на формирование следующей команды во время формирования предыдущей команды.

Рассмотренный формирователь матричных команд найдет применение в аппаратуре управления исполнительными элементами служебных систем космических аппаратов. В настоящее время такой формирователь находится на стадии внедрения в конструкторскую документацию различных изделий предприятия и реализован на следующих элементах: логические устройства на интегральных микросхемах серии 1554, ключи коммутации столбцов и строк командной матрицы на микросборках с ВК16-3 трансформаторной развязкой по управлению, схемы контроля состояния столбцов и строк на оптоэлектронных микросхемах 249КП1С, ключи коммутации матричного питания на МОП-реле 249КП5Р.

Из известных заявителю патентно-информационных материалах не обнаружены признаки, сходные с совокупностью признаков заявляемого объекта.

1. Формирователь матричных команд, содержащий шины приема данных столбцов и строк, вход записи данных, регистры столбцов и строк, первые дешифраторы столбцов и строк, группы ключей коммутации столбцов и строк, матричные шины столбцов и строк, шины питания +Е и -Е, причем шина питания +Е соединена с группой ключей коммутации столбцов, а шина питания -Е соединена с группой ключей коммутации строк, первая группа информационных входов регистра столбцов соединена с шиной приема данных столбцов, первая группа информационных входов регистра строк соединена с шиной приема данных строк, первая группа выходов регистра столбцов соединена с входами первого дешифратора столбцов, выходы которого соединены с входами группы ключей коммутации столбцов, выходы которых соединены с матричной шиной столбцов, первая группа выходов регистра строк соединена с входами первого дешифратора строк, выходы которого соединены с входами группы ключей коммутации строк, выходы которых соединены с матричной шиной строк, отличающийся тем, что в него введены вторые дешифраторы столбцов и строк, схемы контроля состояния столбцов и строк, схемы обнаружения неисправности в столбцах и строках, регистраторы приема данных столбцов и строк, первая и вторая схемы задержки, первый и второй ключи коммутации матричного питания и матричная шина питания, причем шина приема данных столбцов соединена со второй группой информационных входов регистра столбцов, вторая группа выходов которого соединена с входами второго дешифратора столбцов, шина приема данных строк соединена со второй группой информационных входов регистра строк, вторая группа выходов которого соединена с входами второго дешифратора строк, шина питания -Е соединена со схемой контроля состояния столбцов, входы которой соединены с выходами группы ключей коммутации столбцов, а выходы которой соединены с первой группой входов сравнения схемы обнаружения неисправности в столбцах, вторая группа входов сравнения которой соединена с выходами второго дешифратора столбцов, шина питания +Е соединена со схемой контроля состояния строк, входы которой соединены с выходами группы ключей коммутации строк, а выходы которой соединены с первой группой входов сравнения схемы обнаружения неисправности в строках, вторая группа входов сравнения которой соединена с выходами второго дешифратора строк, первая группа входов регистратора приема данных столбцов соединена с выходами первого дешифратора столбцов, вторая группа входов которого соединена с выходами второго дешифратора столбцов, а выход которого соединен через первую схему задержки с управляющим входом схемы обнаружения неисправности в столбцах, выход которой соединен с входом первого ключа коммутации матричного питания, первая группа входов регистратора приема данных строк соединена с выходами первого дешифратора строк, вторая группа входов которого соединена с выходами второго дешифратора строк, а выход которого соединен через вторую схему задержки с управляющим входом схемы обнаружения неисправности в строках, выход которой соединен с входом второго ключа коммутации матричного питания, шина питания +Е соединена с первым ключом коммутации матричного питания, выход которого соединен со вторым ключом коммутации матричного питания, выход которого соединен с матричной шиной питания.

2. Формирователь матричных команд по п.1, отличающийся тем, что в него введены третья и четвертая схемы задержки и элемент ИЛИ, причем выход регистратора приема данных столбцов соединен с первым входом элемента ИЛИ и через третью схему задержки с входом сброса регистра столбцов, выход регистратора приема данных строк соединен со вторым входом элемента ИЛИ и через четвертую схему задержки с входом сброса регистра строк, а вход записи данных соединен с третьим входом элемента ИЛИ, выход которого соединен с входами синхронизации регистров столбцов и строк.