Демодулятор сигналов с относительной фазовой модуляцией

Иллюстрации

Показать всеИзобретение относится к области приема цифровых сигналов, передаваемых методом относительной фазовой модуляции (ОФМ), и может быть использовано для построения устройств демодуляции. Технический результат заключается в снижении ошибок, возникающих в результате воздействия помех, за счет изменения уровня напряжения порога по квадратическому закону, в зависимости от значений «единица» или «нуль», полученных на выходе решающего блока на предыдущих циклах, тем самым обеспечивая повышение помехоустойчивости. Для этого формируют автокорреляционную функцию сигнала, интегрируют ее и сравнивают с пороговым значением, которое формируют в зависимости от наличия демодулируемого логического сигнала «единица» или «ноль» на предыдущем цикле. Для чего дополнительно введен блок адаптации порога (БАП), вход начального уровня порога, сигнальный вход, вход адаптивного порога и выход которого подключены соответственно к выходу генератора константы, к выходу решающего блока, к выходу формирующего блока и к входу порогового уровня решающего блока. При этом БАП состоит из сумматора, корректора полярности, нелинейного корректора и вычитателя, причем первый вход вычитателя является входом начального уровня порога БАП, а второй вход является входом адаптивного порога БАП, выход вычитателя подключен к входу нелинейного корректора БАП, выход которого подключен к второму входу корректора полярности, первый вход которого является сигнальным входом БАП, а выход корректора полярности подключен к второму входу сумматора, выход которого является выходом БАП, а первый вход сумматора является входом начального уровня порога БАП. 3 з.п. ф-лы, 8 ил.

Реферат

Изобретение относится к области радиотехники, а именно к устройствам приема и демодуляции цифровых сигналов, передаваемых методом относительной фазовой модуляции (ОФМ).

Известен демодулятор сигналов с ОФМ [Патент РФ №2099892, 1997 г., МПК6 H04L 27/22], состоящий из фильтра, двух корреляторов, двух блоков стробирования, решающего блока, генератора опорного колебания, фазовращателя и генератора тактовых импульсов, причем вход первого блока стробирования соединен с выходом первого коррелятора, вход второго блока стробирования подключен к выходу второго коррелятора, вход фазовращателя подключен к выходу генератора опорного колебания. Входы установки обоих корреляторов соединены вместе и подключены к первому выходу генератора тактовых импульсов. Входы управления обоих блоков стробирования соединяются с вторым выходом генератора тактовых импульсов. Вход фильтра служит входом демодулятора, выходом которого является выход решающего блока. Кроме того, в составе демодулятора имеется ограничитель, два блока выделения знака и блок формирования оценки фазы, состоящий из двух инверторов, двух блоков выделения знака, коммутатора, двух блоков вычисления модуля, блока сравнения, генератора констант, сумматора. Выход фильтра соединен с входом ограничителя, выход которого подключен к соединенным вместе первым входам корреляторов. Второй вход первого коррелятора соединен с выходом первого блока выделения знака, вход которого подключен к выходу генератора опорного колебания. Второй вход второго коррелятора соединен с выходом второго блока выделения знака, вход которого подключен к выходу фазовращателя. Первый информационный вход коммутатора вместе с входом первого инвертора, входом третьего блока выделения знака и входом первого блока вычисления модуля служат первым входом блока формирования оценки фазы и соединены с выходом первого блока стробирования. Четвертый информационный вход коммутатора вместе с входом второго инвертора, входом четвертого блока выделения знака и входом второго блока вычисления модуля служат вторым входом блока формирования оценки фазы и соединены с выходом второго блока стробирования. Выход первого инвертора соединен со вторым информационным входом коммутатора, выход второго инвертора соединен с третьим информационным входом коммутатора, выход третьего блока выделения знака подключен к соединенным вместе первым управляющим входам коммутатора и генератора констант, выход четвертого блока выделения знака подключен к соединенным вместе вторым управляющим входам коммутатора и генератора констант. Выход первого блока вычисления модуля подключен к первому входу блока сравнения, второй вход которого подключен к выходу второго блока вычисления модуля. Выход блока сравнения подключен к соединенным вместе третьим управляющим входам коммутатора и генератора констант. Выход коммутатора подключен к первому входу сумматора, второй вход которого подключен к выходу генератора констант, выход сумматора служит выходом блока формирования оценки фазы и соединен с входом решающего блока.

Недостатком известного устройства является относительно низкая помехоустойчивость обусловленная тем, что при демодуляции в качестве опорных сигналов используют последовательности импульсов прямоугольной формы. Это приводит к нелинейной зависимости получаемой фазы сигнала из-за отсутствия учета изменений фазы демодулируемого сигнала под воздействием помех, действующих в полосе частот принимаемого сигнала.

Известен демодулятор сигналов с ОФМ [Патент РФ №2271071, 2006 г., МПК6 H04L 27/22], состоящий из фильтра, вход которого является входом для демодулируемого сигнала ОФМ, блока стабилизации амплитуды фазоманипулированного сигнала, вход которого подключен к выходу фильтра, а выход - к первому сигнальному входу коррелятора, второй сигнальный вход которого соединен с выходом генератора опорного сигнала, коррелятора, включающего в себя умножитель напряжений, оба входа которого являются сигнальными входами коррелятора, блока уменьшения уровня помехи, вход которого соединен с выходом умножителя напряжений, а выход - с сигнальным входом интегратора коррелятора, выход которого является выходом коррелятора, а вход сброса интегратора коррелятора является входом установки коррелятора, генератора тактовых импульсов, блока стробирования, соединенного с выходом коррелятора, а вход установки коррелятора подключен к первому выходу генератора тактовых импульсов, ко второму выходу которого подключен вход управления блока стробирования, при этом выход блока стробирования соединен с первым входом и через схему задержки на длительность Т с вычитающим входом схемы вычитания, а выход схемы вычитания соединен с входом блока вычисления модуля, вход которого соединен с первым входом решающей схемы, которая включает в себя последовательно соединенные компаратор напряжений и D-тригтер, выход которого является выходом решающей схемы, а инвертирующий вход компаратора напряжений является вторым входом решающей схемы, который соединен с генератором константы, при этом управляющий вход решающей схемы, являясь входом синхронизации D-триггера, соединен со вторым выходом генератора тактовых импульсов.

Недостатком известного устройства является относительно низкая помехоустойчивость, обусловленная тем, что используемый в устройстве блок уменьшения уровня помехи лишь частично устраняет воздействие помех, появляющихся вследствие применения операции формирования из отфильтрованного демодулируемого сигнала последовательности прямоугольных импульсов.

Наиболее близким по своей технической сущности является устройство демодуляции сигналов с ОФМ (устройство) [Патент РФ №2460225, опубликовано: 27.08.2012 Бюл. №24]. Устройство-прототип состоит из генератора опорного сигнала, выход которого подключен к входу опорного напряжения коррелятора, сигнальный вход которого подключен к выходу стабилизатора амплитуды, вход которого подключен к выходу фильтра, вход которого является входом демодулятора, генератора тактовых импульсов, первый выход которого подключен к тактовому входу коррелятора, выход которого подключен к сигнальному входу блока стробирования, тактовый вход которого подключен к второму выходу генератора тактовых импульсов и тактовому входу решающего блока, сигнальный вход которого подключен к выходу блока вычисления модуля, вход которого подключен к выходу блока вычитания, вход которого подключен к выходу блока стробирования и входу блока задержки на длительность Т, генератора константы, причем выход решающего блока является выходом демодулятора, ограничителя амплитуды, вход которого подключен к выходу блока задержки на длительность Т, а выход подключен к второму входу блока вычитания, формирующего блока, вход уровня порога, сигнальный вход и выход которого подключены соответственно к выходу генератора константы, к выходу решающего блока и к входу уровня порога решающего блока. Формирующий блок состоит из коммутатора, вход уровня порога которого является входом уровня порога блока, а вход отключения генератора константы коммутатора подключен к выходу переключателя константы, выход коммутатора подключен к входу начального уровня формирователя порога, выход которого является выходом блока, а корректирующий вход формирователя порога подключен к выходу корректора порога, вход которого подключен к входу переключателя константы и является сигнальным входом блока.

Недостатком известного устройства-прототипа является относительно низкая помехоустойчивость. Это объясняется тем, что используемый в устройстве формирующий блок, корректирующий порог принятия решения, лишь частично устраняет негативное воздействие помех, приводящих к ошибкам в канале связи. Указанный недостаток обусловлен тем, что под воздействием помех, возникающих в канале связи, с блока вычисления модуля будет поступать неправильно вычисленное значение уровня напряжения, которые при линейно меняющемся уровне напряжения порога, поступающего с формирующего блока, приведет к неправильному принятию решения о демодулированном символе на выходе решающего блока.

Целью заявленного изобретения является разработка демодулятора сигналов с ОФМ, обеспечивающего снижение ошибок (возникающих в результате воздействия помех), за счет изменения уровня напряжения порога по квадратическому закону, в зависимости от значений «единица» или «нуль», полученных на выходе решающего блока на предыдущих циклах, тем самым обеспечивая повышение помехоустойчивости.

В заявленном устройстве поставленная цель достигается тем, что в известный демодулятор сигналов с относительной фазовой модуляцией, содержащий генератор опорного сигнала, выход которого подключен к входу опорного напряжения коррелятора, сигнальный вход коррелятора подключен к выходу стабилизатора амплитуды, вход которого подключен к выходу фильтра, вход которого является входом демодулятора, генератор тактовых импульсов, первый выход которого подключен к тактовому входу коррелятора, выход коррелятора подключен к сигнальному входу блока стробирования, тактовый вход которого подключен к второму выходу генератора тактовых импульсов и к тактовому входу решающего блока, сигнальный вход решающего блока подключен к выходу блока вычисления модуля, вход которого подключен к выходу блока вычитания, первый вход которого подключен к выходу блока стробирования и входу блока задержки на длительность Т, выход которого подключен к входу ограничителя амплитуды, выход которого подключен к второму входу блока вычитания, причем выход решающего блока является выходом демодулятора и соединен с сигнальным входом формирующего блока, вход уровня порога формирующего блока подключен к выходу генератора константы, дополнительно введен блок адаптации порога (БАП), вход начального уровня порога, сигнальный вход, вход адаптивного порога и выход которого подключены соответственно к выходу генератора константы, к выходу решающего блока, к выходу формирующего блока и к входу порогового уровня решающего блока. При этом коррелятор состоит из умножителя напряжения и интегратора, причем первый вход умножителя напряжений является входом опорного напряжения коррелятора, а второй вход умножителя напряжений является сигнальным входом коррелятора, выход умножителя напряжений подключен к первому входу интегратора, выход которого является выходом коррелятора, второй вход интегратора является тактовым входом коррелятора. При этом решающий блок состоит из компаратора напряжений и D-триггера, причем первый вход компаратора напряжений является сигнальным входом решающего блока, а второй вход компаратора напряжений является входом порогового уровня решающего блока, выход компаратора напряжений подключен к первому входу D-триггера, второй вход которого является тактовым входом решающего блока, выход D-триггера является выходом решающего блока. При этом формирующий блок состоит из коммутатора, вход уровня порога которого является входом уровня порога формирующего блока, а вход отключения генератора константы коммутатора подключен к выходу переключателя константы, выход коммутатора подключен к входу начального уровня формирователя порога, выход которого является выходом формирующего блока, а корректирующий вход формирователя порога подключен к выходу корректора порога, вход которого подключен к входу переключателя константы и является сигнальным входом формирующего блока. При этом БАП состоит из сумматора, корректора полярности, нелинейного корректора и вычитателя, причем первый вход вычитателя является входом начального уровня порога БАП, а второй вход является входом адаптивного порога БАП, выход вычитателя подключен к входу нелинейного корректора БАП, выход которого подключен к второму входу корректора полярности, первый вход которого является сигнальным входом БАП, а выход корректора полярности подключен к второму входу сумматора, выход которого является выходом БАП, а первый вход сумматора является входом начального уровня порога БАП.

Благодаря новой совокупности признаков, заключающихся в использовании блока адаптации порога в составе сумматора, корректора полярности, нелинейного корректора и вычитателя, в заявленном устройстве изменение уровня напряжения порога происходит по квадратическому закону. В результате снижается вероятность принятия неправильного решения при наличии относительно длинных повторяющихся последовательностей символов «нуля» или «единицы», вызванных ошибками в канале приема.

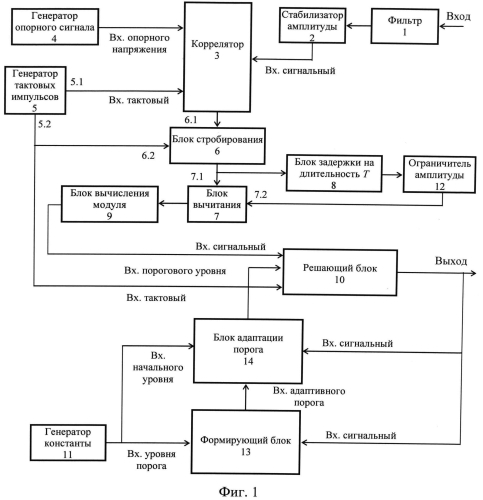

Заявленное изобретение поясняется чертежами, на которых показано:

на фиг.1 - блок-схема демодулятора сигналов с ОФМ;

на фиг.2 - блок-схема коррелятора демодулятора сигналов с ОФМ;

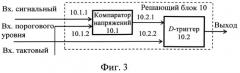

на фиг.3 - блок-схема решающего блока демодулятора сигналов с ОФМ;

на фиг.4 - блок-схема блока адаптации порога демодулятора сигналов с ОФМ;

на фиг.5 - блок-схема формирующего блока демодулятора сигналов с ОФМ;

на фиг.6 - временные диаграммы работы демодулятора в случае отсутствия ошибок в символах выходной последовательности;

на фиг.7 - временные диаграммы работы демодулятора в случае наличия ошибок, приводящих к преобладанию символов «единица» в выходной последовательности;

на фиг.8 - временные диаграммы работы демодулятора в случае наличия ошибок, приводящих к преобладанию символов «нуля» в выходной последовательности.

Заявленное устройство, показанное на фиг.1, поясняется примером конкретного исполнения демодулятора сигналов с ОФМ, состоящего из генератора опорного сигнала 4, выход которого подключен к входу опорного напряжения коррелятора 3, сигнальный вход коррелятора 3 подключен к выходу стабилизатора амплитуды 2, вход которого подключен к выходу фильтра 1, вход которого является входом демодулятора, генератора тактовых импульсов 5, первый выход 5.1 которого подключен к тактовому входу коррелятора 3, выход которого подключен к сигнальному входу 6.1 блока стробирования 6, тактовый вход 6.2 которого подключен к второму 5.2 выходу генератора тактовых импульсов 5 и тактовому входу решающего блока 10, сигнальный вход которого подключен к выходу блока вычисления модуля 9, вход которого подключен к выходу блока вычитания 7, вход 7.1 которого подключен к выходу блока стробирования 6 и входу блока задержки на длительность Г 8, а вход 7.2 подключен к выходу ограничителя амплитуды 12, вход которого подключен к выходу блока задержки на длительность Т 8, причем выход решающего блока 10 является выходом демодулятора и сигнальным входом блока адаптации порога 14 и формирующего блока 13, вход уровня порога которого соединен с выходом генератора константы 11, который также является а входом начального уровня блока адаптации порога 14, вход адаптивного порога и выход которого подключены соответственно к выходу формирующего блока 13, и к входу порогового уровня решающего блока 10.

При этом коррелятор 3 (см. фиг.2) состоит из умножителя напряжений 3.1, первый вход 3.1.1 и второй вход 3.1.2, которого являются соответственно входом опорного напряжения и сигнальным входом коррелятора 3, а выход умножителя напряжений 3.1 подключен к первому входу 3.2.1 интегратора 3.2, второй вход 3.2.2 и выход которого соответственно являются тактовым входом и выходом коррелятора 3, решающий блок 10 (фиг.3) состоит из компаратора напряжений 10.1, первый вход 10.1.1, и второй вход 10.1.2 которого соответственно являются сигнальным и входом порогового уровня решающего блока 10, а выход компаратора напряжений 10.1 подключен к первому входу 10.2.1 D-триггера 10.2, второй вход 10.2.2 и выход которого соответственно являются тактовым входом и выходом решающего блока 10, формирующий блок 13 (фиг.5) состоит из коммутатора 13.1, вход уровня порога 13.1.1 которого является входом уровня порога формирующего блока, а вход отключения генератора константы 13.1.2 коммутатора 13.1 подключен к выходу переключателя константы 13.4, выход коммутатора 13.1 подключен к входу начального уровня 13.2.1 формирователя порога 13.2, выход которого является выходом формирующего блока 13, а корректирующий вход 13.2.2 формирователя порога 13.2 подключен к выходу корректора порога 13.3, вход которого подключен к входу переключателя константы 13.4 и является сигнальным входом формирующего блока 13, блока адаптации порога 14 (фиг.4) состоит из вычитателя 14.4, первый вход 14.4.1 которого соединен с входом 14.1.1 сумматора 14.1 и является входом начального уровня блока адаптации порога 14, а второй вход 14.4.2 вычитателя 14.4 является входом адаптивного порога блока адаптации порога 14, выход вычитателя 14.4 подключен к входу нелинейного корректора 14.3, выход которого подключен к второму входу 14.2.2 корректора полярности 14.2, первый вход 14.2.1 которого является сигнальным входом блока адаптации порога 14, выход корректора полярности 14.3 подключен к второму входу 14.1.2 сумматора 14.1, выход которого является выходом блока адаптации порога 14.

Блоки, входящие в общую схему устройства имеют следующее назначение.

Фильтр 1 предназначен для ослабления частотных составляющих, находящихся вне полосы частот демодулируемого сигнала с ОФМ S(t). В качестве фильтра 1, например, можно использовать фильтр, требования к которому сформированы в [Зюко А.Г., Фалько А. И. и др. Помехоустойчивость и эффективность систем передачи информации. - М.: Радио и связь, 1975, с.263].

Стабилизатор амплитуды 2 предназначен для стабилизации амплитуды сигнала с ОФМ до заданного уровня. В качестве стабилизатора амплитуды 2 можно использовать устройство, предложенное в [А.с. №1737748, 04 27/22, 30.05.92. Бюл. №20].

Генератор опорного сигнала 4 предназначен для формирования опорного гармонического сигнала S0(t).

Генератор тактовых импульсов 5 предназначен для задания (формирования) тактовых интервалов времени, длительностью Т.

Варианты реализации генератора опорных сигналов 4 и генератора тактовых импульсов 5 известны и описаны в [Спилкер Дж. Цифровая спутниковая связь. Пер. с англ. / Под ред. В.В. Маркова. - М.: Связь, 1979, с.302-382].

Коррелятор 3 предназначен для вычисления корреляционной функции Y(t) посредством перемножения стабилизированного сигнала с ОФМ Sc(t) на опорный сигнал S0(t), используя находящиеся в его составе умножитель напряжений 3.1 и интегратор 3.2.

Умножитель напряжений 3.1 может быть реализован на микросхеме 174ПС1, описанной в [Патент РФ №2460225, опубликовано: 27.08.2012 Бюл. №24]. Интегратор 3.2 описан в [Титце У., Шенк К. Полупроводниковая схемотехника. Справочное руководство. / Пер. с нем. - М.: Мир, 1982].

Блок стробирования 6 предназначен для определения отсчетов Yn, в моменты времени Т. Блок стробирования 6 описан в [Патент РФ №2271071, 2006 г., МПК6 H04L 27/22].

С помощью блока задержки на длительность Т 8, ограничителя амплитуды 12, блока вычитания 7 и блока вычисления модуля 9 вычисляют абсолютное значение разности этих отсчетов (Yn-Yn-1).

Построение блоков 8, 7, 9 описано в [Справочник разработчика и конструктора РЭА. Элементная база. Кн.1. - М., 1993. Сост. Масленников М.Ю., Соболев Е.А. и др.]. Ограничитель амплитуды 12 можно, например, выполнить на операционном усилители серии 741, который описан в [К. Бриндли, Д. Карр. Карманный справочник инженера электронной техники / Пер. с англ. 4-е изд., перераб. - М.: Издательский дом «Додека-XXI», 2009. - с.182].

Решающий блок 10 предназначен для принятия решения о демодулируемом информационном символе в моменты времени Т. Он состоит из компаратора напряжений 10.1, используемого для сравнения уровня модуля корреляционной функции и уровня скорректированного порогового значения, и D-тригтера 10.2, формирующего логические значения элементов «единица» и «нуль» на выходе решающего блока 10 в соответствии с тактовыми интервалами.

Компаратор напряжений 10.1 и D-триггер 10.2 могут быть реализованы на микросхемах 597СА2 и 1564ТМ2 соответственно, описанных в [Справочник разработчика и конструктора РЭА. Элементная база. Кн.1. - М., 1993. Сост. Масленников М.Ю., Соболев Е.А. и др.].

Генератор константы 11 предназначен для формирования начального уровня порогового значения.

Генератор константы 11 можно, например, реализовать на резистивных делителях напряжения.

Формирующий блок 13 предназначен для формирования уровня скорректированного порогового значения. [Патент РФ №2460225, опубликовано: 27.08.2012 Бюл. №24]. Он состоит из коммутатора 13.1, предназначенного для отключения генератора константы 11 после установления начального уровня порогового значения; формирователя порога 13.2, предназначенного для непосредственного формирования уровня скорректированного порогового значения, путем суммирования предыдущего уровня скорректированного порогового значения и вычисленного корректором порога 13.3 значения корректирующего уровня; корректора порога 13.3, предназначенного для формирования значения корректирующего уровня в зависимости от логического значения «единица» или «нуль», поступающих с выхода решающего блока 10; переключателя константы 13.4, предназначенного для формирования сигнала отключения коммутатора 13.1 после установления начального уровня порогового значения.

Формирователь порога 13.2 и корректор порога 13.3 можно, например, реализовать на операционном усилители серии 741, описанном в [К. Бриндли, Д. Карр. Карманный справочник инженера электронной техники / Пер. с англ. 4-е изд., перераб. - М.: Издательский дом «Додека- XXI», 2009. - с. 182]. Коммутатор 13.1 можно, например, реализовать на микросхеме ключевого устройства серии 4016, описанной в [К. Бриндли, Д. Карр. Карманный справочник инженера электронной техники / Пер. с англ. 4-е изд., перераб. - М.: Издательский дом «Додека - XXI», 2009. - с. 113]. Переключатель константы 13.4 можно, например, реализовать на основе инвертора с двумя входами, один из которых инвертирующий, описанного, например, в [К. Бриндли, Д. Карр. Карманный справочник инженера электронной техники / Пер. с англ. 4-е изд., перераб. - М.: Издательский дом «Додека - XXI», 2009. - 480 с.].

Различные варианты реализации корректора порога 13.3 известны и описаны в указанной выше книге К. Бриндли, Д. Карр. на с. 182.

БАП 14 предназначен для адаптации по нелинейному закону уровня порога, сформированного формирующим блоком 13. БАП состоит из: вычитателя 14.4, предназначенного для выделения приращения уровня порога путем вычитания из уровня скорректированного порогового значения, сформированного формирующим блоком 13; значения начального уровня порога, задаваемого генератором константы 11; нелинейного корректора 14.3, предназначенного для нелинейной коррекции выделенного приращения уровня порога, путем его возведения в квадрат; корректора полярности 14.2, предназначенного для восстановления знака напряжения приращения скорректированного порога после нелинейной коррекции; сумматора 14.1, предназначенного для непосредственного формирования уровня адаптированного порогового значения путем суммирования скорректированного приращения порогового уровня и начального уровня порогового значения.

Сумматор 14.1 и вычитатель 14.4 можно реализовать, например, на операционном усилителе серии 741, описанном в [К. Бриндли, Д. Карр. Карманный справочник инженера электронной техники / Пер. с англ. 4-е изд., перераб. - М.: Издательский дом «Додека-XXI», 2009. - с.182]. Нелинейный корректор 14.3 можно реализовать на перемножителе, включенном по схеме квадратора, например, на микросхеме 525ПС2, описанной в [Алексенко А.Г. и др. Применение прецизионных аналоговых микросхем 2-е изд., перераб. и доп. - М.: Радио и связь, 1985. - 256 с.]. Корректор полярности можно реализовать, например, на операционном усилители серии 741, описанном в [К. Бриндли, Д. Карр. Карманный справочник инженера электронной техники / Пер. с англ. 4-е изд., перераб. - М.: Издательский дом «Додека-XXI», 2009. - с.182].

В основу сущности работы устройства демодуляции сигналов с ОФМ положен принцип повышения достоверности принятия решения о принятом символе в выходной последовательности демодулятора за счет изменения уровня порога в зависимости от совокупности логических значений «единица» или «нуля», пронятых на предыдущих тактах.

Двоичный сигнал на выходе отдельных ступеней формирования групповых потоков может иметь произвольную статистическую структуру следования значений «единица» и «нуль», что не удовлетворяет требованиям к постоянству спектральной плотности мощности передаваемого сигнала. Поэтому в передающей части канала связи после операции кодирования осуществляют операцию скремблирования, обеспечивающую равномерное распределение информационных элементов «единица» и «нуль» в выходной последовательности [см. Григорьев В.А. Сигналы современных зарубежных систем электросвязи: Учебник. - СПб.: ВАС, 2007, с.126-127]. Следовательно, если появление значений «единица» и «нуль» в выходной последовательности модулятора перестает быть равномерным, то это говорит об ошибках, возникающих в канале связи.

Заявленное устройство работает следующим образом. Приходящий по каналу связи сигнал S(t) поступает на вход фильтра 1, являющийся входом демодулятора. В фильтре 1 осуществляется ослабление частотных составляющих, находящихся вне полосы частот демодулируемого сигнала. С выхода фильтра 1 отфильтрованный сигнал Sc(t)=Uccos(2pf0t+φ0) с длительностью элемента сигнала T, где Uc - амплитуда, f0 - средняя частота, φ0 - начальная фаза, определяется информационным символом передаваемой информации и принимает значения {0, π}, поступает на вход стабилизатора амплитуды 2, где осуществляется выравнивание амплитуды сигнала. Затем отфильтрованный сигнал с выровненной амплитудой поступает на вход 3.1.2 умножителя напряжений 3.1. На другой вход 3.1.1 умножителя напряжений 3.1 поступает с генератора опорного сигнала 4 опорный сигнал S0(t)=U0cos(2pf0t) с постоянной амплитуды U0. С выхода умножителя напряжений 3.1 сигнал произведения Sc(t) S0(t) поступает на вход 3.2.1 интегратора 3.2. На другой вход 3.2.2 интегратора 3.2 через каждый интервал времени Т поступает тактовый импульс с выхода 5.1 генератора тактовых импульсов 5. В результате, на выходе коррелятора 3 формируется корреляционная функция Y(t) (фиг.6а), которая поступает на вход 6.1 блока стробирования 6. В блоке стробирования 6 в момент окончания интегрирования по тактовому сигналу с выхода 5.2 генератора тактовых импульсов 5 происходит взятие отсчетов Yn функции корреляции Y(t). В результате формируется последовательность импульсов Yn с амплитудой ±Uk (фиг.6б).

Посредством тактового сигнала с выхода 5.1 генератора тактовых импульсов 5 значение корреляционной функции Y(t) в интеграторе 3.2 сбрасывается в нуль, и после этого происходит формирование корреляционной функции для следующего элемента сигнала.

С выхода блока стробирования 6 сигнал Yn поступает на вход 7.1 блока вычитания 7 и через блок задержки на длительность T 8 на ограничитель амплитуды 12, где значения амплитуды импульсов снижается до величины ±Ul. В результате на выходе ограничителя амплитуд формируется последовательность импульсов Yn-1 с амплитудой ±Ul, фиг.6в.

С выхода ограничителя амплитуды 12, задержанная на один такт последовательность импульсов Yn-1 поступает на вход 7.2 блока вычитания 7, где вычисляется разность между значениями последовательностей импульсов Yn и Yn-1, которая затем поступает на вход блока вычисления модуля 9, где осуществляется инверсия отрицательных значений.

С выхода блока вычисления модуля 9 последовательность | p Y n | , представляющая модуль разности последовательностей импульсов Yn и Yn-1, поступает на вход 10.1.1 компаратора напряжений 10.1, фиг.6г, на другой вход 10.1.2 компаратора напряжений 10.1 подается значение уровня порога Y п о р к о р с выхода сумматора 14.1 (см. фиг.6г).

В формирующем блоке 13 величина уровня порога формируется как сумма значений Y п о р к о р = Y п о р + Δ Y п о р п , поступающих соответственно с выхода коммутатора 13.1 на вход 13.2.1 формирователя порога 13.2 и с выхода корректора порога 13.3 на вход 13.2.2. Уровень напряжения Yпор определяется генератором константы 11 и подается на вход 13.1.1 коммутатора 13.1, который отключает генератор константы от входа 13.2.1 с началом работы заявляемого устройства сигналом, подаваемым на вход 13.1.2 с переключателя константы 13.4. Переключатель константы 13.4 начинает работать с подачи на его вход сигнала с выхода D-триггера 10.2.

В корректоре порога 13.3 знак плюс или минус величины Δ Y п о р п формируется в зависимости от логического значения «единица» или «нуль», подаваемого на вход корректора порога 13.3 с выхода D-триггера 10.2.

Далее скорректированное значение величины порога принятия решения Y п о р к о р поступает на вход 14.4.2 вычитателя 14.4. На другой вход 14.4.1 вычитателя 14.4 поступает уровень напряжения Yпор, определяемый генератором константы 11. В вычитателе 14.4 происходит выделение величины Δ Y п о р п , которая поступает на последовательно соединенные нелинейный корректор 14.3 и корректор полярности 14.2, где величина приращения порога Δ Y п о р п возводится в квадрат ( Δ Y п о р п ) 2 и восстанавливается полярность после нелинейной коррекции. В корректоре полярности 14.2 знак плюс или минус величины ( Δ Y п о р п ) 2 формируется в зависимости от логического значения «единица» или «нуль», подаваемого на вход 14.2.1 с выхода D-триггера 10.2. В сумматоре 14.1 блока адаптации порога 14 величина уровня порога формируется как сумма значений Y п о р к о р = Y п о р + ( Δ Y п о р п ) 2 , поступающих соответственно с выхода генератора константы 11 на вход 14.1.1 и с выхода корректора полярности на вход 14.1.2.

Уровень напряжения Yпор выбирается равным абсолютному значению половины суммы амплитуд Uk и Ul и рассчитывается по формуле (Uk+Ul)/2.

С выхода D-триггера 10.2 демодулированный сигнал в виде импульсов, соответствующих логическим значениям «единица» и «нуль», поступает на выход устройства в соответствии с подачей тактовых импульсов с выхода 5.1.2 генератора тактовых импульсов 5 на вход 10.2.2 D-триггера 10.2, фиг.6д.

Если в момент воздействия тактового импульса на вход 10.2.2 соотношение амплитуд сигналов | p Y n | и Y п о р к о р будет соответствовать неравенству | p Y n | > Y п о р к о р , то с выхода компаратора напряжений 10.1 на вход 10.2.1 D-триггера 10.2 будет поступать высокий уровень напряжения, в результате чего в D-триггер 10.2 будет записан логический уровень «единица». В случае невыполнения неравенства | p Y n | > Y п о р к о р на выходе компаратора 10.1 будет низкий уровень напряжения, в результате чего в D-триггер 10.2 будет записан логический уровень значения «нуля».

На фиг.6 процесс демодуляции сигнала S(t) соответствует условию отсутствия ошибок в канале связи, вызванных воздействием помехи. В этом случае величина уровня порога решающего блока будет изменяться в зависимости от логического значения «единица» или «нуль» на выходе устройства, но при этом ошибки демодуляции возникать не будут.

При наличии помехи в канале связи, приводящей к ошибкам, связанным с преобладанием символов «единица» в выходной последовательности, на выходе коррелятора 3 в последовательности Y(t) появятся импульсные сигналы, значение которых будет не соответствовать истинной величине. На фиг.7а сигнал, вызванный помеховым импульсом, показан пунктиром. В результате на выходе блока стробирования 6 и на выходе ограничителя амплитуд 12, соответственно в последовательностях Yn и Yn-1, появятся импульсы, вызванные помехой, на фиг.7б и 7в такие импульсы названы помеховыми импульсами и выделены серым цветом. На выходе блока вычисления модуля 9 последовательность | p Y n | будет содержать два неправильно демодулированных импульса, на фиг.7г эти импульсы выделены темным цветом (четвертый и пятый импульс).

Если решение о демодулированном сигнале принимать в соответствии с правилом, предложенным в способе-прототипе, когда уровень | p Y n | сравнивается с уровнем Y п о р к о р = Y п о р + Δ Y п о р п , то в выходной последовательности импульсов на интервале Т5 будет принято решение о наличии логического значения «единица», что не соответствует истинным значениям (см. фиг.7д). В то же время, если решение принимать в соответствии с правилом, предложенным в заявляемом способе, когда уровень | p Y n | сравнивается с уровнем Y п о р к о р = Y п о р + ( Δ Y п о р п ) 2 , то в выходной последовательности импульсов нет неправильно принятых решений (см. фиг.7д), что указывает на повышение достоверности принятия решения о принятом символе в выходной последовательности демодулятора, достигаемого за счет изменения уровня напряжения порога по квадратическому закону, в зависимости от значений «единица» или «нуль», полученных на выходе решающего блока на предыдущих циклах.

При наличии помехи в канале связи, приводящей к ошибкам, связанным с преобладанием символов «нуль» в выходной последова