Устройство восстановления несущей частоты демодулятора сигналов с шестнадцатипозиционной амплитудно-фазовой манипуляцией

Иллюстрации

Показать всеИзобретение относится к области радиосвязи и может применяться в демодуляторах спутниковых систем связи, использующих сигналы с шестнадцатипозиционной амплитудно-фазовой манипуляцией (АФМ16). Технический результат - повышение точности слежения за несущей частотой. Устройство восстановления несущей частоты демодулятора сигналов с шестнадцатипозиционной амплитудно-фазовой манипуляцией содержит квадратурный перемножитель, блок вынесения решения о принимаемых информационных символах, формирователь сигнала ошибки, фильтр петли, интегратор и формирователь отсчетов синуса и косинуса, блок оценки математического ожидания ошибки по фазе и сумматор. 1 з.п. ф-лы, 9 ил.

Реферат

Изобретение относится к области радиосвязи и может применяться в демодуляторах спутниковых систем связи, использующих сигналы с шестнадцатипозиционной амплитудно-фазовой манипуляцией (АФМ16).

При работе спутниковых усилителей мощности в режиме насыщения используются сигналы с фазовой манипуляцией (ФМ4 и ФМ8), которые имеют постоянную огибающую. В тех случаях, когда есть значительный запас по мощности, спектральная эффективность может быть увеличена за счет использования сигналов с амплитудно-фазовой манипуляцией (АФМ16 и АФМ32), оптимизированных для работы с нелинейным передатчиком, и техники предыскажений.

В стандарте DVB-S2 [Digital Video Broadcasting (DVB); Second generation framing structure, channel coding and modulation systems for Broadcasting, Interactive Services, News Gathering and other broadband satellite applications. ETSI EN 302 307, v.1.1.2, (2006-06), 74 p.] точки сигнального созвездия для АФМ16 расположены на двух окружностях: 4 точки на внутренней окружности радиуса R1 и 12 точек на внешней окружности радиуса R2 (фиг.1). Отношение радиусов (γ=R2/R1) может принимать шесть значений в диапазоне от 2,57 до 3,15 в зависимости от скорости кодирования.

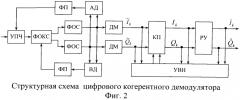

Структурная схема когерентного демодулятора сигналов с фазовой (ФМ), амплитудно-фазовой (АФМ) и квадратурной амплитудной (КАМ) модуляцией приведена на фиг.2. Здесь УПЧ - усилитель промежуточной частоты с регулируемым коэффициентом передачи, ФОКС - формирователь отсчетов квадратурных сигналов, ФОС - фильтр основной селекции, АД - амплитудный детектор устройства автоматической регулировки усиления, ВД -временной дискриминатор устройства тактовой синхронизации, ФП - фильтр петли, ДМ - демультиплексор, на выход которого проходит каждый второй отсчет сигнала, КП - квадратурный перемножитель, РУ - блок вынесения решения о принимаемых информационных символах, УВН - устройство восстановления несущей частоты.

В УПЧ осуществляется усиление и фильтрация сигнала. В ФОКС осуществляется перенос сигнала на видеочастоту с формированием синфазного и квадратурного сигналов, и их аналого-цифровое преобразование. Частота дискретизации сигналов равна удвоенной тактовой частоте входного сигнала f∂=2fm, что необходимо для работы ВД устройства тактовой синхронизации. С помощью КП (фиг.3) осуществляется поворот фазы комплексного сигнала I ˜ k + j ⋅ Q ˜ k , по значениям Ik и Qk принимается решение о координатах принимаемой точки сигнального созвездия I ⌢ k и Q ⌢ k в соответствии с фиг.1.

Устройства восстановления несущей частоты реализуются в виде петли фазовой автоподстройки частоты (ФАПЧ), т.е. содержат в своем составе фазовый детектор (ФД), фильтр петли (ФП) и генератор, управляемый напряжением (ГУН). В литературе описаны два алгоритма работы ФД.

В первом алгоритме фазовый детектор использует решения о принимаемых информационных символах (фиг.4) (см., например, [Lee E.A., Messerschmitt D.G. Digital communication. - Boston/Dordrecht/London: Kluver Academic Publishers, 1988, 713 p.], раздел 14.1). На фиг.4 комплексные сигналы обозначены жирной линией. Алгоритм работы формирователя сигнала ошибки (ФСО) описывается выражением

ε k = Q k ⋅ I ⌢ k − I k + j ⋅ Q ⌢ k . ( 1 )

Второй алгоритм предполагает наличие на входе нелинейного преобразователя, в котором осуществляется возведение входного сигнала в N-ю степень (см.и, например, [Lee E.A., Messerschmitt D.G. Digital communication. - Boston/Dordrecht/London: Kluver Academic Publishers, 1988, 713 p.], раздел 14.2). Обычно N=2 для сигналов ФМ2, N=4 для сигналов ФМ4 и КАМ. В спектре сигнала на выходе нелинейного преобразователя имеется дискретная спектральная составляющая на частоте N·fн, где fн - несущая частота сигнала. Слежение за этой составляющей осуществляется с помощью обычной (следящей за синусоидальным сигналом) петли ФАПЧ. Устройство восстановления несущей частоты в этом случае состоит из (фиг.5) последовательно соединенных блока возведения входного сигнала в N-ную степень ((·)N), вход которого соединен с входом устройства, квадратурного перемножителя (КП), блока взятия мнимой части от комплексного числа (Im{·}), фильтра петли (ФП) и генератора, управляемого напряжением (ГУН), выход которого соединен со вторым входом квадратурного перемножителя (КП).

Перечисленные выше варианты построения устройств восстановления несущей частоты имеют недостаточную точность при приеме АФМ сигналов.

Наиболее близким по технической сущности и достигаемому положительному эффекту, принятым за прототип, является устройство восстановления несущей частоты, которое реализует первый алгоритм работы фазового детектора и описано в [Lee E.A., Messerschmitt D.G. Digital communication. - Boston/Dordrecht/London: Kluver Academic Publishers, 1988, 713 p.], раздел 14.2.

На фиг.6 представлена структурная схема прототипа. Устройство содержит последовательно соединенные квадратурный перемножитель 1, первые два входа которого соединены с двумя входами устройства, блок вынесения решения о принимаемых информационных символах 2, два выхода которого соединены с двумя выходами устройства, формирователь сигнала ошибки 3, вторые два входа которого соединены с двумя выходами квадратурного перемножителя 1, фильтр петли 4, интегратор 5 и формирователь отсчетов синуса и косинуса 6, два выхода которого соединены со вторыми двумя входами квадратурного перемножителя 1.

Устройство работает следующим образом. На первые два входа квадратурного перемножителя 1 поступают отсчеты синфазного I ˜ k и квадратурного Q ˜ k сигналов. На вторые два входа квадратурного перемножителя 1 с формирователя отсчетов синуса и косинуса 6 поступают отсчеты синуса и косинуса оценки фазы ϕk несущей частоты сигналов, которая формируется на выходе интегратора 5. На выходе квадратурного перемножителя 1 в результате перемножения комплексных I ˜ k + j ⋅ Q ˜ k и sin(ϕk)+j·cos(ϕk) формируется комплексный сигнал Ik+j·Qk, который повернут по фазе относительно входного комплексного сигнала на угол ϕk. В блоке вынесения решения о принимаемых информационных символах 2 выносится решение о значениях координат точки сигнального созвездия I ⌢ k и Q ⌢ k (одно из восьми возможных, в соответствии с фиг.1). На выходе формирователя сигнала ошибки 3 формируется сигнал ошибки εk в соответствии с выражением (1). Этот сигнал фильтруется в фильтре петли 4 и поступает на вход генератора, управляемого напряжением, который реализован в виде последовательного соединения интегратора 5 и формирователя отсчетов синуса и косинуса 6.

Описанный выше алгоритм работы устройства восстановления несущей частоты широко используется при приеме ФМ и КАМ сигналов.

Недостатком описанного устройства является его низкая точность при приеме АФМ сигналов.

Цель изобретения - повышение точности слежения устройства.

Поставленная цель достигается тем, что в устройство восстановления несущей частоты, содержащее последовательно соединенные квадратурный перемножитель, первые два входа которого соединены с двумя входами устройства, блок вынесения решения о принимаемых информационных символах, два выхода которого соединены с двумя выходами устройства, формирователь сигнала ошибки, вторые два входа которого соединены с двумя выходами квадратурного перемножителя, фильтр петли, интегратор и формирователь отсчетов синуса и косинуса, два выхода которого соединены со вторыми двумя входами квадратурного перемножителя, введены последовательно соединенные блок оценки математического ожидания ошибки по фазе, первые два входа которого соединены с выходами блока вынесения решения о принимаемых символах, третий вход - с выходом формирователя сигнала ошибки, и сумматор, который включен в разрыв между интегратором и формирователем отсчетов синуса и косинуса, т.е. второй вход сумматора соединен с выходом интегратора, а его выход - с входом формирователя отсчетов синуса и косинуса, а блок оценки математического ожидания ошибки по фазе состоит из последовательно соединенных амплитудного детектора, два входа которого соединены с двумя выходами блока вынесения решения о принимаемых информационных символах, компаратора, интегратора со сбросом, второй вход которого соединен с выходом формирователя сигнала ошибки, и блока вынесения решения об ошибке, а также содержит формирователь временного интервала, первый выход которого соединен со вторым входом блока вынесения решения об ошибке, а второй выход - с третьим входом интегратора со сбросом.

Анализ существенных отличий, указанных в отличительной части формулы изобретения, показывает, что блок оценки математического ожидания ошибки по фазе и сумматор не используются в прототипе.

Фиг.1. Сигнальное созвездие для АФМ16.

Фиг.2. Структурная схема цифрового когерентного демодулятора.

Фиг.3. Структурная схема квадратурного перемножителя.

Фиг.4. Структурная схема устройства восстановления несущей частоты.

Фиг.5. Структурная схема устройства восстановления несущей частоты.

Фиг.6. Структурная схема устройства восстановления несущей частоты (прототипа).

Фиг.7. Структурная схема устройства восстановления несущей частоты (заявляемого устройства).

Фиг.8. Структурная схема блока оценки математического ожидания ошибки по фазе (заявляемого устройства).

Фиг.9. Фазовые портреты сигналов на входе решающего устройства.

Предлагаемое устройство изображено на фиг.7. Устройство содержит последовательно соединенные квадратурный перемножитель 1, первые два входа которого соединены с двумя входами устройства, блок вынесения решения о принимаемых информационных символах 2, два выхода которого соединены с двумя выходами устройства, формирователь сигнала ошибки 3, вторые два входа которого соединены с двумя выходами квадратурного перемножителя 1, фильтр петли 4, интегратор 5, сумматор 8 и формирователь отсчетов синуса и косинуса 6, два выхода которого соединены со вторыми двумя входами квадратурного перемножителя 1, а также блок оценки математического ожидания ошибки по фазе 7, первые два входа которого соединены с выходами блока вынесения решения о принимаемых информационных символах 2, третий вход - с выходом формирователя сигнала ошибки 3, а выход - со вторым входом сумматора 8.

Устройство работает следующим образом. На первые два входа квадратурного перемножителя 1 поступают отсчеты синфазного I ˜ k и квадратурного Q ˜ k сигналов. На вторые два входа квадратурного перемножителя 1 с формирователя отсчетов синуса и косинуса 6 поступают отсчеты синуса и косинуса оценки фазы θk=ϕk-Δϕk несущей частоты сигналов. Значение ϕk формируется на выходе интегратора 5. Значение Δϕk формируется на выходе блока оценки математического ожидания ошибки по фазе 7. На выходе квадратурного перемножителя 1 в результате перемножения комплексных сигналов I ˜ k + j ⋅ Q ˜ k и sin(θk)+j·cos(θk) формируется комплексный сигнал Ik+j·Qk, который повернут по фазе относительно входного комплексного сигнала на угол θk. В блоке вынесения решения о принимаемых информационных символах 2 выносится решение о значениях координат точки сигнального созвездия I ⌢ k и Q ⌢ k (одно из восьми возможных, в соответствии с фиг.1). На выходе формирователя сигнала ошибки 3 формируется сигнал ошибки εk в соответствии с выражением (1). Этот сигнал фильтруется в фильтре петли 4 и поступает на вход интегратора 5.

Блок оценки математического ожидания ошибки по фазе 7 изображен на фиг.8 и состоит из последовательно соединенных амплитудного детектора 9, два входа которого соединены с двумя выходами блока вынесения решения о принимаемых информационных символах 2, компаратора 10, интегратора со сбросом 11, второй вход которого соединен с выходом формирователя сигнала ошибки 3, и блока вынесения решения об ошибке 12, а также содержит формирователь временного интервала 13, первый выход которого соединен со вторым входом блока вынесения решения об ошибке 12, а второй выход - с третьим входом интегратора со сбросом 11.

Ошибка по фазе в прототипе устройства восстановления несущей частоты при приеме сигналов АФМ16 может принимать одно из трех значений: 0, минус π/12 или плюс π/12 (см. фазовые портреты на фиг.9а, 9б и 9в). Из этих же фазовых портретов следует, что оценку математического ожидания ошибки по фазе можно получить, используя только те точки сигнального созвездия, которые лежат на внутренней окружности. Для принятия решения о том, что точка сигнального созвездия находится на внутренней окружности, в устройстве используются амплитудный детектор 9 и компаратор 10 (см. фиг.8). Блок оценки математического ожидания ошибки по фазе работает следующим образом. На два входа амплитудного детектора 9 поступают решения о значениях координат текущей точки сигнального созвездия I ⌢ k и Q ⌢ k . Амплитуда сигнала A k = I ⌢ k 2 + Q ⌢ k 2 в компараторе 10 сравнивается с порогом, в результате принимается решение о принадлежности точки сигнального созвездия внутренней или внешней окружности. В интеграторе со сбросом 11 к сигналу на его выходе добавляется сигнал ошибки εk, при условии что текущая точка сигнального созвездия принадлежит внутренней окружности. На выходе формирователя временного интервала 13 формируются два импульса, следующих один за другим. В интервале между этими импульсами осуществляется накопление сигнала ошибки εk. Первый импульс определяет момент вынесения решения об ошибке: 0, минус π/12 или плюс π/12 в блоке вынесения решения об ошибке 12, а вторым импульсом осуществляется сброс интегратора со сбросом 11.

Техническое преимущество заявляемого устройства заключается в том, что оно за счет введения блока оценки математического ожидания ошибки по фазе и сумматора позволяет повысить его точность, и тем самым уменьшить энергетические потери при демодуляции. Докажем это.

Прототип устройства восстановления несущей частоты при приеме сигналов АФМ16 имеет три точки устойчивого равновесия, которым соответствуют ошибки по фазе: 0, минус π/12 или плюс π/12 (см. фазовые портреты, приведенные на фиг.9а, 9б и 9в). Указанные фазовые портреты и оценки отношения сигнал/шум на входе блока вынесения решения о принимаемых информационных символах получены методом компьютерного моделирования рассматриваемой системы связи и соответствуют отношению сигнал/шум на входе демодулятора Еб/N0, равному 20 дБ, где Еб - энергия сигнала, приходящаяся на бит информации, N0 - спектральная плотность мощности аддитивного гауссовского шума. Из-за неидеальности работы демодулятора и, в частности, из-за ошибок работы устройства восстановления несущей частоты отношение сигнал/шум на входе блока вынесения решения о принимаемых информационных символах оказывается меньше отношения сигнал/шум на входе демодулятора Еб/N0. Разность между двумя этими значениями отношения сигнал/шум принято называть энергетическими потерями. Из фиг.9а, 9б и 9в следует, что энергетические потери демодулятора при нулевой фазовой ошибке составляют 1,2 дБ, а при ошибках минус π/12 и плюс π/12 - 8 дБ. Эксперимент показывает, что возможные значения фазовой ошибки равновероятны, при этом средние энергетические потери составляют примерно 5,7 дБ. Исключить ошибки по фазе ±π/12 можно, если в ФСО использовать только те точки сигнального созвездия, которые лежат на внутренней окружности, однако при этом увеличивается шумовая составляющая ошибки. В этом случае энергетические потери составляют 4,4 дБ (см. фиг.9г). При использовании в демодуляторе заявляемого устройства его работа осуществляется по всем точкам сигнального созвездия, а ошибки по фазе ±π/12 отсутствуют, следовательно, точность слежения повышается. При этом энергетические потери составляют 1,2 дБ (см. фиг.9а), что на 4,5 дБ меньше по сравнению с тем случаем, когда в демодуляторе используется прототип.

1. Устройство восстановления несущей частоты демодулятора сигналов с шестнадцатипозиционной амплитудно-фазовой манипуляцией, содержащее последовательно соединенные квадратурный перемножитель, первые два входа которого соединены с двумя входами устройства, блок вынесения решения о принимаемых информационных символах, два выхода которого соединены с двумя выходами устройства, формирователь сигнала ошибки, вторые два входа которого соединены с двумя выходами квадратурного перемножителя, фильтр петли, интегратор и формирователь отсчетов синуса и косинуса, два выхода которого соединены со вторыми двумя входами квадратурного перемножителя, отличающееся тем, что введены последовательно соединенные блок оценки математического ожидания ошибки по фазе, первые два входа которого соединены с выходами блока вынесения решения о принимаемых информационных символах, третий вход - с выходом формирователя сигнала ошибки, и сумматор, который включен в разрыв между интегратором и формирователем отсчетов синуса и косинуса, т.е. второй вход сумматора соединен с выходом интегратора, а его выход - с входом формирователя отсчетов синуса и косинуса.

2. Устройство восстановления несущей частоты по п.1, отличающееся тем, что блок оценки математического ожидания ошибки по фазе состоит из последовательно соединенных амплитудного детектора, два входа которого соединены с двумя выходами блока вынесения решения о принимаемых информационных символах, компаратора, интегратора со сбросом, второй вход которого соединен с выходом формирователя сигнала ошибки, и блока вынесения решения об ошибке, а также содержит формирователь временного интервала, первый выход которого соединен со вторым входом блока вынесения решения об ошибке, а второй выход - с третьим входом интегратора со сбросом.