Мультиконтроллер распределяемой памяти

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники. Технический результат заключается в обеспечении автономного произвольного доступа к памяти без использования дополнительных ресурсов. Указанный технический результат достигается за счет более сложной организации внутренней памяти, а именно в разделении ее на три независимых блока, использования в предлагаемом изобретении арифметико-логического устройства для выполнения арифметических действий над параметрами операторов, оптимизации связей между различными блоками для более рационального перемещения параметров, расширения системы команд. 11 ил., 4 табл.

Реферат

Предполагаемое изобретение относится к области вычислительной техники и может найти применение в конвейерных потоковых машинах и многопроцессорных вычислительных системах.

Известно устройство доступа к памяти в процессоре ADSP-TS203S (см. http://www.analog.com/static/imported-files/data_sheets/ADSP-TS203S.pdf). Система обращения к памяти, принятая для архитектуры процессора ADSP-TS203S, содержит два адресных генератора, состоящих из целочисленных АЛУ и регистровых файлов; логику статического предсказания переходов, буфер адресов переходов и внутреннюю память DRAM. АЛУ используются для адресации данных, вычисления значений указателей, а также для выполнения простых вычислительных операций с целыми числами. Внутренняя память DRAM разбита на 4 независимых блока, предназначенных для хранения как инструкций, так и данных. Каждый блок внутренней памяти имеет собственный кэш. Имеется выход на контроллер внешней памяти SDRAM. Устройство доступа к памяти позволяет осуществлять сложные процедуры обращения как к внутренней, так и к внешней памяти.

Недостатком данного устройства является то, что оно не может быть использовано самостоятельно (без дополнительных средств) для организации доступа к памяти.

Причина недостатка состоит в том, что устройство доступа к памяти является составной частью процессора ADSP-TS203S.

Наиболее близким к предполагаемому изобретению является мультиконтроллер распределенной памяти (патент на изобретение №2210804) содержащий память программ, устройство управления, регистр операторов, счетчик условий, счетчик возврата, два регистровых файла начальных адресов и адресных приращений. В состав прототипа также входят сумматоры текущего адреса, адреса пороговой адресации и модифицируемых полей оператора, а также ортогональная регистровая память и вспомогательные мультиплексоры и счетчики.

Данное устройство позволяет обеспечивать автономный произвольный доступ к памяти по нескольким параллельным каналам без использования дополнительных ресурсов, в том числе, процессора. Порядок доступа к памяти строго регламентирован. Он описывается программой, хранящейся в памяти программ устройства и не требует механизма запросов от процессора. Поддерживается процедура изменения адресов каналов, заключающаяся в увеличении (уменьшении) адреса по каждому каналу на некоторый адресный параметр (приращение), а также более сложная процедура пороговой адресации. Кроме того, имеется возможность для модификации начальных адресов доступа и адресных приращений, а также средства для организации вложенных циклов, что позволяет организовывать сложные процедуры обращения к памяти.

Заявляемое устройство является результатом модификации описанного выше мультиконтроллера распределенной памяти с целью расширения возможностей программирования и повышения быстродействия. Рассмотрим преимущества заявляемого устройства перед своим прототипом.

В прототипе константа цикла указывается непосредственно в поле оператора, то есть используется непосредственная адресация. Число значений операндов при этом ограничивается разрядностью поля. В заявляемом устройстве используется прямая адресация, когда в соответствующем поле оператора указывается полный адрес константы цикла. Это дает возможность увеличить разрядность данного операнда. Кроме того, расширяются возможности программирования, так как значение параметра может изменяться при неизменной исполняемой программе.

В прототипе операторы и их параметры, такие как начальный адрес и адресное приращение, хранятся в одной памяти программ параметров. В заявляемом устройстве используется три независимых блока памяти для операторов, параметров адресации и констант цикла соответственно. Каждый блок памяти реализован в виде двухпортовой статической памяти. Такое решение обеспечивает более быстрый доступ к требуемым операндам.

В заявляемом устройстве счетчик возврата, используемый в прототипе, был заменен на стек глубиной 64 слова. Это позволяет организовывать подпрограммы большей вложенности.

В заявляемом устройстве было добавлено четыре регистра общего назначения.

Были расширены возможности пересчета полей операторов и параметров. В прототипе для модификации полей оператора использовалась только операция сложения. В заявляемом устройстве добавлены операции обнуления и замещения полей оператора. В прототипе для пересчета параметров оператора были доступны операции сложения и перемещения. В заявляемом устройстве были добавлены операции вычитания, умножения и деления параметров, а также существенно увеличен список операторов перемещения параметров между блоками памяти напрямую и между регистрами.

Был добавлен регистр сегмента для осуществления сегментной адресации памяти.

Задача на решение которой направлено заявляемое изобретение, заключается в расширении функциональных возможностей, обеспечении автономного произвольного доступа к памяти без использования дополнительных ресурсов, в том числе, процессора.

Технический результат, достигаемый при осуществлении изобретения, состоит в том, что расширение функциональных возможностей достигается за счет более сложной организации внутренней памяти, а именно, в разделении ее на три независимых блока, перехода от непосредственной к прямой адресации для константы цикла, перехода от счетчика возврата к стеку адресов возврата, использования в изобретении арифметико-логического устройства для выполнения арифметических действий над параметрами операторов, а именно, сложения, вычитания, умножения и деления, добавления быстродействующих регистров общего назначения, оптимизации связей между различными блоками изобретения для более рационального перемещения параметров, расширения системы команд.

Для достижения указанного технического результата заявляемое устройство содержит устройство управления, блок памяти операторов, блок памяти параметров, блок памяти циклов, блок основного мультиплексора, устройство арифметическое, процессор адресный, причем вход управляющего сигнала устройства соединен с первым входом устройства управления, двунаправленный вывод которого соединен с двунаправленными выводами блоков памяти операторов, памяти параметров, памяти циклов, процессора адресного, устройства арифметического и блока основного мультиплексора, выход которого соединен с первыми входами блоков памяти операторов, памяти параметров, памяти циклов и процессора адресного, второй вход которого соединен с первым входом устройства арифметического и с первым выходом блока памяти параметров, второй выход которого соединен с третьим входом процессора адресного, вторым входом устройства арифметического, первым входом блока основного мультиплексора и вторым входом блока памяти оператора, первый выход которого разрядами поля V1 связан соответственно с второго по шестой входами устройства управления, разрядами полей V2, V3 с вторым входом блока памяти параметров и разрядами полей V2, V3, V4 с вторым входом блока памяти циклов, третий вход которого соединен с третьим входом блока памяти параметров и выходом устройства арифметического, четвертый вход процессора адресного соединен с первым выходом блока памяти циклов, второй выход которого соединен с третьим входом устройства арифметического, четвертый вход которого соединен с третьим выходом блока памяти циклов и вторым входом блока основного мультиплексора, третий вход которого соединен с вторым выходом блока памяти операторов, с первого по четвертый выходы процессора адресного соединены соответственно с четвертого по седьмой входами блока основного мультиплексора, второй выход устройства управления соединен с первым выходом устройства, с второго по восьмой входы которого соединены соответственно с пятого по одиннадцатый входами процессора адресного, с пятого по одиннадцатый выходы которого соединены соответственно с второго по восьмой выходами устройства.

Причинно-следственная связь между совокупностью существенных признаков заявляемого изобретения и достигаемым техническим результатом заключается в следующем: введение в устройство прямой адресации константы цикла, переход от регистра возврата к стеку, добавление регистров общего назначения, добавление арифметико-логического устройства для модификации параметров и добавление новых операторов расширяют возможности программирования. Добавление трех независимых блоков памяти для операторов, параметров адресации и констант цикла, а также оптимизация связей между отдельными блоками позволяет реализовать процедуру обращения к памяти на более высокой тактовой частоте по сравнению с прототипом.

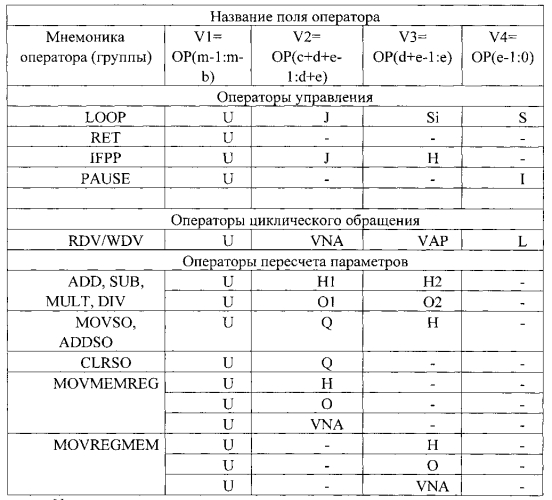

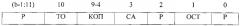

Изобретение поясняется чертежами, где на фиг. 1 представлена схема устройства мультиконтроллер распределяемой памяти (DMC), на фиг. 2 (Л. 1, Л. 2) - устройство управления (CTRL), на фиг. 3-блок основного мультиплексора (GMUX), на фиг. 4 (Л. 1, Л. 2) - блок памяти операторов (SO), на фиг. 5 - блок памяти параметров (SP), на фиг. 6 - блок памяти циклов (SC), на фиг. 7 - устройство арифметическое (ALU), на фиг. 8 (Л. 1, Л. 2) - процессор адресный (АР).

Устройство содержит вход 1 - вход поступления управляющего сигнала PUSK; вы ход 2 - выход статусного сигнала STOP; устройство 3 управления; блок 4 памяти операторов; блок 5 памяти параметров; блок 6 памяти циклов; блок 7 основного мультиплексора, устройство 8 арифметическое; процессор 9 адресный; вход 10 - вход маркера данных от контроллера внешней памяти данных MDI_M; вход 11 - вход данных от контроллера внешней памяти данных DI_M; вход 12 - сигнал LAST_CMD, подтверждающий выполнение контроллером внешней памяти всех запросов; вход 13 - сигнал LAST_DAT, подтверждающий поступление от контроллера внешней памяти последнего данного; вход 14 - сигнал переполнения контроллера внешней памяти OVFL_M; вход 15 - вход маркера данных от вычислительной схемы MDI_U; вход 16 - вход данных от вычислительной схемы DI_U; выход 17 - выход маркера адреса МА_M для контроллера внешней памяти; выход 18 - выход адреса A_M для контроллера внешней памяти; выход 19 - выход маркера данных MDO_M для контроллера внешней памяти; выход 20 - выход данных DO_M для контроллера внешней памяти; выход 21 - выход последнего запроса для контроллера внешней памяти LOP_M; выход 22 - выход маркера данных для вычислительной схемы MDO_U; выход 23 - выход данных для вычислительной схемы DO_U.

Устройство 3 управления (фиг. 2 Л1, Л2) содержит четыре элемента И24, 26, 33.1, 33.2 четыре триггера FD25, 28, 30, 54, сдвиговый регистр SRG31, три дешифратора DC32, 34, 36, сорок элементов ИЛИ27, 29, 35.1-35.3, 37-53, 55-72.

Блок 7 основного мультиплексора (фиг. 3) содержит восемь элементов И73, 75, 77, 79, 86, 89-91, семь элементов ИЛИ81-85, 87, 92, четыре регистра REG74, 76, 78, 80, триггер FD88, мультиплексор МХ93.

Блок 4 памяти операторов (фиг. 4 Л1, Л2) содержит двадцать два элемента И94.1-94.3, 98, 101-103, 106, 112, 114, 117, 119, 123, 125, 129, 131, 135, 137, 138, 142-144, пять элементов ИЛИ95, 104, 105, 139, 145, четыре инвертора НЕ115, 121, 127, 133, два мультиплексора МХ96, 107, два блока памяти RAM100, ПО, пять триггеров FD97, 99, 108, 140, 141, счетчик СТ109, девять регистров REG111, 113, 116, 120, 122, 126, 128, 132, 134, четыре сумматора ADD118, 124, 130, 136.

Блок 5 памяти параметров (фиг. 5) содержит семь элементов И146, 149, 150, 158, 160-162, три элемента ИЛИ147, 151, 163, мультиплексор МХ152, блок памяти RAM155, триггер FD153, четыре регистра REG148, 154, 156, 157, компаратор 159.

Блок 6 памяти циклов (фиг. 6) содержит девять элементов И164, 167, 172, 175, 195, 196, 186, 190, 192, пять элементов ИЛИ165, 169, 173, 181, 197, три мультиплексора МХ166, 170, 178, три триггера FD171, 179, 187, счетчик СТ188, блок памяти RAM 180, четыре регистра REGI74, 182-184, три компаратора 185, 189, 191, вычитатель 193.

Устройство 8 арифметическое (фиг. 7) содержит три мультиплексора МХ198, 199, 207, три элемента И200, 202, 204, два элемента ИЛИ206, 208, умножитель MULT201, сумматор-вычитатель 203, делитель DIV205.

Процессор 9 адресный (фиг. 8 Л1, Л2) содержит четырнадцать элементов И209, 218, 220, 229, 232, 234, 243, 244, 250, 254, 261, 265-267, одиннадцать элементов ИЛИ214, 215, 225, 226, 235, 238, 240, 245, 247, 258, 268, семь регистров REG210-212, 219, 221, 269, 271, восемнадцать триггеров FD217, 230, 231, 233, 236, 237, 239, 241, 242, 246, 255-257, 259, 262, 263, 270, 272, три мультиплексорами 13, 227, 264, три сумматора 216, 223, 228, вычитатель 222, три компаратора 224, 249, 253, элемент XOR251, два счетчика СТ248, 252, блок памяти FIFO260.

Вход 1 управляющего сигнала PUSK устройства (фиг. 1) соединен с первым входом устройства 3 управления, двунаправленный вывод CTRL которого соединен с двунаправленными выводами CTRL блоков 4 памяти операторов, 5 памяти параметров, 6 памяти циклов, процессора 9 адресного, устройства 8 арифметического и блока 7 основного мультиплексора, выход GB которого соединен с первыми входами GB блоков 4 памяти операторов, 5 памяти параметров, 6 памяти циклов и процессора 9 адресного, второй вход SPA которого соединен с первым входом устройства 8 арифметического и с первым выходом SPA блока 5 памяти параметров, второй выход SPB которого соединен с третьим входом процессора 9 адресного, вторым входом устройства 8 арифметического, первым входом блока 7 основного мультиплексора и вторым входом блока 4 памяти оператора, первый выход OP которого разрядами поля VI связан соответственно с второго по шестой входами устройства 3 управления, разрядами полей V2, V3 с вторым входом ОР блока 5 памяти параметров и разрядами полей V2, V3, V4 с вторым входом ОР блока 6 памяти циклов, третий вход ALU которого соединен с третьим входом блока 5 памяти параметров и выходом ALU устройства 8 арифметического, четвертый вход SCA1 процессора 9 адресного соединен с первым выходом блока 6 памяти циклов, второй выход SCA2 которого соединен с третьим входом устройства 8 арифметического, четвертый вход SCB которого соединен с третьим выходом SCB блока 6 памяти циклов и вторым входом блока 7 основного мультиплексора, третий вход SS которого соединен с вторым выходом SS блока 4 памяти операторов, с первого по четвертый выходы SD, SEG, BASA и MOD процессора 9 адресного соединены соответственно с четвертого по седьмой входами блока 7 основного мультиплексора, второй выход STOP устройства 3 управления соединен с первым выходом 2 устройства, с второго по восьмой входы 10÷16 которого соединены соответственно с пятого по одиннадцатый входами процессора 9 адресного, с пятого по одиннадцатый выходы которого соединены соответственно с второго по восьмой выходами 17÷23 устройства.

Первый вход PUSK устройства 3 управления (фиг. 2 Л1, Л2) соединен с первым входом элемента ИЛИ27, второй вход которого соединен с выходом элемента И26, первый вход которого соединен с вторым входом LST устройства управления и первым входом элемента И24, второй вход которого соединен с вторым входом элемента И26, выходом триггера FD30, входами сброса сдвигового регистра SRG31, дешифраторов DC36, DC34 и выходом GEND двунаправленного вывода CTRL, выход элемента И24 соединен с входом триггера FD25, выход которого соединен с выходом статусного сигнала STOP устройства управления, выход триггера FD28 соединен с выходом INSTR двунаправленного вывода CTRL и информационным входом сдвигового регистра SRG31, выходы с первого Q1 по двенадцатый Q12 которого соединены соответственно с выходами Τ1÷T12 двунаправленного вывода CTRL, выход Q3 регистра SRG31 соединен с управляющим входом дешифратора DC32, первый и второй информационные входы которого соединены соответственно с третьим и четвертым входами MPO, MPI устройства управления, с первый по четвертый выходы дешифратора DC32 соединены соответственно с выходами MODV1÷MODV4 двунаправленного вывода CTRL, вход триггера FD30 соединен с выходом элемента ИЛИ29, с первого по пятый входы которого соединены соответственно с входами END_AP÷END_GMUX двунаправленного вывода CTRL, пятый вход СОР устройства управления восемью битами соединен с информационным входом дешифратора DC36 и двумя битами СОР(3:2) с информационным входом дешифратора DC34, управляющий вход которого соединен с выходом элемента И33.2, выход элемента И33.1 соединен с управляющим входом дешифратора DC36, шестой вход ТО устройства управления соединен с первыми входами элементов И33.1, И33.2, вторые входы которых соединены с входом Т4 двунаправленного вывода CTRL, выход QM2 дешифратора DC34 соединен с первыми входами элементов ИЛИ35.1, ИЛИ35.2, первый вход элемента ИЛИ35.3 соединен с выходом QM1 дешифратора DC34, выход QM3 которого соединен с вторыми входами элементов ИЛИ35.1, ИЛИ35.3, второй вход элемента ИЛИ35.2 соединен с выходом QM0 дешифратора DC34, выходы элементов ИЛИ35.1, ИЛИ35.2, ИЛИ35.3 соединены соответственно с выходами PA, OP_RD, OP_WR двунаправленного вывода CTRL, выходы Q33, Q59, Q157 дешифратора DC36 соединены соответственно с первого по третий входами элемента ИЛИ37, выход которого соединен с выходом MOVSSXX двунаправленного вывода CTRL, выход LOOP которого соединен с выходом элемента ИЛИ38, входы которого соединены с выходами Q8, Q10 дешифратора DC36, выходы Q12, Q14 которого соединены с входами элемента ИЛИ39, выход которого соединен с выходом IFPP двунаправленного вывода CTRL, выход ADDO_MOVO которого соединен с выходом элемента ИЛИ40, входы которого соединены с выходами Q3, Q4 дешифратора DC36, выходы Q9, Q8, Q12, Q4, Q6 которого соединены соответственно с выходами RET, LOOP_CALL, IFPP_CALL, MOVO, CLRO двунаправленного вывода CTRL, выходы Q57, Q84, Q85, Q87÷Q91, Q93, Q161 дешифратора DC36 соединены соответственно с входами элемента ИЛИ41, выход которого соединен с выходом MOVSPXX двунаправленного вывода CTRL, выход ARITHM_SP которого соединен с выходом элемента ИЛИ42, входы которого соединены соответственно с выходами Q0, Q1, Q188, Q190, Q192 дешифратора DC36, выходы Q83, Q21, Q81 которого соединены соответственно с выходами MOVSPSD, PAUSE, MOVSCSD двунаправленного вывода CTRL, выход MOVSCXX которого соединен с выходом элемента ИЛИ43, входы с первого по десятый которого соединены соответственно с выходами Q55, Q159, Q162, Q163, Q165-Q169, Q171 дешифратора DC36, выходы Q2, Q7, Q189, Q191, Q193 которого соединены соответственно с первого по пятый входы элемента ИЛИ44, выход которого соединен с выходом ARITHM_SC двунаправленного вывода CTRL устройства управления, выход OP_MULT которого соединен с выходом элемента ИЛИ45, входы которого соединены с выходами Q192, Q193 дешифратора DC36, выходы Q7, Q0 которого соединены с входами элемента ИЛИ46, выход которого соединен с выходом OP ADD двунаправленного вывода CTRL, выход OP_ASUB которого соединен с выходом элемента ИЛИ47, входы с первого по четвертый которого соединены с выходами Q0-Q2, Q7 дешифратора DC36, выходы Q188, Q189 которого соединены с входами элемента ИЛИ48, выход которого соединен с выходом OP_DIV двунаправленного вывода CTRL, выход DIV_FRACT которого соединен с выходом элемента ИЛИ49, входы которого соединены с выходами Q190, Q191 дешифратора DC36, выходы Q39, Q65, Q143 которого соединены с входами элемента ИЛИ50, выход которого соединен с выходом MOVSEGXX двунаправленного вывода CTRL, выход MOVBASXX которого соединен с выходом элементом ИЛИ51, входы которого соединены с выходами Q32, Q58, Q136 дешифратора DC36, выходы Q41, Q67, Q144 которого соединены с входами элемента ИЛИ52, выход которого соединен с выходом MOVMODXX двунаправленного вывода CTRL, выход MOVSD_WR двунаправленного вывода CTRL устройства управления (Л2) соединен с выходом элемента ИЛИ53, входы с первого по десятый которого соединены с выходами QUO, QUI, Q113÷Q117, Q119, Q56, Q160 дешифратора DC36, одиннадцатый вход элемента ИЛИ53 соединен с выходом триггера FD54, информационный вход которого соединен с выходом Q82 дешифратора DC36, управляющий вход и вход сброса триггера FD54 соединены соответственно с входами VALID_SD и GEND двунаправленного вывода CTRL, выходы Q58, Q59, Q61÷Q65, Q67 дешифратора DC36 соединены соответственно с входами с первого по восьмой элемента ИЛИ55, выход которого соединен с выходом MOVRGSD двунаправленного вывода CTRL и первым входом элемента ИЛИ56, входы со второго по четвертый которого соединены соответственно с выходами Q81-Q83 дешифратора DC36, выход элемента ИЛИ56 соединен с выходом MOVSD_RD двунаправленного вывода CTRL, выходы MOVRON1XX, MOVRON2XX, MOVRON3XX, MOVRON4XX, MOVXXMOD, MOVXXSS которого соединены соответственно с выходами элементов ИЛИ57-ИЛИ62, входы элемента ИЛИ57 соединены соответственно с выходами Q35, Q61, Q139 дешифратора DC36, выходы Q36, Q62, Q140 которого соединены с входами элемента ИЛИ58, входы элемента ИЛИ59 соединены с выходами Q37, Q63, Q141 дешифратора DC36, выходы Q38, Q64, Q142 которого соединены с входами элемента ИЛИ60, входы элемента ИЛИ61 соединены с выходами Q93, Q119, Q171 дешифратора DC36, выходы Q85, Q111, Q163 которого соединены с входами элемента ИЛИ62, выходы MOVXXRON1, MOVXXRON2, MOVXXRON3, MOVXXRON4, MOVXXSEG, MOVXXBAS двунаправленного вывода CTRL соединены соответственно с выходами элементов ИЛИ63÷ИЛИ68, входы элемента ИЛИ63 соединены с выходами Q87, Q113, Q165 дешифратора DC36, выходы Q88, Q114, Q166 которого соединены с входами элемента ИЛИ64, входы элемента ИЛИ65 соединены с выходами Q89, Q115, Q167 дешифратора DC36, выходы Q90, Q116, Q168 которого соединены с входами элемента ИЛИ66, входы элемента ИЛИ67 соединены с выходами Q91, Q117, Q169 дешифратора DC36, выходы которого Q84, QUO, Q162 соединены с входами элемента ИЛИ68, выходы дешифратора Q32, Q33, Q35÷Q39, Q41 соединены с входами элемента ИЛИ69, выход которого соединен с выходом MOVRGSP двунаправленного вывода CTRL и первым входом элемента ИЛИ70, входы с второго по четвертый которого соединены соответственно с выходами Q55÷Q57 дешифратора DC36, выход элемента ИЛИ70 соединен с выходом MOVXXSP двунаправленного вывода CTRL, выходы дешифратора Q136, Q137, Q139÷Q144 соединены с входами элемента ИЛИ71, выход которого соединен с выходом MOVRGSC двунаправленного вывода CTRL и первым входом элемента ИЛИ72, входы с второго по четвертый которого соединены с выходами Q159÷Q161 дешифратора DC36, выход элемента ИЛИ72 соединен с выходом MOVXXSC двунаправленного вывода CTRL.

С первого BASA по седьмой SD входы блока 7 основного мультиплексора (фиг. 3) соединены соответственно с первого DO по седьмой D6 информационными входами мультиплексора МХ93, с восьмого D7 по одиннадцатый D10, информационные входы которого соединены соответственно с выходами регистров REG74, REG76, REG78, REG80, выходы элементов ИЛИ81÷ИЛИ84 соединены соответственно с адресными входами мультиплексора МХ93, выход которого соединен с выходом GB блока и с информационными входами регистров REG74, REG76, REG78, REG80, управляющие входы которых соединены соответственно с выходами элементов И73, И75, И77, И79, первые входы которых соединены с входом GBH двунаправленного вывода CTRL, входы MOVRON1XX÷MOVRON4XX соединены соответственно с вторыми входами элементов И73, И75, И77, И79, выход элемента ИЛИ87 соединен с управляющим входом мультиплексора МХ93 и входом триггера FD88, выход которого соединен с выходом GBM двунаправленного вывода CTRL, входы VALID_SD и Т7 которого соединены соответственно с первыми входами элементов ИЛИ87 и И86, выход элемента И86 соединен с вторым входом элемента ИЛИ 87, второй вход элемента И86 соединен с выходом элемента ИЛИ85, входы с первого по десятый которого соединены соответственно с входами MOVXXMOD, MOVXXSC, MOVXXSEG, MOVXXSS, MOVXXSP, MOVXXRON1÷MOVXXRON4, MOVXXBAS двунаправленного вывода CTRL, входы MOVXXMOD, VALID_SD, MOVXXSS, MOVXXRON1, MOVXXRON3 которого соединены с входами элемента ИЛИ81, входы элемента ИЛИ82 соединены с входами MOVXXSEG, MOVXXSP, VALID SD, MOVXXRON1, MOVXXRON4 двунаправленного вывода CTRL, входы MOVXXSC, MOVXXSS, VALIDSD, MOVXXRON1 которого соединены с входами элемента ИЛИ83, входы элемента ИЛИ84 соединены с входами MOVXXRON2÷MOVXXRON4 двунаправленного вывода CTRL, вход Т6 которого соединен с первыми входами элементов И89, И90, вторые выводы которых соединены соответственно с входами MOVRGSP и MOVRGSC двунаправленного вывода CTRL, входы GBM и MOVRGSD которого соединены с входом элемента И91, входы элемента И92 соединены с выходами элементов И89÷И91, выход И92 соединен с выходом END_GMUX двунаправленного вывода CTRL.

Первый вход GB блока 4 памяти операторов (фиг. 4 Л1, Л2) соединен с первым информационным входом мультиплексора МХ96, второй информационный вход которого соединен с первым входом памяти RAMI 10 и выходом счетчика СТ109, входы LOOP_CALL, IFPP_CALL двунаправленного вывода CTRL соединены соответственно с входами элемента И94.1, выход которого соединен с первым входом элемента И94.2, выход которого соединен с первым входом элемента ИЛИ95 и адресным входом мультиплексора МХ96, управляющий вход которого соединен с входом триггера FD97 и выходом элемента ИЛИ95, второй вход которого соединен с выходом элемента И94.3, первый и второй входы которого соединены соответственно с входами MOVSSXX и GBM двунаправленного вывода CTRL, выход мультиплексора МХ96 соединен с первым входом памяти RAM100, второй вход которого соединен с выходом триггера FD97, третий вход памяти RAM100 соединен с выходом триггера FD99, вход которого соединен с выходом элемента И98, первый и второй входы которого соединены соответственно с входами RET и T4 двунаправленного вывода CTRL, входы LOOP и T8 которого соединены соответственно с первыми и вторыми входами элементов И101, И102, третьи входы которых соединены соответственно с входами SIEQ0 и SEQ0 двунаправленного вывода CTRL, входы IFPP, T8. HEQ0 которого соединены соответственно с первого по третий входы элемента И103, выход которого соединен с первым входом элемента ИЛИ104, второй и третий входы которого соединены соответственно с выходами элементов И101, И102, выход элемента ИЛИ104 соединен с вторым входом элемента И94.2 и первым входом элемента ИЛИ105, второй вход которого соединен с адресным входом мультиплексора МХ107 и выходом элемента И106, входы которого соединены соответственно с входами RET и ТИ двунаправленного вывода CTRL, выход регистра REG111 соединен с выходом ОР блока памяти операторов, вторым входом памяти RAM110 и первым информационным входом мультиплексора MX107, второй информационный вход которого соединен с выходом памяти RAM100 и выходом SS блока памяти операторов, управляющий вход мультиплексора MX107 соединен с выходом элемента ИЛИ105 и входом триггера FD108, выход мультиплексора МХ107 соединен с первым входом счетчика СТ109, второй вход которого соединен с выходом триггера FD108, вход INSTR двунаправленного вывода CTRL соединен с управляющими входами счетчика СТ109 и регистра REG111, информационный вход которого соединен с первым выходом памяти RAM110, вход записи WEB которого соединен с первым входом элемента ИЛИ145 и выходом триггера FD141, вход которого соединен с выходом триггера FD140 и с управляющими входами (Л. 2) сумматоров ADD118, ADD124, ADD130, ADD136, выходы Q_ADD которых соединены с третьим входом памяти RAM110 (Л. 1), вход триггера FD140 соединен с выходом элемента ИЛИ139, входы которого соединены соответственно с выходами элементов И137, И138, входы которых соединены соответственно с входами ADDO_MOVO, Т7, CLRO, Т6 двунаправленного вывода CTRL, входы RET, Т4, LOOP, Т8, IFPP, Τ 8 которого соединены соответственно с входами элементов И142-И144, выходы которых соединены соответственно с второго по четвертый входы элемента ИЛИ145, выход которого соединен с выходом END_SO двунаправленного вывода CTRL, второй выход SOB памяти RAM110 соединен соответственно разрядами поля V1 (Л. 2) с информационным входом регистра REG113, разрядами поля V2 с информационным входом регистра REG120, разрядами поля V3 - с информационным входом регистра REG126, разрядами поля V4 - с информационным входом регистра REG132, управляющие входы CE которых соединены с входом Т6 двунаправленного вывода CTRL, второй вход SPB сектора памяти операторов соединен соответственно с информационными входами регистров REG116 разрядами SPB(B-1:0), регистра REG122 - разрядами SPB(C-1:0), регистра REG128 -разрядами SPB(D-1:0), регистра REG134 - разрядами SPB(E-1:0), управляющие входы СЕ которых соединены с выходом элемента И114, входы которого соединены соответственно с входами ADDO_MOVO и Т7 двунаправленного вывода CTRL, вход MOVO двунаправленного вывода CTRL соединен с первыми входами элементов И112, И119, И125, И131, вторые входы которых соединены соответственно с входами MODV1-MODV4 двунаправленного вывода CTRL, выходы элементов И112, И119, И125, И131 соединены соответственно с входами сброса регистров REG113, REG120, REG126, REG132, выходы которых соединены соответственно с первыми информационными входами сумматоров ADD118, ADD124, ADD130, ADD136, вторые информационные входы которых соединены соответственно с выходами регистров REG116, REG122, REG128, REG134, входы сброса которых соединены соответственно с выходами элементов НЕ115, НЕ121, НЕ127, НЕ133, входы которых соединены соответственно с входами MODV1-MODV4 двунаправленного вывода CTRL, входы сброса сумматоров ADD118, ADD124, ADD130, ADD136 соединены соответственно с выходами элементов И117, И123, И129, И135, первые входы которых соединены соответственно с входами MODV1-MODV4 двунаправленного вывода CTRL, вход CLRO которого соединен с вторыми входами элементов И117, И123, И129, И135.

Первый вход ОР блока 5 памяти параметров (фиг. 5) соединен разрядами поля V2(F-1:0) с информационным входом регистра REG148, управляющий вход которого соединен с выходом элемента ИЛИ147, первый вход которого соединен с выходом элемента ИЛИ146, первый и второй входы которого соединены соответственно с входами MOVSPXX и GBH двунаправленного вывода CTRL, входы Т2 и ALU_M которого соединены соответственно с вторым и третьим входами элемента ИЛИ146, выход регистра REG148 соединен с первым входом памяти RAM155, второй вход которой соединен с выходом мультиплексора MX152, первый и второй информационные входы которого соединены соответственно с вторым GB и третьим ALU входами блока памяти параметров, управляющий вход мультиплексора МХ152 соединен с входом триггера FD153 и выходом элемента ИЛИ151, первый и второй входы которого соединены с выходами элементов И149, И150, входы которых соединены соответственно с входами ALU_M, ARITHM_SP, MOVSPXX, GBM двунаправленного вывода CTRL, вход ALU_M которого соединен с адресным входом мультиплексора МХ152, выход триггера FD153 соединен с входом записи WEA памяти RAM155, третий вход которой соединен с выходом регистра REG154, информационный вход которого соединен с первым входом ОР блока памяти параметров разрядами поля V3(F-1:0), управляющий вход регистра REG154 соединен с входом Т2 двунаправленного вывода CTRL, вход Т8 которого соединен с управляющими входами регистров REG156, REG157, информационные входы которых соединены соответственно с первым и вторым выходами памяти RAM155, выход регистра REG156 соединен с первым выходом SPA блока памяти параметров, второй выход SPB которого соединен с выходом регистра REG157 и информационным входом компаратора 159, управляющий вход которого соединен с выходом элемента И158, входы которого соединены с входами IFPP и Т7 двунаправленного вывода CTRL, входы ARITHM_SP, ALU_M, MOVSPXX, Т6, MOVSPSD, GBM соединены соответственно с входами элементов И160-И162, выходы которых соединены с входами элемента ИЛИ 163, выход которого соединен с выходом END_SP двунаправленного вывода CTRL, выход HEQ0 которого соединен с выходом компаратора 159.

Первый вход ОР блока 6 памяти циклов (фиг. 6) разрядами поля V2(G-1:0) и поля V4(G-1:0) соединен соответственно с первым и вторым информационными входами мультиплексора MX166, управляющий вход которого соединен с выходом элемента ИЛИ165, первый вход которого соединен с выходом элемента И164, входы которого соединены соответственно с входами MOVSCXX и GBM двунаправленного вывода CTRL, вход Т2 которого соединен с адресным входом мультиплексора MX166 и вторым входом элемента ИЛИ165, третий и четвертый входы которого соединены соответственно с входами Т3 и ALU_M двунаправленного вывода CTRL, второй GB и третий ALU входы блока памяти циклов соединены соответственно с первым и вторым информационными входами мультиплексора МХ170, управляющий вход которого соединен с входом триггера FD171 и выходом элемента ИЛИ169, входы которого соединены соответственно с выходами элементов И167, И164, входы элемента И169 соединены с входами ALU_M, ARITHM_SC двунаправленного вывода CTRL, вход ALU M которого соединен с адресным входом мультиплексора MX 170, с первого по третий входы памяти RAM180 соединены соответственно с выходами мультиплексоров МХ166, MX170 и триггера FD171, четвертый вход памяти RAM180 соединен с выходом регистра REG174, информационный вход которого соединен с входом ОР блока памяти циклов разрядами поля V3(G-1:0), управляющий вход регистра REG174 соединен с выходом элемента ИЛИ173, первый вход которого соединен с выходом элемента ИЛИ172, входы которого соединены соответственно с входами LOOP, Т8, SEQ0 двунаправленного вывода CTRL, вход Т2 которого соединен с вторым входом элемента ИЛИ173, первый информационный входы мультиплексора MX178 соединен с выходом SIDEC вычитателя 193, второй информационный вход мультиплексора MX178 соединен с выходом REG183 и первым выходом SCA1 блока памяти циклов, управляющий вход мультиплексора MX178 соединен с выходом элемента И172, входом триггера FD179 и первым входом элемента И175, второй вход которого соединен с входом SIEQ0 двунаправленного вывода CTRL, выход элемента И175 соединен с адресным входом мультиплексора MX178, выход которого соединен с пятым входом памяти RAM180, шестой вход которой соединен с выходом триггера FD179, первый выход памяти RAM180 соединен с информационным входом регистра REG182, управляющий вход которого соединен с выходом элемента ИЛИ181, первый вход которого соединен с входом Т6 двунаправленного вывода CTRL и управляющим входом регистра REG184, информационный вход которого соединен с вторым выходом памяти RAM180, выход регистра REG182 соединен с информационными входами регистра REG183 и компаратора 185, первым информационным входом компаратора 189 и вторым выходом SCA2 блока памяти циклов, первый вход элемента И186 соединен с входом PAUSE двунаправленного вывода CTRL, вход LOOP которого соединен с первыми входами элементов И190, И192, вход Т7 двунаправленного вывода CTRL соединен с вторыми входами элементов ИЛИ181, И186, И190, управляющими входами компаратора 185 и регистра REG183, выход регистра REG184 соединен с информационным входом компаратора 191, первым информационным входом вычитателя 193 и третьим выходом SBC блока памяти циклов, выход компаратора 185 соединен с выходом SEGO двунаправленного вывода CTRL, выход элемента И186 соединен с управляющим входом триггера FD187, информационный вход которого соединен с логической «1», выход триггера FD187 соединен с информационным входом счетчика СТ188 и управляющим входом компаратора 189, второй информационный вход которого соединен с выходом счетчика СТ188, вход сброса которого соединен с выходом компаратора 189, входом сброса триггера FD187 и первым входом элемента ИЛИ197, второй вход которого соединен с выходом Q элемента И167, третий и четвертый входы элемента ИЛИ 197 соединены соответственно с выходами элементов И195, И196, входы MOVSCXX и Т6, MOVSCSD и GBM двунаправленного вывода CTRL соединены соответственно с входами элементов И195, И196, выход элемента ИЛИ197 соединен с выходом END_SC двунаправленного вывода CTRL, выход элемента И190 соединен с управляющим входом компаратора 191, выход которого соединен с выходом SIEQ0 двунаправленного вывода CTRL, вход Т8 которого соединен с вторым входом элемента И192, выход которого соединен с управляющим входом вычитателя 193, второй информационный вход которого соединен с логической «1».

Первый SPA и второй SCA2 входы устройства 8 арифметического (фиг. 7) соединены соответственно с первым и вторым информационными входами мультиплексора MX198, управляющий вход которого соединен с управляющим входом мультиплексора MX199 и входом Т8 двунаправленного вывода CTRL, вход ARITHM_SC которого соединен с адресными входами мультиплексоров МХ198, МХ199, первый и второй информационные входы мультиплексора MX199 соединены соответственно с третьим SPB и четвертым SCB входами двунаправленного вывода CTRL, выход мультиплексора MX199 соединен с первыми входами умножителя 201, сумматора-вычитателя 203, делителя 205, вторые входы которых соединены с выходом мультиплексора MX198, третий вход умножителя 201 соединен с выходом элемента И200, входы которого соединены с входами Т9 и OP_MULT двунаправленного вывода CTRL, вход OP_ADD которого соединен с третьим входом сумматора-вычитателя 203, четвертый вход которого соединен с выходом элемента И202, входы которого соединены с входами Т9 и OP_ASUB двунаправленного вывода CTRL, входы Т9 и OP_DIV которого соединены с входами элемента И204, выход которого соединен с третьим входом делителя 205, первый и второй информационные входы мультиплексора МХ207 соединены соответственно с первыми входами умножителя 201 и сумматора-вычитателя 203, третий и четвертый информационные входы мультиплексора МХ207 соединены соответственно с первым и вторым выходами делителя 205, третий выход которого соединен с первым входом элемента ИЛИ208, второй и третий входы которого соединены соответственно с вторыми выходами сумматора-вычитателя 203 и умножителя 201, первый адресный вход мультиплексора МХ207 соединены с выходом элемента ИЛИ206, входы которого соединены с входами OP_ASUB и DIV FRACT двунаправленного вывода CTRL, вход OP_DIV которого соединен с вторым адресным входом мультиплексора МХ207, выход которого соединен с выходом ALU устройства 8 арифметического, выход элемента ИЛИ208 соединен с выходом ALU_M двунаправленного вывода CTRL.

Первый вход GB процессора 9 адресного (фиг. 8 Л1, Л2) соединен с информационными входами регистров REG210, REG219, REG221, управляющие входы которых соединены соответственно с выходами элементов И209, И218, И220, первые входы которых соединены с входом GBM двунаправленного вывода CTRL, входы MOVSEGXX, MOVBASXX, MOVMODXX которого соединены соответственно с вторыми входами элем