Синхронизируемый измеритель фазовых сдвигов

Иллюстрации

Показать всеИзобретение относится к области радиоизмерений и предназначено для определения фазового сдвига как синусоидальных сигналов, так и последовательностей импульсов. Технический результат - повышение эффективности функционирования измерителя фазовых сдвигов за счет исключения ошибки, связанной с нарушением порядка поступления входных сигналов, и повышения точности формирования временных интервалов, определяющих искомый фазовый сдвиг. Для этого синхронизируемый измеритель фазовых сдвигов содержит два формирователя импульсов, два делителя частоты, синхронизатор, логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и измеритель временных интервалов. 2 н. и 3 з.п. ф-лы, 3 ил.

Реферат

Изобретение относится к области радиоизмерений и предназначено для определения фазового сдвига как синусоидальных сигналов, так и последовательностей импульсов.

Простейшим измерителем фазовых сдвигов является устройство, построенное на основе логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к низкочастотному фильтру с индицирующим устройством или к измерителю временных интервалов, в зависимости от требований, предъявляемых к точности и/или форме представления результатов измерений, при этом входами измерителя фазовых сдвигов являются входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (в случае работы с аналоговыми сигналами перед указанными входами устанавливают компараторы напряжений, формирующие импульсы заданного уровня) [Применение интегральных схем: Практическое руководство. Кн. 1. Пер. с англ. / Под ред. А. Уильямса. - М.: Мир, 1987, стр.154-155, рис.3.25; Метрология и радиоизмерения / Под ред. В.И. Нефедова. - М.: Высшая школа, 2003, стр.310, рис.9.14]. Существенным недостатком измерителя, построенного подобным образом, является треугольная форма его преобразовательной характеристики, с вершиной в точке π и основанием 2π. Это ограничивает области применения измерителя, делая его эффективным только для измерения фазовых сдвигов не превосходящих π.

Достаточно распространенным уже много лет является измеритель фазовых сдвигов, выбранный в качестве прототипа, содержащий два формирователя импульсов, RS-триггер и измеритель временных интервалов, выход которого является выходом измерителя фазовых сдвигов, входами которого являются входы формирователей импульсов, выходы которых подключены к соответствующим входам RS-триггера, выход которого подключен ко входу измерителя временных интервалов [Соловов В.Я. Фазовые измерения. - М.: Энергия, 1973, стр.28, рис.1-13; Куликовский К.Л., Купер В.Я. Методы и средства измерений. - М.: Энергоатомиздат, 1986, стр.291, рис.5.6].

Недостатком прототипа является то, что для корректного определения фазовых сдвигов требуется подавать на S-вход RS-триггера опережающий сигнал, а на R-вход - запаздывающий, т.е. требуется априорная информация о знаке временного рассогласования процессов. Указанное ограничивает области применений измерителя и снижает его эффективность, так как при неизвестном знаке фазового сдвига возможно неправильное определение его значения. Если в процессе работы устройства на S-вход RS-триггера первым поступил не опережающий сигнал, а запаздывающий, то фазовый сдвиг будет определен с ошибкой, которая может быть весьма существенной. В этом случае вместо формирования на выходе RS-триггера импульса длительностью, равной относительному временному сдвигу одноименных точек сигналов, поступающих на информационные входы, будет сформирован выходной импульс длительностью, равной разности периода следования сигналов и временного сдвига, заданного разностью фаз. Это является серьезным недостатком устройства.

Технический результат, достигаемый при использовании изобретения, заключается в повышении эффективности функционирования измерителя фазовых сдвигов за счет исключения ошибки, связанной с нарушением порядка поступления входных сигналов, и повышения точности формирования временных интервалов, определяющих искомый фазовый сдвиг.

Технический результат достигается тем, что в синхронизируемый измеритель фазовых сдвигов, содержащий два формирователя импульсов и измеритель временных интервалов, выход которого является выходом измерителя фазовых сдвигов, входами которого являются входы формирователей импульсов, согласно изобретению введены два делителя частоты на два, синхронизатор и логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен со входом измерителя временных интервалов, а входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами первого и второго делителей частоты, входы которых соединены соответственно с выходами первого и второго формирователей импульсов, первый и второй информационные входы синхронизатора объединены с выходами соответственно первого и второго формирователей импульсов, обнуляющие входы делителей частоты объединены и подключены к выходу синхронизатора, обнуляющий вход которого является обнуляющим входом измерителя фазовых сдвигов.

Кроме того, технический результат достигается тем, что, согласно изобретению, синхронизатор для применения в синхронизируемом измерителе фазовых сдвигов содержит два D-триггера и логический элемент ИЛИ, выход которого является выходом синхронизатора, первым и вторым информационными входами которого являются тактовые входы соответственно первого и второго D-триггеров, установочные входы которых объединены и составляют обнуляющий вход синхронизатора, D-входы D-триггеров являются входами фиксированного уровня логического нуля, выходы D-триггеров соединены со входами элемента ИЛИ.

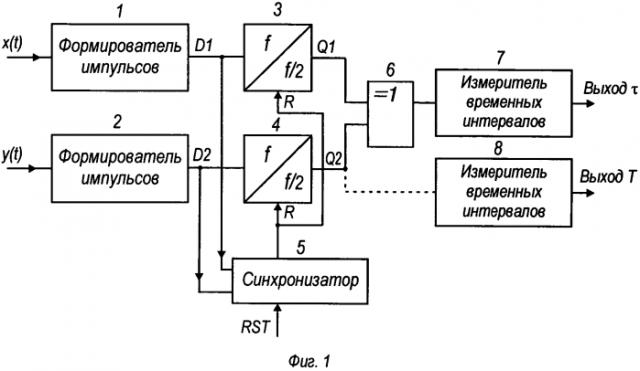

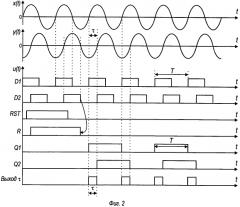

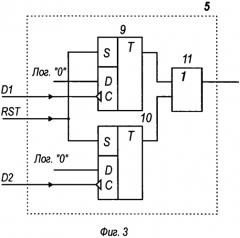

Сущность изобретения поясняется графическим материалом. На фиг.1 показана функциональная схема синхронизируемого измерителя фазовых сдвигов, на фиг.2 - временные диаграммы, иллюстрирующие работу измерителя. На фиг.3 приведена функциональная схема синхронизатора, входящего в состав синхронизируемого измерителя фазовых сдвигов.

Схема по фиг.1 содержит формирователи импульсов 1, 2, делители частоты на два 3, 4, синхронизатор 5, логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и измерители временных интервалов 7, 8. Входы формирователей импульсов 1, 2 являются соответственно информационными входами x(t), y(f) устройства, обнуляющим входом RST которого служит обнуляющий вход синхронизатора 5, информационные входы которого соединены с выходами формирователей импульсов 1, 2, информационный вход делителя частоты 3 соединен с выходом формирователя импульсов 1, а информационный вход делителя частоты 4 - с выходом формирователя импульсов 2, обнуляющие входы делителей частоты 3, 4 объединены и подключены к выходу синхронизатора 5, выходы делителей частоты 3, 4 соединены со входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6, выход которого соединен со входом измерителя временных интервалов 7, выход которого является первым выходом устройства, вторым выходом которого является выход измерителя временных интервалов 8, вход которого соединен с выходом делителя частоты 4.

Временные диаграммы (см. фиг.2) содержат синусоидальные сигналы на входах x(t) и y(t), имеющие период T, фазовый сдвиг Δφ между которыми следует определить, показанный в виде временного интервала τ; импульсы D1 и D2 на выходах формирователей 1, 2 соответственно; импульс обнуления на входе RST; логические уровни R на обнуляющих входах делителей частоты 3, 4; импульсы Q1 и Q2 на выходах делителей частоты 3 и 4 соответственно; импульсы длительностью τ на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6.

Синхронизатор 5, показанный на схеме по фиг.3, содержит D-триггеры 9, 10 и логический элемент ИЛИ 11, выход которого является выходом синхронизатора, информационными входами D1 и D2 которого являются тактовые входы D-триггеров 9 и 10 соответственно, установочные входы которых объединены и составляют обнуляющий вход RST синхронизатора, D-входы D-триггеров 9, 10 являются входами фиксированного уровня логического нуля, выходы D-триггеров 9,10 соединены со входами элемента ИЛИ.

Рассмотрим работу предложенного измерителя (см. фиг.1) на примере определения фазового сдвига Δφ между двумя синусоидальными сигналами x(t)=Xsinωt и y(t)=Ysin(ωt-Δφ), причем Δφ=ωτ. Указанные сигналы клиппируются, т.е. преобразуются в импульсы D1 и D2 длительностью, равной длительности полуволн синусоид (см. фиг.2), после чего полученные последовательности импульсов поступают одновременно на входы делителей частоты 3, 4 и синхронизатора 5. Задача синхронизатора - определить по поступающим импульсам интервал времени, в течение которого последовательно сформировались отрицательные фронты импульсов из двух последовательностей и по окончании этого интервала разрешить работу делителей частоты 3, 4. То есть фиксируются моменты времени

и ,

где

t n x - момент времени окончания действия n-й положительной полуволны сигнала x(t);

t n y - момент времени окончания действия n-й положительной полуволны сигнала y(t);

n=1, 2, 3, …

Указанное позволяет обеспечить запуск делителей частоты 3, 4 не в произвольные моменты времени, а строго по окончании действия двух смежных полуволн одного знака из сигналов x(t), y(t). В результате в момент времени t n x + T 2 начинает работу тот делитель частоты, на вход которого поступает опережающий сигнал x(t), а в момент t n y + T 2 - делитель частоты, на вход которого поступает запаздывающий сигнал y(t). В нашем примере это делители 3 и 4 соответственно. Причем несложно видеть, что ( t n y + T 2 ) − ( t n x + T 2 ) = τ .

Синхронизация начинается с обнуления измерителя. Для этого на вход RST подают обнуляющий импульс (см. временные диаграммы на фиг.2), который блокирует работу делителей до тех пор, пока не проследуют, как указывалось выше, два смежных отрицательных фронта. По второму (по более позднему) из них на выходе синхронизатора 5 снимается активный обнуляющий уровень и делители частоты 3, 4 начинают работу, в результате которой формируются последовательности импульсов Q1 и Q2 с уменьшенной в два раза частотой, т.е с периодом 2Т, длительностью импульсов Т и относительным временным сдвигом τ. Полученные последовательности импульсов сравниваются путем выполнения логической операции «неравнозначность» - для этого служит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, в результате чего на выходе указанного элемента формируется последовательность импульсов с длительностями, равными временным интервалам τ и с частотой 1/Т, равной частоте входных сигналов. Далее в измерителе временных интервалов 7 оценивается величина τ, пропорциональная Δφ, а при необходимости преобразуется непосредственно в Δφ, исходя из известной величины ω.

Особенность работы заявленного измерителя, состоящая в синхронизации процесса выделения временных интервалов, определяющих искомый фазовый сдвиг Δφ, позволяет исключить ошибки, связанные с некорректным выделением временных интервалов τ, когда начало интервала определяется не опережающим сигналом, а запаздывающим. Таким образом исключается составляющая абсолютной погрешности оценки Δ интервалов τ, выражаемая как Δ=T-2τ. Причем, как несложно понять из приведенного, погрешность Δ может быть весьма существенной при относительно больших периодах T и малых сдвигах τ. Это легко видеть из выражения для относительной погрешности оценки, характерной для прототипа и других подобных устройств: δ = ( T τ − 2 ) 100 % . Следовательно, при работе измерителя не требуется иметь априорную информацию о знаке фазового сдвига Δφ: независимо от распределения сигналов по входам измерителя начало временного интервала будет определяться опережающим сигналом.

Один из вариантов реализации синхронизатора показан на фиг.3. Запуск синхронизатора осуществляется подачей на вход RST (см. фиг.3) импульса обнуления, после чего каждый из D-триггеров 9, 10 переводится в состояние высокого логического уровня на выходе и устанавливает такой же уровень на выходе элемента ИЛИ 11, а следовательно, и на входах обнуления делителей частоты 3, 4. Далее с формированием отрицательных фронтов импульсов на входах D1, D2 синхронизатора (см. временные диаграммы на фиг.2) каждый из D-триггеров 9, 10 возвращается в исходное состояние (поочередно или одновременно, в зависимости от того отличен фазовый сдвиг от нуля или нет) и на выходе элемента ИЛИ 11 устанавливается низкий логический уровень, разрешающий работу делителей частоты 3, 4. Таким образом синхронизатор останавливает работу делителей 3, 4, обнуляет их и разрешает работу только после того, как сформировались две положительные полуволны, по одной в каждом сигнале x(t), y(t).

Описанное устройство при наличии дополнительного измерителя временных интервалов 8 позволяет одновременно с фазовым сдвигом определять и период T сигналов x(t), y(t): он равен длительности импульсов на одном из выходов Q1, Q2 делителей частоты 3, 4. Для измерения периода T или косвенно частоты ω достаточно снять сигнал с одного из упомянутых выходов, как показано штриховыми линиями на фиг.1.

Относительно реализации устройства заметим, что в качестве формирователей импульсов могут быть использованы традиционно применяемые в подобных случаях аналоговые компараторы с установкой в качестве опорного уровня нулевого потенциала общего провода, а в качестве делителей частоты на два можно с успехом использовать D-триггеры с обнуляющими входами, включенные в счетный режим [Аванесян Г.Р. Цифровые интегральные микросхемы. - М.: Радиотехника, 2008, стр.90, рис.2.17]. Возможно применение формирователей импульсов, выдающих короткие импульсы длительностью, много меньшей длительности клиппируемой полуволны, привязанные к моментам пересечения сигналом нулевого уровня. Такое решение может быть обусловлено требованиями, задаваемыми принципом действия синхронизатора 5 или делителей частоты 3, 4. Реализуется подобный формирователь путем объединения аналогового компаратора с формирователем коротких импульсов, который подключается к выходу компаратора.

1. Синхронизируемый измеритель фазовых сдвигов, содержащий два формирователя импульсов и измеритель временных интервалов, выход которого является выходом измерителя фазовых сдвигов, входами которого являются входы формирователей импульсов, отличающийся тем, что в него введены два делителя частоты на два, синхронизатор и логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен со входом измерителя временных интервалов, а входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами первого и второго делителей частоты, входы которых соединены соответственно с выходами первого и второго формирователей импульсов, первый и второй информационные входы синхронизатора объединены с выходами соответственно первого и второго формирователей импульсов, обнуляющие входы делителей частоты объединены и подключены к выходу синхронизатора, обнуляющий вход которого является обнуляющим входом измерителя фазовых сдвигов.

2. Синхронизируемый измеритель фазовых сдвигов по п.1, отличающийся тем, что формирователь импульсов представляет собой аналоговый компаратор, выход которого является выходом формирователя импульсов, входом формирователя импульсов является один из входов компаратора, другой вход которого является входом опорного напряжения.

3. Синхронизируемый измеритель фазовых сдвигов по п.1, отличающийся тем, что формирователь импульсов состоит из аналогового компаратора и формирователя коротких импульсов, выход которого является выходом формирователя импульсов, входом формирователя импульсов является один из входов компаратора, другой вход которого является входом опорного напряжения, выход компаратора соединен со входом формирователя коротких импульсов.

4. Синхронизируемый измеритель фазовых сдвигов по п.1, отличающийся тем, что делитель частоты на два построен на основе D-триггера, включенного в счетный режим, обнуляющий вход которого является обнуляющим входом делителя частоты.

5. Синхронизатор для применения в синхронизируемом измерителе фазовых сдвигов по п.1, отличающийся тем, что содержит два D-триггера и логический элемент ИЛИ, выход которого является выходом синхронизатора, первым и вторым информационными входами которого являются тактовые входы соответственно первого и второго D-триггеров, установочные входы которых объединены и составляют обнуляющий вход синхронизатора, D-входы D-триггеров являются входами фиксированного уровня логического нуля, выходы D-триггеров соединены со входами элемента ИЛИ.