Средство разделенной загрузки/сохранения и команда для него

Иллюстрации

Показать всеИзобретение относится к области функциональных возможностей команд процессора компьютерной системы. Техническим результатом является повышение эффективности выполнения неделимых операций. В заявке описана команда разделенной загрузки/сохранения, при выполнении которой ЦП осуществляется доступ к операндам из двух разделенных ячеек памяти, и устанавливаются индикаторы кода условия, указывающие, был ли осуществлен неделимый доступ к двум операндам посредством блочно-параллельного заблокированного выбираемого обращения к операндам без промежуточных операций обращения к запоминающему устройству из других ЦП. При использовании упомянутой команды в форме разделенной загрузки пары доступом является загрузка, а разделенные данные хранятся в общих регистрах. 3 н. и 13 з.п. ф-лы, 19 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к компьютерным системам, более точно, к функциональным возможностям команд процессора компьютерной системы. Предпосылки создания изобретения

Товарные знаки: IBM® является зарегистрированным товарным знаком International Business Machines Corporation (Армонк, штат Нью-Йорк, США). S/390, Z900 и z990 и названия других продуктов могут являться зарегистрированными товарными знаками или названиями продуктов International Business Machines Corporation или других компаний.

Начиная с появившихся в 60-х годах машин, известных как IBM® System 360, и до настоящего времени усилиями множества высокоодаренных инженеров IBM была создана особая архитектура, которая получила известность как "мэйнфрейм" в силу своей неотъемлемой принадлежности к вычислительной системе и принципы работы которой определяют архитектуру машины путем описания команд, которые могут выполняться путем реализации в "мэйнфрейме" созданных изобретателями IBM команд, которые с учетом их существенной роли в течение многих лет включены в руководство IBM Principles of Operation. Восьмое издание руководства IBM® z/Architecture® Principles of Operation, опубликованное в феврале 2009 г., стало стандартным справочным материалом SA22-7832-07 и включено в описание серверов на основе мэйнфреймов IBM ZlO™.

Как указано в патенте US 5742785 под названием "Posting multiple reservations with a conditional store atomic operations in a multiprocessing environment", правопреемником которого является IBM, и заявка на который подана 20 ноября 1995 г., "Несколько переменных, которые совместно используются в режиме мультипроцессорной обработки, могут обновляться как одна неделимая операция. Каждый компьютерный процессор, работающий в режиме мультипроцессорной обработки, содержит несколько регистров резервирования, которые наряду с новым способом используются для резервирования каждой из нескольких совместно используемых переменных. Во время выполнения программы может резервироваться множество совместно используемых переменных, каждая ее соответствующим регистром резервирования. Резервирование совместно используемой переменной осуществляется посредством особой команды. Регистр резервирования отслеживает: адрес совместно используемой переменной, которую он резервирует, значение измененных результатов, которые должны обновляться в совестно используемом переменном адресе, была ли обновлена переменная, разрешено ли резервирование, и обладает ли процессор, содержащий регистр резервирования, полномочием обновлять совместно используемую переменную. Резервирование может быть аннулировано, если второй процессор попытается считать адрес зарезервированной совместно используемой переменной. При обнаружении команды, которая пытается обновить совместно используемую переменную, набор указанных этой командой зарезервированных измененных совместно используемых переменных, которые содержат обновленные измененные результаты, обновляются как одна неделимая операция, тогда и только тогда, когда в указанном наборе разрешены все резервирования. Если какое-либо из резервирований в наборе аннулировано, ни одна из совместно используемых переменных из набора не обновляется. Код условия указывает, было ли обновление успешным, или оно не произошло. Код условия может проверяться, и последовательность команд может повторяться до ее успешного выполнения".

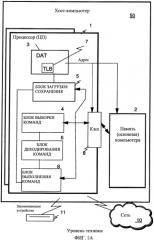

На фиг.1А представлены характерные элементы известной из техники компьютерной хост-системы 50. В компьютерной системе также могут применяться другие варианты размещения элементов, которые хорошо известны из техники. Характерный хост-компьютер 50 содержит один или несколько ЦП 1, связанных с основным запоминающим устройством (памятью 2 компьютера), а также интерфейсы ввода-вывода для сопряжения с запоминающими устройствами 11 и подключения к сетям 10 для связи с другими компьютерами или SAN и т.п. ЦП 1 совместим с архитектурой, содержащей структурированную систему команд и структурированные функциональные возможности. ЦП 1 может осуществлять динамическое преобразование 3 адреса (DAT) с целью преобразования адресов программ (виртуальных адресов) в действительный адрес памяти. DAT обычно содержит буфер 7 быстрого преобразования адреса (TLB) для кэширования преобразований, чтобы при последующих доступах к блоку памяти 2 компьютера не требовалась задержка преобразования адреса. Обычно между памятью 2 компьютера и процессором 1 используется кэшпамять 9. Кэш-память 9 может являться иерархической и состоящей из кэша большой емкости, доступного для нескольких ЦП, и более быстродействующих кэшей (низкого уровня) меньшей емкости между кэшем большой емкости и каждым ЦП. В некоторых случаях реализации кэши низкого уровня разделены на отдельные кэши низкого уровня для выборки команд и доступа к данным. В одном из вариантов осуществления блок 4 выборки команд вызывает из памяти 2 команду посредством кэш-памяти 9. Команда декодируется в блоке 6 декодирования команд и отправляется (с другими командами в некоторых вариантах осуществления) в блоки 8 выполнения команд. Используется несколько блоков 8 выполнения команд, например, блок выполнения арифметических команд, блок выполнения команд с плавающей точкой и блок выполнения команд перехода. Команда выполняется блоком, который в зависимости от необходимости осуществляет доступ к операндам из определяемых командами регистров или памяти. Если доступ (загрузка или сохранение) к операнду должен осуществляться из памяти 2, блок 5 загрузки/сохранения обычно обрабатывает процедуру доступа под управлением выполняемой команды. Команды могут выполняться в аппаратных схемах или во внутреннем микрокоде (аппаратно-программном обеспечении) или с использованием сочетания того и другого.

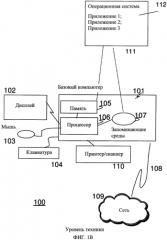

На фиг.1Б проиллюстрирован один из примеров известной из техники компьютерной хост-системы 21 эмуляции, которая эмулирует компьютерную хост-систему 50, имеющую хост-архитектуру. Хост-процессором (ЦП) 1 в компьютерной хост-системе 21 эмуляции является хост-процессор (или виртуальный хост-процессор) эмуляции, представляющий собой процессор 27 эмуляции со структурой собственных команд, отличающейся от структуры команд процессора 1 хост-компьютера 50. Компьютерная хост-система 21 эмуляции имеет память 22, доступную для процессора 27 эмуляции. В примере осуществления память 22 разделена на память 2 хост-компьютера и память 23 программ эмуляции. Память 2 хост-компьютера доступна для программ хост-компьютера 21 эмуляции в зависимости от архитектуры хост-компьютера. Процессор 27 эмуляции выполняет собственные команды структурированной системы команд, структура которых отличается от структуры команд эмулируемого процессора 1 и которые извлекаются из памяти 23 программ эмуляции, и может осуществлять выборку хост-команды для выполнения из программы в памяти 2 хост-компьютера путем применения одной или нескольких команд из программы контроля последовательности и выборки/декодирования (Sequence & Access/Decode), которая может декодировать выбранную хост-команду(-ы) и определять программу выполнения собственных команд эмуляции функции выбранной хост-команды. Другие средства, которые предусмотрены в архитектуре компьютерной хост-системы 50, могут эмулироваться программами структурированных средств (Architected Facilities Routines), включая такие средства, как, например, регистры общего назначения, управляющие регистры, поддержка подсистемы динамического преобразования адреса и ввода-вывода и кэш-память процессора. Программы эмуляции также могут использовать функции, доступные в процессоре 27 эмуляции (такие как общие регистры и динамическое преобразование виртуальных адресов) для повышения производительности программ эмуляции. Также может быть предусмотрено особое программное обеспечение и механизмы разгрузки, облегчающие процессору 27 эмуляцию функции хост-компьютера 50.

В мэйнфрейме структурированные машинные команды используются программаторами, обычно современными программаторами на языке "С" посредством компилирующего приложения. Эти команды, хранящиеся в запоминающей среде, могут выполняться в собственной системе команд сервера IBM® на основе z/Architecture® или в качестве альтернативы в машинах на основе других архитектур. Они могут эмулироваться в существующих и будущих серверов на основе мэйнфреймов IBM и в других машинах IBM (например, серверах pSeries® и xSeries®). Они могут выполняться в операционной системе Linux разнообразными машинами, использующими аппаратное обеспечение производства IBM, Intel, AMD, Sun Microsystems и других компаний. Помимо выполнения этим аппаратным обеспечением на основе системы Z/Architecture®, может использоваться Linux, а также машины, использующие эмуляцию, как описано на сайтах http://www.turbohercules.com, http://www.hercules-390.org и http://www.funsoft.com. В режиме эмуляции эмулирующее программное обеспечение выполняется собственным процессором, эмулирующим архитектуру эмулируемого процессора.

Собственный процессор 27 обычно выполняет эмулирующее программное обеспечение 23, представляющее собой аппаратно-программное обеспечение или собственную операционную систему для эмуляции эмулируемого процессора. Эмулирующее программное обеспечение 23 отвечает за выборку и выполнение команд архитектуры эмулируемого процессора. Эмулирующее программное обеспечение 23 поддерживает счетчик эмулируемых команд для слежения за границами команд. Эмулирующее программное обеспечение 23 может осуществлять выборку одной или нескольких эмулируемых машинных команд за один раз и преобразование одной или нескольких эмулируемых машинных команд в соответствующую группу собственных машинных команд для выполнения собственным процессором 27. Эти преобразованные команды могут помещаться в кэш, что позволяет ускорять преобразование. Тем не менее, эмулирующее программное обеспечение должно поддерживать правила архитектуры эмулируемого процессора с тем, чтобы обеспечивать правильную работу операционных систем и приложений, написанных для эмулируемого процессора. Кроме того, эмулирующее программное обеспечение должно обеспечивать ресурсы, указанные архитектурой эмулируемого процессора 1, включая без ограничения управляющие регистры, регистры общего назначения, регистры с плавающей точкой, функцию динамического преобразования адреса, включая таблицы сегментов и таблицы страниц, например, механизмы прерывания, механизмы переключения контекста, часы истинного времени (TOD) и структурированные интерфейсы с подсистемами ввода-вывода с тем, чтобы операционная система или прикладная программа, рассчитанная на работу в эмулируемом процессоре, могла быть запущена в собственном процессоре, имеющем эмулирующее программное обеспечение.

Конкретная эмулируемая команда декодируется, и вызывается подпрограмма для выполнения функции отдельной команды. Функция 23 эмулирующего программного обеспечения, эмулирующая функцию эмулируемого процессора 1, реализуется, в подпрограмме или драйвере на языке "С" или каким-либо другим способом обеспечения драйвера для конкретного аппаратного обеспечения, доступным для специалистов в данной области техники, ознакомившихся в описанием предпочтительного варианта осуществления. В различных патентах, в которых предложена эмуляция программного и аппаратного обеспечения, включая без ограничения патент US 5551013 под названием "Multiprocessor for hardware emulation", выданный на имя Beausoleil и др., патент US 6009261 под названием "Preprocessing of stored target routines for emulating incompatible instructions on a target processor", выданный на имя Scalzi и др.; патент US 5574873 под названием "Decoding guest instruction to directly access emulation routines that emulate the guest instructions", выданный на имя Davidian и др.; патент US 6308255 под названием "Symmetrical multiprocessing bus and chipset used for coprocessor support allowing non-native code to run in a system", выданный на имя Gorishek и др.; патент US 6463582 под названием "Dynamic optimizing object code translator for architecture emulation and dynamic optimizing object code translation method", выданный на имя Lethin и др.; патент US 5790825 под названием "Method for emulating guest instructions on a host computer through dynamic recompilation of host instructions", выданный на имя Eric Traut; и многие другие, проиллюстрированы разнообразные известные способы эмуляции формата команд, структурированного для отличающейся машины, в целевой машине, доступные для специалистов в данной области техники, а также используемые ими промышленные средства программного обеспечения.

В патенте US 5870598 под названием "Method and apparatus for providing an optimized compare-and-branch instruction" от 29 августа 1997 г., правопреемником которого является Intel®, Corp., описана оптимизированная команда сравнения и перехода для выполнения в микропроцессоре с сокращенным набором команд. Реализованный в микропроцессоре задатчик последовательности команд реагирует на команду сравнения и перехода с целью ее эффективного выполнения. Задатчик последовательности команд обнаруживает команду сравнения и перехода и выполняет ее как обычную команду сравнения. В следующем цикле задатчик последовательности команд преобразует ее в команду перехода и обеспечивает преобразованную команду для выполнения одним из блоков выполнения команд. Выполняется команда перехода, выбирается или не выбирается переход, и продолжается нормальный процесс выполнения программы. Команда Intel имеет несколько недостатков, в том числе то, что в ходе выполнения задаются коды условия, что разрушает установки контекста, которые могут потребовать восстановления.

В патенте US 7296120 В2 под названием "Mechanism that Provides Efficient Multi-Word Load Atomicity", выданном 13 ноября 2007 г.на имя Corrigan и др., описаны устройство, способ и программный продукт для обеспечения поддержки неделимой загрузки нескольких слов без дополнительного использования памяти. Двойное слово загружается как одна неделимая операция без использования одного или нескольких дополнительных полей и без блокировки. В случае неудачного обращения к кэш-памяти используется маркер недостоверности, чтобы установить, было ли двойное слово сохранено и загружено как одна неделимая операция, и, соответственно, является ли оно достоверным.

Краткое изложение сущности изобретения

В изобретении предложена команда для доступа к памяти и установки индикатора, указывающего, выглядит ли осуществленный доступ неделимым, иными словами, был ли доступ к данным, вызванным из памяти или сохраненным в памяти, осуществлен без какой-либо промежуточной операции обращения к запоминающему устройству, которая могла изменить часть данных, к которым был получен доступ.

В вариантах осуществления изобретения эта команда используется для вызова хранимых в памяти разделенных операндов, предусматривающего выполнение первой подпрограммы, содержащей команды вызова хранимых в памяти разделенных операндов, при этом упомянутые команды включают команду разделенной загрузки пары (Load Pair Disjoint) для загрузки двух разделенных операндов из памяти и установки значения кода условия. Если значение кода условия указывает, что два разделенных операнда могли быть загружены в любой из двух разделенных операндов с использованием промежуточной операции обращения к запоминающему устройству, выполняется вторая подпрограмма, содержащая команды вызова из памяти хранимых разделенных операндов. Если значение кода условия указывает, что два разделенных операнды были загружены в любой из двух разделенных операндов без промежуточной операции обращения к запоминающему устройству, выполняется третья подпрограмма использования загруженных двух разделенных операндов.

В одном из вариантов осуществления вторая программа повторно выполняется, пока значение кода условия не будет указывать, что два разделенных операнда были загружены в любой из двух разделенных операндов без промежуточной операции обращения к запоминающему устройству.

В одном из вариантов осуществления устанавливается предельное значение для повторного выполнения. Если значение кода условия указывает, что два разделенных операнда могли быть загружены в любой из двух разделенных операндов с использованием промежуточной операции обращения к запоминающему устройству, вторая подпрограмма повторно выполняется, пока не произойдет одно из следующего: вторая подпрограмма будет повторно выполнена то число раз, которое установлено предельным значением, или значение кода условия будет указывать, что два разделенных операнда были загружены в любой из двух разделенных операндов без промежуточной операции обращения к запоминающему устройству.

В одном из вариантов осуществления команда разделенной загрузки пары приводит к загрузке двух разделенных операндов в соответствующие положения общего регистра.

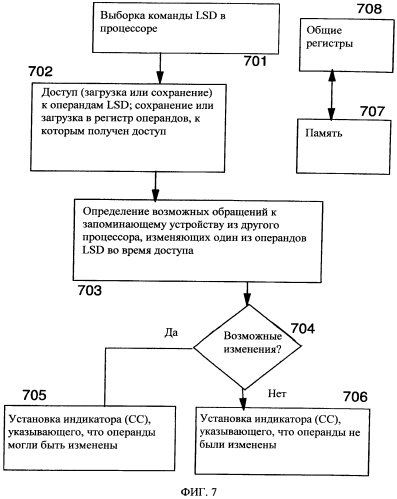

В одном из вариантов осуществления в процессоре мультипроцессорной системы выполняется команда разделенной загрузки/сохранения (LSD - от англ. Load/Store Disjoint). Выполняемая команда разделенной загрузки/сохранения содержит код операции, а ее выполнение включает выполнение определяемой командой LSD операции, исходя из заданного кода операции, которая представляет собой доступ к одному или нескольким операндам в памяти. В зависимости от того, мог ли один из одного или нескольких операндов быть изменен во время доступа к одному или нескольким операндам в памяти в результате события обращения к запоминающему устройству из другого процессора мультипроцессорной системы, устанавливается первое значение индикатора, указывающее, мог ли один из одного или нескольких операндов быть изменен во время доступа к одному или нескольким операндам в памяти в результате события обращения к запоминающему устройству из другого процессора мультипроцессорной системы.

В одном из вариантов осуществления первое значение индикатора представляет собой любое из следующего: первое значение кода условия или второе значение кода условия. Если определено, что первый операнд в памяти или второй операнд в памяти из одного или нескольких операндов мог быть изменен во время упомянутого доступа в результате события обращения к запоминающему устройству, устанавливается первое значение кода условия, указывающее, что во время упомянутого доступа могло быть изменено любое из следующего: первый операнд в памяти или второй операнд в памяти. Если определено, что в результате события обращения к запоминающему устройству во время упомянутого доступа не был изменен ни первый операнд в памяти, ни второй операнд в памяти, устанавливается второе значение кода условия, указывающее, что во время упомянутого доступа не был изменен ни первый операнд в памяти, ни второй операнд в памяти.

В одном из вариантов осуществления командой LSD является команда разделенной загрузки пары (LPD - от англ. Load Pair Disjoint), при этом доступ к одному или нескольким операндам в памяти включает вызов из памяти первого операнда и второго операнда, и дополнительно включает сохранение первого операнда в первом регистре, указанном командой LPD, и сохранение второго операнда во втором регистре, указанном командой LPD.

В одном из вариантов осуществления, в котором команда разделенной загрузки пары содержит поле первого общего регистра, указывающее первый общий регистр, поле второго общего регистра, указывающее второй общий регистр, и поле третьего общего регистра, указывающее первый регистр и второй регистр, при этом из первого общего регистра, указанного в поле первого общего регистра, извлекается первый адрес, который используется для вызова первого операнда в памяти. Из второго общего регистра, указанного в поле второго общего регистра, извлекается второй адрес, который используется для вызова второго операнда в памяти. Операция разделенной загрузки пары включает сохранение первого операнда в первом регистре, который является старшей частью общего регистра, указанного в поле третьего общего регистра, и сохранение второго операнда во втором регистре, который является младшей частью общего регистра, указанного в поле третьего общего регистра.

В одном из вариантов осуществления, в котором команда разделенной загрузки пары дополнительно содержит первое поле смещения и второе поле смещения, первое поле смещения арифметически суммируется с полученным первым адресом с целью создания первого адреса памяти для вызова первого операнда в памяти. Второе поле смещения арифметически суммируется с полученным вторым адресом с целью создания второго адреса памяти для вызова второго операнда в памяти.

В одном из вариантов осуществления от множества процессоров мультипроцессорной системы принимаются события обращения к запоминающему устройству, и данные принятых операций обращения к запоминающему устройству сохраняются в памяти.

В одном из вариантов осуществления, в котором команда разделенной загрузки пары, заданная для вычислительной машины с определенной архитектурой, вызывается и выполняется центральным процессором вычислительной машины с альтернативной архитектурой, команда разделенной загрузки пары интерпретируется, чтобы идентифицировать заданную программу системы программного обеспечения для эмуляции функции команды разделенной загрузки пары, при этом выполнение команды разделенной загрузки пары включает выполнение заданной программы системы программного обеспечения для осуществления шагов способа выполнения машинной команды.

Перечисленные, а также дополнительные задачи, признаки и преимущества настоящего изобретения станут ясны из следующего далее описания.

Краткое описание чертежей

Далее лишь в качестве примера описаны варианты осуществления изобретения со ссылкой на сопровождающие его чертежи, на которых:

на фиг.1А схематически проиллюстрирован один из примеров известной из техники компьютерной хост-системы,

на фиг.1Б - один из примеров известной из техники эмулирующей компьютерной хост-системы,

на фиг.1В - один из примеров известной из техники компьютерной системы,

на фиг.2 - один из примеров известной из техники компьютерной сети, на фиг.3 - один из примеров элементов известной из техники

компьютерной системы,

на фиг.4А-4В - подробные элементы известной из техники компьютерной системы,

на фиг.5А-5Е - известный из техники формат машинной команды компьютерной системы,

на фиг.6 - один из примеров форматов команд согласно вариантам осуществления изобретения,

на фиг.7-9 - один из примеров осуществления и

на фиг.10 - примеры элементов мультипроцессорной системы, в которой применяется и осуществляется изобретение.

Осуществление изобретения

В современных мультипроцессорных компьютерных системах обеспечивается возможность для двух или более процессоров осуществлять доступ к ячейкам общей памяти и изменять их. Такие ячейки считаются совместно используемыми, при этом считается, что в каждой из них содержится совместно используемая переменная.

Другим контекстом, в котором совместно используемые переменные существуют в компьютерной системе, является отдельный процессор, в котором одновременно постоянно хранятся отдельные и различные программы (иногда называемые процессами). Каждый процесс осуществляет управление в течение определенного периода времени, называемого квантом, а в конце кванта управление приостанавливается, и доступ к процессору получает другой процесс. Процессы выполняются таким образом, что их соответствующие кванты чередуются во времени, при этом их выполнение разрешается на циклической основе или на основе приоритетов. Процессы способны осуществлять доступ к ячейкам общей памяти и изменять их, и, соответственно, эти процессы логически действуют в одном процессоре в ячейках совместно используемой памяти, как если бы они действовали в отдельных и различных процессорах.

В любом случае, поскольку два или более параллельных процесса способны обновлять совместно используемую переменную, существует возможность внесения несогласованного обновления. Предположим, что перед каждым из двух процессов стоит задача приращения значения в ячейке памяти. Каждый процесс пытается выполнить задачу путем считывания значения из ячейки в регистр машины, приращения значения регистра машины и затем записи в память нового значения регистра машины. Если процесс 1 выполняет операцию чтения/изменения/записи без вмешательства со стороны процесса 2, и, если затем процесс 2 выполняет такие же операции, совместно используемая переменная будет корректно изменена путем приращения дважды.

Несогласованность возникает, когда операции чтения/изменения/записи двух процессов чередуются во времени. Иными словами, если процесс 1 считывает значение переменной X, затем процесс 2 считывает такое же значение переменной X, и последующие приращения и записи происходят в произвольном порядке, каждый процесс сохранит значение X, равное его первоначальному значению, приращенному один раз. Соответственно, в окончательном значении X будет отображено только одно приращение. Одно приращение будет потеряно.

Причиной получения неверного окончательного значения является то, что два процесса оперируют несогласованными данными. Если процесс 1 считывает значение X с намерением изменить его, логическая резиденция X перемещается из совместно используемой памяти в частный регистр, связанный с процессом 1. Если затем процесс 2 считывает значение X, при этом значение X еще не было изменено процессом 1, значение, считанное процессом 2, не согласуется с фактическим значением X, поскольку значение X в данный момент недоступно в совместно используемой памяти, и не будет доступно снова до его перезаписи.

Для обеспечения правильности необходимо обеспечивать согласованность. Достаточным условием согласованного поведения является обеспечение того, что при выполнении последовательности операций чтения/изменения/записи совместно используемой переменной X, последовательность выполняется как одна неделимая операция. Под одной неделимой операцией подразумевается, что последовательность выполняется таким образом, чтобы какой-либо другой процесс не мог изменить значение X в интервале между моментом чтения значения X и моментом записи значения X.

Существует множество способов обеспечения правильности и согласованности последовательностей операций чтения/изменения/записи. Одним из способов является помещение таких последовательностей в область программы, называемую критической секцией. Критической секции предшествует одна или несколько команд, которые выполняют операцию блокирования, а за критической секцией следует одна или несколько команд, которые выполняют операцию разблокирования. Операции блокирования и разблокирования гарантируют, что в любой определенный момент код в критической секции способен выполнять самое большее один процесс. Если по соглашению или согласно протоколу все остальные процессы обновляют одни и те же совместно используемые переменные посредством критических секций, управляемых одним и тем же механизмом блокирования и разблокирования, обновление совместно используемых переменных может выполняться как одна неделимая операция в ходе операций чтения/изменения/записи в критической секции, поскольку ни один другой процесс не способен осуществлять промежуточный доступ к совместно используемым переменным в то время, как какой-либо процесс выполняет операции чтения/изменения/записи в критической секции.

Для создания критической секции необходима функция блокирования. Как известно из техники, обычным средством реализации такой функции является команда, которая сама выполняет неделимые операции чтения/изменения/записи с заблокированной переменной. В число команд, используемых с этой целью, входит команда проверки и установки (Test-and-Set) и команда приращения (Increment) (или отрицательного приращения) (Decrement).

Команда проверки и установки считывает значение переменной X, присваивает значению переменной X разряд 1 независимо от исходного состояния разряда, перезаписывает значение переменной X, и выдает код условия, значение которого равно исходному разряду до принудительного приравнивания его значения к 1. Поскольку эта команда выполняет операции чтения/изменения/записи совместно используемой переменной, она должна быть реализована в расчете на осуществление такого обновления в качестве одной неделимой операции, чтобы обеспечить согласованность выполнения. Эта одна команда может использоваться для установки блокировки, защищающей критическую секцию, в которой может согласованно выполняться последовательность операций чтения/изменения/записи произвольной сложности, поскольку блокировка предотвращает промежуточный доступ со стороны других процессов к совместно используемым переменным.

С целью использования команды проверки и установки для создания блокировки каждый процесс защищает критическую секцию с помощью команды проверки и установки, которая осуществляет доступ к заблокированной переменной. Заблокированная переменная сохраняет значение 1 непосредственно после выполнения команды проверки и установки независимо от ее прежнего значения. Каждый процесс проверяет код условия после выполнения команды проверки и установки, и только процесс, который обнаруживает значение кода, равное 0 (соответствующее исходному значению, равному 0), способен входить в критическую секцию и выполнять в ней последовательность операций чтения/изменения/записи. Все остальные процессы, пытающиеся выполнять код чтения/изменения/записи в своих соответствующих критических секциях, должны ожидать или выполнять какие-либо другие действия, пока заблокированное состояние критической секции не изменится на разблокированное (0) состояние. Когда какой-либо процесс завершает выполнение последовательности чтения/изменения/записи и выходит из критической секции, блокировка снимается путем сохранения 0 в блокировке, что позволяет другому процессу входить в критическую секцию путем выполнения заблокированной команды проверки и установки при исходном значении переменной, равном 0.

Команда проверки и установки реализована в системе IBM 370. Приращение и отрицательное приращение могут быть реализованы как неделимые операции чтения/изменения/записи и могут использоваться для выполнения преимущественно тех же функций, которые выполняет команда проверки и установки, почти в качестве прямой замены команды проверки и установки. Они являются более универсальными, поскольку способны осуществлять приращение и отрицательное приращение совместно используемых переменных как одну неделимую операцию, тогда как команда проверки и установки способна лишь устанавливать разряд. Процессор DEC VAX содержит команды неделимого приращения и отрицательного приращения.

Использование операций чтения/изменения/записи для создания критической секции сопряжено с рядом сложностей. В их число входят:

1. Вход в критическую секцию возможен самое большее для одного процесса за один раз. Если процесс входит в критическую секцию и дает сбой, происходит сбой всей системы, поскольку ни один другой процесс не может войти в критическую секцию.

2. Длительная и сложная для выполнения критическая секция является узким местом в мультипроцессорной системе. Поскольку только один процесс может за один раз входить в критическую секцию, если в эту же критическую секцию должны войти другие процессы, они должны ожидать, пока она не станет доступной, и они могут принуждаться к простою на протяжении этого времени. Желательным выходом является обновление совместно используемых переменных посредством последовательностей команд, которые выполняют операции чтения/изменения/записи вне критической секции. Это усовершенствование должно тщательно контролироваться с целью сохранения согласованности.

3. Поскольку критическая секция содержит множество команд, временной квант процесса может завершаться внутри критической секции, и этот процесс может приостанавливаться на длительное время, в течение которого управление процессором берут на себя другие процессы. На протяжении периода приостановки процесса, который отвечает за блокировку критической секции, ни один другой процесс не может входить в критическую секцию и обновлять совместно используемые переменные, управляемые этой критической секцией.

Для преодоления этих недостатков комплексные операции с совместно используемыми переменными могут быть реализованы в виде единой команды, выполняемой как одна неделимая операция. Например, процессор DEC VAX содержит неделимые команды постановки в очередь (ENQUEUE) и удаления из очереди (DEQUEUE), каждая из которых параллельно и как одна неделимая операция изменяет до четырех совместно используемых переменных и тем самым вносит изменения согласованно.

Если следовать этому подходу, проектировщик машин должен создавать неделимую команду для каждой отдельной операции с совместно используемыми переменными для каждого представления данных. Например, процессор DEC VAX содержит различные команды постановки в очередь и удаления из очереди для очередей с различными представлениями. Манипуляции с очередями с одним указателем на элемент должны выполняться одной из пар команд постановки в очередь/удаления из очереди, а манипуляции с очередями с двумя указателями на элемент должны выполняться отличающейся парой команд постановки в очередь/удаления из очереди.

Одним из недостатков в этом случае является необходимость для проектировщика машин предусматривать любую потенциальную неделимую операцию и любое потенциальное представление данных, поскольку каждая такая операция является в высшей степени специализированной. Этот подход не действует, поскольку программист не способен легко создавать и использовать специализированную неделимую операцию для каждого конкретного контекста и представления данных.

Соответственно, одной из важных задач, требующих решения, является способность создавать специализированные неделимые операции для комплексных обновлений совместно используемых переменных и выполнять эти неделимые операции, чтобы фактическое обновление происходило во время выполнения единой команды. За счет этого надежность и производительность мультипроцессорной системы не находятся под угрозой в случае сбоев или прерываний процесса, который отвечает за блокировку критической секции.

Частичное решение этой задачи достигается за счет применения команды сравнения и свопинга (Compare-and-Swap), реализованной в системе IBM 370. Команда сравнения и свопинга обеспечивает последний этап последовательности команд чтения/изменения/записи, который не защищен критической секцией и выполняет операцию записи только при определенных условиях, которые предположительно обеспечивают согласованность и неделимость. Для применения команды сравнения и свопинга сначала в процессе выполняются все действия последовательности чтения/изменения/записи посредством традиционных не являющихся неделимыми команд с целью обновления совместно используемой переменной за исключением операции окончательной записи обновленного значения совместно используемой переменной. Команда сравнения и свопинга применяется в процессе для выполнения операции окончательной записи. При выполнении команды сравнения и свопинга переменная повторно считывается из памяти, и ее хранящееся текущее значение сравнивается с копией предыдущего значения, которое хранится в регистре машины. Если значения совпадают, хранящееся значение переменной обновляется вновь вычисленным значением. Если копия предыдущего значения, хранящегося в регистре машины, и текущее значение, хранящееся в совместно используемой памяти, различаются, при выполнении команды сравнения и свопинга память не обновляется, и копия предыдущего значения, хранящегося в регистре машины, заменяется копией текущего значения переменной в совместно используемой памяти. При выполнении команды передается отчет о том, что произошло с кодом условия. Поскольку команда сравнения и свопинга сама выполняет действия последовательности чтения/изменения/записи, эти действия должны выполняться как одна неделимая операция, чтобы обеспечить правильность программы.

В основу команды сравнения и свопинга положена идея, согласно которой значение совместно используемой переменной может обновляться, если оно не было изменено ни одним другим процессом с момента его последнего считывания. Тем самым предположительно обеспечивается согласованное пове