Определение форматов трансляции для функций адаптера во время выполнения

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в облегчении предоставления адреса, используемого при доступе к системной памяти. Способ облегчения доступа к памяти включает осуществляемую с учетом выполнения команды Modify PCI Function Controls (MPFC), которая определяет дескриптор для определения положения адаптера, указатель для определения положения одной или нескольких таблиц трансляции и поле формата, которое указывает выбранный формат трансляции из множества доступных форматов трансляции, установку формата трансляции в выбранный формат трансляции, связанный с помощью дескриптора с адаптером; динамически выполняемое при поступлении запроса от адаптера получение указания формата трансляции, установленного командой MPFC, который должен использоваться при предоставлении адреса, используемого для доступа к памяти, при этом указанный формат трансляции предварительно регистрируют для адаптера, причем запрос имеет начальный адрес, который должен использоваться при предоставлении адреса, используемого для доступа к памяти; и определение адреса прямого доступа к памяти (DMA), используемого для доступа к памяти, на основании полученного формата трансляции и начального адреса, при этом начальный адрес сгенерирован адаптером; и сохранение или извлечение данных адаптера по адресу DMA. 3 н. и 11 з.п. ф-лы, 26 ил.

Реферат

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Это изобретение относится, в целом, к доступу к системной памяти в вычислительной среде, и в частности - к облегчению предоставления адреса, используемого при доступе к системной памяти.

Системная память доступна для запросов чтения и записи. Эти запросы могут исходить от различных компонентов вычислительной среды, включая центральные процессоры, а также адаптеры. Каждый запрос содержит адрес, который должен использоваться для доступа к системной памяти. Однако в некоторых случаях этот адрес не имеет однозначного соотношения с физическим местоположением в системной памяти. Следовательно, выполняется трансляция адреса.

Трансляция адреса используется, чтобы транслировать адрес, который предоставлен в одной форме, прямо непригодной для доступа к системной памяти, в другую форму, которая прямо используется для доступа к физическому местоположению в системной памяти. Например, виртуальный адрес, включаемый в запрос, предоставленный центральным процессором, транслируется в действительный или абсолютный адрес в системной памяти. В качестве дополнительного примера, адрес взаимосвязи периферийных компонентов (PCI), предоставленный в запросе от адаптера, может транслироваться в абсолютный адрес в системной памяти.

Публикация США №2007/0136554 А1, опубликованная 14 июня 2007 (под авторством Biran и др.), "Memory Operations in a Virtualized System," Виртуальная память выделяется и связывается с экземпляром операционной системы. Виртуальная память транслируется в один или более действительных адресов, причем один или более действительных адресов не требуют дальнейшей трансляции. Адаптер ввода-вывода делается видимым одному или более действительным адресам. Экземпляру операционной системы предоставляются один или более действительных адресов для осуществления доступа к виртуальной памяти, связанной с экземпляром операционной системы. Защита и трансляция адреса может выполняться адаптером ввода-вывода или экземпляром операционной системы.

В публикации США No. 2008/0091915 А1, опубликованной 17 апреля 2008 (под авторством Moerti и др.), "Apparatus and Method for Communicating With a Memory Registration Enabled Adapter Using Cached Address Translations", предоставляются устройство и способ для связи с адаптером с возможностью регистрации памяти, таким как канальный адаптер хоста InfiniBand™. С помощью устройства и способа службы драйверов устройств могут запускаться драйвером устройства для инициализации записей трансляции адреса в структуре данных трансляции адреса корневого комплекса. Адрес структуры данных буфера данных драйвера устройства и модификаторы регистрации могут передаваться драйвером устройства службам драйвера устройства. Службы драйвера устройства могут создавать записи структуры данных трансляции адреса в структуре данных трансляции адреса, связанной с корневым комплексом, и записи трансляции адреса регистрации памяти (MR) в структуре данных трансляции адреса MR адаптера. Структура данных трансляции адреса MR затем может использоваться операциями ввода-вывода, чтобы обходить структуру данных трансляции адреса, связанную с корневым комплексом.

Патент США №7493425, выданный 17 февраля 2009 (на имя Arndt и др.), "Method, System and Program Product for Differentiating Between Virtual Hosts on Bus Transactions and Associating Allowable Memory Access for an Input/Output Adapter that Supports Virtualization", описывает способ, систему и компьютерный программный продукт, который позволяет образу системы в рамках виртуального сервера с множества системных образов сохранять изолированность от других системных образов, одновременно прямо открывая часть своей связанной системной памяти, или всю системную память, разделенному адаптеру PCI без необходимости анализа и проверки каждой операции ввода-вывода компонентом, которому дается поручение менеджером LPAR.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Недостатки имеющегося уровня техники преодолеваются, и дополнительные преимущества обеспечиваются путем предоставления способа по п.1, а также соответствующей системы и компьютерного программного продукта для облегчения доступа к памяти.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Одна или несколько особенностей настоящего изобретения конкретно охарактеризованы и отдельно заявлены в формуле изобретения, следующей за описанием. Перечисленные выше и другие задачи, признаки и преимущества изобретения станут ясны из следующего далее подробного описания в сочетании с сопровождающими его чертежами, на которых:

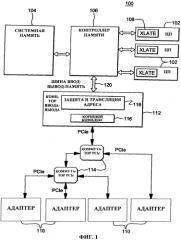

ФИГ.1 представляет собой изображение одного варианта осуществления вычислительной среды, которая должна включать и использовать одну или более особенностей настоящего изобретения;

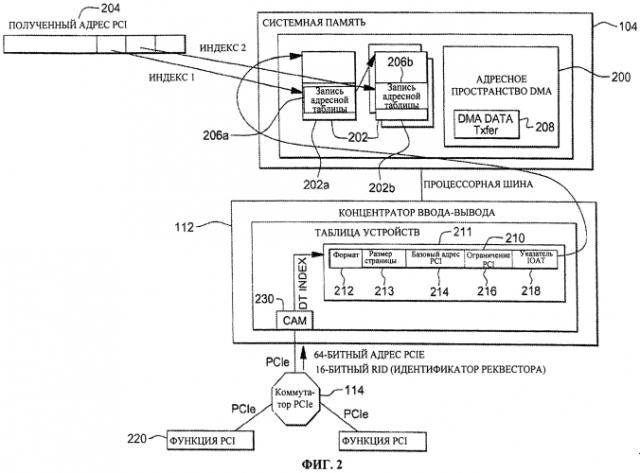

ФИГ.2 представляет собой изображение одного варианта осуществления дополнительных подробностей о системной памяти и концентраторе ввода-вывода, представленных на фиг.1, в соответствии с одной особенностью настоящего изобретения;

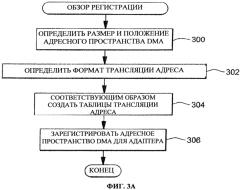

ФИГ.3А представляет собой изображение одного варианта осуществления обзора логической схемы для регистрации адресного пространства DMA (прямого доступа к памяти) для адаптера, в соответствии с одной особенностью настоящего изобретения;

ФИГ.3Б представляет собой изображение одного примера логической схемы для выбора формата трансляции, в соответствии с одной особенностью настоящего изобретения;

ФИГ.3В представляет собой изображение одного варианта осуществления различных подробностей регистрации адресного пространства DMA для адаптера, в соответствии с одной особенностью настоящего изобретения;

ФИГ.4 представляет собой изображение одного варианта осуществления логической схемы для обработки операции DMA, в соответствии с одной особенностью настоящего изобретения;

ФИГ.5А представляет собой изображение одного примера уровней трансляции, применяемых, когда весь адрес используется для индексации в таблицах трансляции адресов, чтобы транслировать адрес и осуществлять доступ к странице;

ФИГ.5Б представляет собой изображение одного примера уровней трансляции, применяемых, когда часть адреса игнорируется при индексации в таблицах трансляции адресов, в соответствии с одной особенностью настоящего изобретения;

ФИГ.5В представляет собой изображение примеров различных CPU DAT-совместимых форматов, используемых в соответствии с одной или более особенностями настоящего изобретения;

ФИГ.5Г представляет собой изображение примеров различных форматов трансляции расширенного адреса ввода-вывода, используемых в соответствии с одной или более особенностями настоящего изобретения;

ФИГ.6А - один из вариантов осуществления команды Modify PCI Function Controls, используемой согласно одной из особенностей настоящего изобретения;

ФИГ.6Б - один из вариантов осуществления поля, используемого командой Modify PCI Function Controls, проиллюстрированной на ФИГ.6А согласно одной из особенностей настоящего изобретения;

ФИГ.6В представляет собой изображение одного варианта осуществления другого поля, используемого командой Modify PCI Function Controls, представленной на ФИГ.6А, в соответствии с одной особенностью настоящего изобретения;

ФИГ.6Г представляет собой изображение одного варианта осуществления содержимого блока информации о функциях (FIB) в соответствии с одной особенностью настоящего изобретения;

ФИГ.7 - один из вариантов осуществления общего представления логики команды Modify PCI Function Controls согласно одной из особенностей настоящего изобретения;

ФИГ.8 представляет собой изображение одного варианта осуществления логической схемы, связанной с операцией регистрации параметров трансляции адресов ввода-вывода, которая может определяться командой Modify PCI Function Controls, в соответствии с одной особенностью настоящего изобретения;

ФИГ.9 представляет собой изображение одного варианта осуществления логической схемы, связанной с операцией отмены регистрации параметров трансляции адресов ввода-вывода, которая может определяться командой Modify PCI Function Controls, в соответствии с одной особенностью настоящего изобретения;

ФИГ.10 иллюстрирует один вариант осуществления компьютерного программного продукта, в котором содержится одна или несколько особенностей настоящего изобретения;

ФИГ.11 иллюстрирует один вариант осуществления хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.12 иллюстрирует дополнительный пример компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.13 иллюстрирует другой пример компьютерной системы, содержащей компьютерную сеть, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.14 иллюстрирует один вариант осуществления различных элементов компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.15А иллюстрирует один вариант осуществления исполнительного устройства компьютерной системы по ФИГ.14, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.15Б иллюстрирует один вариант осуществления устройства перехода компьютерной системы по ФИГ.14, в котором содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.15В иллюстрирует один вариант осуществления устройства загрузки/сохранения компьютерной системы по ФИГ.14, в которой содержится и используется одна или несколько особенностей настоящего изобретения; и

ФИГ.16 иллюстрирует один вариант осуществления эмулированной хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ

В соответствии с одной особенностью настоящего изобретения предоставляется функциональная возможность для облегчения доступа к памяти путем осуществления определения во время исполнения (например, во время трансляции адреса) того, какой формат трансляции был предварительно зарегистрирован для использования при предоставлении адреса, используемого при прямом доступе к системной памяти. В одном примере начальный адрес предоставляется функцией адаптера (называемый в данном документе адресом ввода-вывода), и формат трансляции, зарегистрированный для функции, используется, чтобы на основании изначально представленного адреса предоставлять адрес, который используется при доступе к системной памяти. Формат трансляции может указывать, например, тип таблиц(-ы) трансляции, который должен использоваться, что никакие таблицы трансляции не должны извлекаться или что трансляция может быть обойдена.

Далее будет описан один из вариантов осуществления вычислительной среды, в которой содержится и используется одна или несколько особенностей настоящего изобретения согласно ФИГ.1. В одном из примеров вычислительной средой 100 является сервер System z®, предлагаемый International Business Machines Corporation. Основой сервера System z® является z/Architecture®, предлагаемая International Business Machines Corporation. Подробности, касающиеся z/Architecture®, описаны в публикации IBM® под названием "z/Architecture-Principles of Operation", публикация IBM № SA22-7832-07 (февраль 2009 г.). IBM®, System z® и z/Architecture® являются зарегистрированными товарными знаками International Business Machines Corporation (Армонк, штат Нью-Йорк, США). Другие названия, используемые в заявке, могут являться зарегистрированными товарными знаками, товарными знаками или названиями продуктов International Business Machines Corporation или других компаний.

В одном из примеров вычислительная среда 100 содержит один или несколько центральных процессоров (ЦП) 102, связанных с системной памятью 104 (иначе называемой основной памятью) посредством контроллера 106 памяти. Для доступа к системной памяти 104 центральный процессор 102 выдает запрос чтения или записи, в котором содержится адрес, используемый для доступа к системной памяти. Поскольку адрес, содержащийся в запросе, обычно не может непосредственно использоваться для доступа к системной памяти, он транслируется в адрес, который может непосредственно использоваться для доступа к системной памяти. Адрес транслируется посредством механизма 108 трансляции (XLATE). Например, адрес транслируется из виртуального адреса в действительный или абсолютный адрес с использованием, например, динамической трансляции адресов (DAT).

Запрос, включая транслированный адрес, принимается контроллером 106 памяти. В одном из примеров контроллер 106 памяти состоит из аппаратного обеспечения и используется для арбитража при доступе к системной памяти и для обеспечения непротиворечивости памяти. Этот арбитраж осуществляется применительно к запросам, принимаемым от ЦП 102, а также запросам, принимаемым от одного или нескольких адаптеров 110. Подобно центральным процессорам адаптеры выдают в системную память 104 запросы на получение доступа к системной памяти.

В одном из примеров адаптером 110 является адаптер шины межсоединения периферийных компонентов (PCI) или адаптер на основе PCI Express (PCIe), содержащий одну или несколько функций PCI. Функция PCI подает запрос, который требует доступ к системной памяти. Запрос направляется на концентратор 112 ввода-вывода (например, концентратор PCI) через один или более коммутаторов 114 (например, коммутаторов PCI). В одном из примеров концентратор ввода-вывода состоит из аппаратного обеспечения, включающего один или несколько конечных автоматов.

Как используется в данном документе, термин "адаптер" включает любой тип адаптера (например, адаптер запоминающего устройства, сетевой адаптер, обрабатывающий адаптер, адаптер PCI, криптографический адаптер, другой тип адаптеров ввода-вывода, и т.п.) В одном из вариантов осуществления адаптер содержит одну функцию. Тем не менее, в других вариантах осуществления адаптер может содержать множество функций адаптера. В зависимости от того, содержит ли адаптер одну функцию или множество функций, применима одна или несколько особенностей настоящего изобретения. Кроме того, в примерах, представленных в данном документе, адаптер используется взаимозаменяемо с функцией адаптера (например, функцией PCI), если не указано иное.

Концентратор ввода-вывода содержит, например, корневой комплекс 116, который принимает запрос от коммутатора. Запрос содержит адрес ввода/вывода, который может быть нужно транслировать, и поэтому корневой комплекс предоставляет адрес на блок 118 защиты и трансляции адреса. Этот блок, например, представляет собой аппаратный блок, используемый для трансляции, при необходимости, адреса ввода-вывода в адрес, прямо используемый для доступа к системной памяти 104, как более подробно описывается ниже.

Запрос, инициированный на адаптере, включающий адрес (транслированный или начальный адрес, если трансляция не нужна), предоставляется на контроллер 106 памяти посредством, например, шины 120 ввод/вывод-память. Контроллер памяти выполняет свой арбитраж и направляет запрос с адресом в системную память в надлежащее время.

Дальнейшие подробности относительно системной памяти и концентратора ввода-вывода описываются со ссылкой на фиг.2. В этом варианте осуществления контроллер памяти не показан. Однако концентратор ввода-вывода может быть соединен с системной памятью прямо или через контроллер памяти. В одном примере системная память 104 включает одно или более адресных пространств 200. Адресное пространство - это конкретная часть системной памяти, которая была назначена для конкретного компонента вычислительной среды, такой как конкретный адаптер. В одном примере адресное пространство доступно посредством прямого доступа к памяти (DMA), инициированного адаптером, и поэтому адресное пространство в примерах, приведенных в данном документе, называется адресным пространством DMA. Однако в других примерах для доступа к адресному пространству прямой доступ к памяти не используется.

Кроме того, в одном примере системная память 104 содержит таблицы 202 трансляции адреса, используемые для трансляции адреса из адреса, который прямо не используется для доступа к системной памяти, в адрес, который используется прямо. В одном варианте осуществления имеется одна или более таблиц трансляции адреса, приписанных к адресному пространству DMA, и эти одна или более таблиц трансляции адреса настроены на основании, например, размера адресного пространства, к которому они приписаны, размера самих таблиц трансляции адреса и/или размера страницы (или другого блока памяти), к которой необходимо осуществлять доступ.

В одном примере имеется иерархия таблиц трансляции адреса. Например, как показано на ФИГ.2, имеется таблица 202а первого уровня (например, таблица сегментов), на которую указывает указатель 218 IOAT (описанный ниже), и вторая таблица 202b более низкого уровня (например, таблица страниц), на которую указывает запись 206а таблицы первого уровня. Один или более битов полученного адреса 204 используются для индексации в таблице 202а, чтобы определять положение конкретной записи 206а, которая указывает конкретную таблицу 202b более низкого уровня. Затем один или более других битов адреса 204 используются для определения положения конкретной записи 206b в этой таблице. В этом примере эта запись предоставляет адрес, используемый для определения положения верной страницы, а дополнительные биты в адресе 204 используются для определения конкретного положения 208 на странице для выполнения передачи данных. То есть, адрес в записи 206b и выбранные биты полученного адреса 204 PCI используются, чтобы предоставлять адрес, прямо используемый для доступа к системной памяти. Например, прямо используемый адрес образуется из соединения старших битов адреса в записи 206b (например, битов 63:12, в примере 4-Кб страницы) и выбранных младших битов из полученного адреса PCI (например, битов 11:0 для 4-Кб страницы).

В одном примере адресное пространство DMA конкретному адаптеру назначает операционная система. Это назначение выполняется посредством процесса регистрации, который вызывает инициализацию (например, посредством надежного программного обеспечения) записи 210 таблицы устройств для этого адаптера. Эта запись таблицы устройств находится в таблице 211 устройств, расположенной в концентраторе 112 ввода-вывода. Например, таблица 211 устройств находится в блоке защиты и трансляции адреса концентратора ввода-вывода.

В одном примере запись (DTE) 210 таблицы устройств содержит ряд полей наподобие следующих:

формат 212: Это поле содержит множество битов для указания различной информации, включая, например, формат трансляции адреса таблицы верхнего уровня таблиц трансляции адреса. CPU DAT-совместимый, расширенного адреса ввода-вывода, обходной, без извлечения, и т.п. Форм;

Размер 213 страницы: Это поле указывает размер страницы (или другого блока памяти), к которому должен осуществляться доступ;

базовый адрес 214 PCI и ограничение 216 PCI: Эти значения предоставляют диапазон, используемый для определения адресного пространства DMA и проверки допустимости полученного адреса (например, адреса PCI); и

Указатель IOAT (трансляции адреса ввода-вывода) 218: Это поле содержит указатель на таблицу трансляции адреса наивысшего уровня, используемую для адресного пространства DMA.

В других вариантах осуществления в DTE может содержаться больше, меньше информации или другая информация.

В одном варианте осуществления запись таблицы устройств, которая должна использоваться в конкретной трансляции, определяется с помощью идентификатора (RID) реквестора, расположенного в запросе, подаваемом функцией 220 PCI, связанной с адаптером (и/или частью адреса). ID реквестора (например, 16-битное значение, определяющее, например, номер шины, номер устройства и номер функции) включается в запрос, как и адрес ввода-вывода (например, 64-битный адрес PCIe), который должен использоваться для доступа к системной памяти. Запрос, включая RID и адрес ввода-вывода, предоставляется, например, на ассоциативную память (САМ) 230 посредством, например, коммутатора 114, который используется для предоставления индексного значения. Например, в САМ содержится множество записей, каждая из которых соответствует индексу в таблице устройств. Каждая запись в САМ содержит значение RID. Если, например, принятый RID соответствует значению, содержащемуся в записи в САМ, для определения местоположения записи в таблице устройств используется соответствующий индекс из таблицы устройств. То есть, выход САМ используется для индексации в таблице 211 устройств, чтобы определять положение записи 210 таблицы устройств. Если соответствия нет, полученный пакет отклоняется без осуществления доступа к системной памяти. (В других вариантах осуществления САМ или другой поиск не требуется, и RID используется в качестве индекса).

После этого, поля в записи таблицы устройств используются, чтобы убеждаться в допустимости адреса и настройки таблиц трансляции адреса. Например, поступающий в запросе адрес проверяется аппаратным обеспечением концентратора ввода-вывода (например, блоком защиты и трансляции адреса), чтобы убедиться, что он находится в пределах границ, определенных базовым адресом 214 PCI и ограничением 216 PCI, хранящимися в записи таблицы устройств, определенной с помощью RID запроса, предоставившего адрес. Это гарантирует, что адрес находится в пределах ранее зарегистрированного диапазона, для которого таблицы трансляции адреса настроены правильно.

В одном варианте осуществления, чтобы получить адрес системной памяти (т.е. адрес, прямо используемый для доступа к системной памяти), сначала выполняется процесс регистрации. Этот процесс регистрации регистрирует конкретное адресное пространство и, таким образом, связанные таблицы трансляции адреса, с конкретным реквестором, таким как конкретная функция адаптера. Один пример обзора этого процесса регистрации описывается со ссылкой на фиг.3А.

Обращаясь к фиг.3А, сначала на этапе 300 операционная система, выполняющаяся в одном из центральных процессоров, соединенных с системной памятью, определяет размер и местоположение адресного пространства, к которому должен осуществлять доступ адаптер. В одном примере размер адресного пространства определяется базовым адресом PCI и ограничением PCI, установленными операционной системой. Операционная система определяет основание и ограничение с помощью одного или более критериев. Например, если операционная система хочет, чтобы адреса PCI прямо отображались на виртуальные адреса ЦП, то база и ограничение устанавливаются таким образом. В еще одном примере, если желательным является дополнительное изолирование между адаптерами и/или образами операционной системы, то используемые адреса выбираются так, чтобы предоставлять ненакладывающиеся и раздельные адресные пространства. Местоположение также определяется операционной системой и основывается, например, на характеристиках адаптера.

Далее, как часть процесса регистрации, на этапе 302 осуществляется определение, какой формат трансляции адреса должен быть зарегистрирован для функции адаптера. То есть, осуществляется определение, какой формат должен использоваться для предоставления адресов для функции адаптера, которые прямо могут использоваться при доступе к системной памяти.

В соответствии с одной особенностью настоящего изобретения, доступно множество форматов трансляции адреса, и из этого множества форматов операционная система выбирает один формат для функции адаптера. Этот выбор основывается, например, на конфигурации адресных пространств, типе адаптера, и т.п. Различные возможные форматы включают:

а) Формат обхода, в котором трансляция адреса обходится. Этот формат может использоваться, когда адаптер, для которого выполняется регистрация, является надежным адаптером. Адаптер считается надежным адаптером, если, например, аппаратная конструкция адаптера является достаточно устойчивой к ошибкам и защищенной, так что адреса не могут быть искажены. Например, внутренне развитый адаптер, который предоставляет свои собственные механизмы трансляции и защиты, или адаптер, который управляется надежным аппаратно-программным обеспечением, может считаться надежным адаптером.

В контексте настоящего изобретения аппаратно-программное обеспечение содержит, например, микрокод, милликод и/или макрокод процессора. Оно содержит, например, команды аппаратного уровня и/или структуры данных, используемые при реализации высокоуровневого машинного кода. В одном варианте осуществления изобретения оно содержит, например, собственный код, который, как правило, поставляют как микрокод, который содержит выверенное программное обеспечение, или микрокод, характерный для базового аппаратного обеспечения, и управляет доступом операционной системы к аппаратному обеспечению системы.

С собственным подключением адаптеров ввода-вывода к, например. System z®, применяется трансляция адреса ввода-вывода (IOAT), чтобы обеспечивать защиту и изолирование доступа DMA к системной памяти адаптером. Однако существуют классы адаптеров, которые не нуждаются в таком дополнительном уровне защиты, включая описанные выше. Таким образом, для этих адаптеров может быть выбран формат обхода;

b) Формат без извлечения, в котором адрес, включенный в начальный запрос от адаптера, используется без извлечения каких-либо таблиц трансляции. Этот формат может быть выбран, когда память является непрерывной, размер страницы известен и адрес предназначен для ограниченной области (например, страницы в 4 Кб или 1 Мб), в которой не требуется извлечение никаких таблиц трансляции из системной памяти. Адрес, используемый для доступа к системной памяти (т.е. получающийся в результате адрес, когда выбирается формат без извлечения), получается из адреса указателя IOAT. Например, для страницы размером 4 Кб, младшие биты адреса PCI (например, биты 11:0) соединяются со старшими 52 битами указателя IOAT, чтобы получать итоговый адрес, используемый для доступа к системной памяти;

c) CPU DAT-совместимый формат, в котором таблицы трансляции, используемые для трансляции адресов ввода-вывода, совместимы с таблицами трансляции, используемыми для трансляций CPU DAT. To есть, должны использоваться таблицы трансляции адреса, которые подобны и совместимы с тем, что уже используется для динамической трансляции адреса ЦП. Это обеспечивает легкость использования для тех операционных систем, которые знакомы с использованием таблиц этих типов; позволяет разделять таблицы между ЦП и адаптером ввода-вывода; и придает определенной операционной системе (например, z/VM®) эффективность при обработке пространств DMA ее гостей с постраничной организацией. Доступны различные CPU DAT-совместимые форматы, как более подробно описывается ниже со ссылкой на фиг.5В;

d) Формат трансляции расширенных адресов ввода-вывода, в котором для трансляций адресов ввода-вывода используются таблицы трансляции расширенных адресов. При этом формате таблицы трансляции адреса предназначаются для операций ввода-вывода и могут быть больше по размеру, чем обычно используемые при трансляции адреса ЦП. Например, могут быть 1-Мб или даже более крупные таблицы страниц и/или другие таблицы трансляции. Кроме того, размеры различных уровней таблиц трансляции, включая таблицы страниц, могут отличаться друг от друга, и они могут отличаться от самих страниц. Увеличение традиционных размеров уменьшает транзакции шины и помогает улучшать кэширование трансляции ввода-вывода. Размер таблицы страниц и других таблиц трансляции, как и размер страницы, определяют, сколько уровней трансляции необходимо. Примеры различных форматов трансляции расширенных адресов ввода-вывода описываются более подробно ниже со ссылкой на фиг.5Г.

Один вариант осуществления процесса, выполняемого операционной системой для выбора формата трансляции адреса из множества доступных форматов трансляции адреса, который должен использоваться для функции адаптера, для которой выполняется регистрация, описывается со ссылкой на фиг.3Б. В одном примере, чтобы произвести этот выбор, операционная система рассматривает свои внутренние структуры, как она хочет адресовать память, тип адаптера, и т.п.

Обращаясь к фиг.3Б, в этом примере, на этапе запроса 310 сначала осуществляется определение, является ли адаптер, для которого выполняется регистрация, надежным адаптером. Это определение осуществляется, например, проверкой указания в структуре данных (например, хранящейся в памяти). Если операционная система решает, что адаптер является надежным, то на этапе 312 осуществляется дальнейшее определение, должна ли быть обойдена трансляция. Например, операционная система определяет, на основании, например, хранящегося индикатора, является ли приемлемым обход. Если операционная система решает, что трансляция должна быть обойдена, то на этапе 313 выбирается формат обхода, и адрес, предоставленный реквестором, прямо используется для доступа к системной памяти.

Возвращаясь к этапу запроса 310, если, однако, адаптер не является надежным адаптером, или если обход не должен быть выбран на этапе 312, то на этапе запроса 314 осуществляется дальнейшее определение, должен ли быть выбран формат без извлечения. Для этого выбора операционная система рассматривает, например, является ли память непрерывной, и размер страницы (или другого раздела памяти). Если конфигурация позволяет формат без извлечения, то при условии прохождения любых проверок на правильность, на этапе 316 выбирается формат без извлечения. Следовательно, получающийся в результате адрес запроса PCI получается прямо из адреса указателя IOAT.

Возвращаясь к этапу запроса 314, если формат без извлечения не выбран, то на этапе запроса 318 осуществляется дальнейшее определение, должен ли запрос использовать таблицы трансляции адресов CPU DAT-совместимости. И снова операционная система рассматривает свои структуры и адресуемость, принимая решение, хочет ли она CPU DAT-совместимый формат. Если он является желаемым форматом, и при условии прохождения любых проверок на правильность, на этапе 320 выбирается CPU DAT-совместимый формат. В частности, в этом примере, один CPU DAT-совместимый формат выбирается из одного или более доступных форматов, которые описываются ниже.

Однако если CPU DAT-совместимость не выбрана, то на этапе запроса 322 осуществляется дальнейшее определение, является ли желательным формат трансляции расширенных адресов ввода-вывода. То есть, снова, принимается решение на основании, например, структур, которые должны использоваться, и адресации памяти. Если является желательным формат трансляции расширенных адресов ввода-вывода, то при условии прохождения любых проверок на правильность, на этапе 324 выбирается формат трансляции расширенных адресов ввода-вывода. В частности, в этом примере, формат трансляции расширенных адресов ввода-вывода выбирается из одного или более доступных форматов, как описывается ниже.

Однако если на все эти запросы получается отрицательный ответ, то на этапе 326 конкретный формат выбирается операционной системой от имени реквестора. Например, может выбираться формат по умолчанию. Этот формат по умолчанию может быть CPU DAT-совместимым форматом или форматом трансляции расширенных адресов ввода-вывода, или даже другим форматом, таким как таблицы трансляции адреса, которые установлены только для ввода-вывода, но ближе связаны с таблицами формата CPU DAT. Существует множество вариантов. Кроме того, хотя в этом примере запросы, представленные на фиг.3Б расположены в конкретном порядке, в других примерах они могут быть в отличающихся порядках.

Согласно ФИГ.3А, впоследствии, при условии, что таблицы трансляции адреса необходимы, на этапе 304 создаются одна или более таблиц трансляции адреса, чтобы покрывать это адресное пространство DMA. В одном примере создание включает построение таблиц и размещение надлежащих адресов в табличных записях. В качестве примера, одна из таблиц трансляции адреса является таблицей 4-Кб страниц, имеющей 512 64-битных записей, и каждая запись включает адрес 4-Кб страницы, совместимый с назначенным адресным пространством.

После этого на этапе 306 адресное пространство DMA регистрируется для адаптера, как более подробно описывается со ссылкой на фиг.3В. В этом примере предполагается, что имеется одна функция PCI на адаптер, а поэтому один ID реквестора на адаптер. Эта логика выполняется, например, центральным процессором, связанным с системной памятью, с учетом запроса операционной системы.

Обращаясь к фиг.3В, сначала, в одном варианте осуществления, на этапе 350 выбирается доступная запись таблицы устройств, которая должна соответствовать ID реквестора адаптера. То есть, ID реквестора будет использоваться для определения положения записи таблицы устройств.

Дополнительно, базовый адрес PCI и ограничение PCI на этапе 352 сохраняются в записи таблицы устройств. Кроме того, на этапе 354 формат таблицы трансляции адреса наивысшего уровня сохраняется в поле формата записи таблицы устройств. Например, поле формата включает множество битов, и один или более из этих битов указывают формат таблицы наивысшего уровня и выбранный формат трансляции адреса (например, уровня сегментов, CPU DAT-совместимый). В еще одном варианте осуществления один или более битов указывают наивысший уровень, и один или более других битов указывают определенный формат трансляции (например, обходной, без извлечения, конкретный CPU DAT-совместимый формат, конкретный формат трансляции расширенного адреса ввода-вывода, и т.п.).

Дополнительно, на этапе 356 указатель трансляции (IOAT) адреса ввода-вывода, используемый, чтобы указывать на таблицу трансляции адреса наивысшего уровня (или страницу, в случае без извлечения), если имеется, сохраняется в записи таблицы устройств. На этом регистрация завершается.

С учетом выполнения регистрации, адресное пространство DMA и соответствующие таблицы трансляции адреса, если имеются, готовы к использованию, также как и запись таблицы устройств. Подробности относительно обработки запроса, поданного реквестором, таким как функция адаптера, для доступа к системной памяти описываются со ссылкой на фиг.4. Обработка, описанная ниже, выполняется концентратором ввода-вывода. В одном примере логику выполняет блок защиты и трансляции адреса концентратора ввода-вывода.

В одном варианте осуществления сначала на этапе 400 на концентраторе ввода-вывода получается запрос DMA. Например, функция PCI подает запрос, который направляется на концентратор PCI посредством, например, коммутатора PCI. Используя в запросе ID реквестор, на этапе 402 определяется положение соответствующей записи таблицы устройств. После этого на этапе запроса 404 осуществляется определение, является ли запись таблицы устройств допустимой. В одном примере допустимость определяется проверкой бита допустимости в самой записи. Этот бит устанавливается, например, с учетом выполнения запроса функции активации операционной системой. Если активирован, бит устанавливается, например, в единицу (т.е., допустимый); иначе он остается нулевым (т.е., недопустимым). В еще одном примере бит может устанавливаться, когда завершается процесс регистрации.

Если запись таблицы устройств является недопустимой, на этапе 405 предоставляется ошибка. Иначе на этапе запроса 406 осуществляется дальнейшее определение, является ли адрес PCI, предоставленный в запросе, меньшим, чем базовый адрес PCI, хранящийся в записи таблицы устройств. Если да, то адрес находится за пределами допустимого диапазона, и на этапе 407 предоставляется ошибка. Однако если адрес PCI больше базового адреса или равен ему, то на этапе запроса 408 осуществляется другое определение, больше ли адрес PCI, чем предельное значение PCI в записи таблицы устройств. Если адрес PCI больше, чем ограничение, то на этапе 409 снова предоставляется ошибка, поскольку адрес находится за пределами допустимого диапазона. Однако если адрес находится в пределах допустимого диапазона, то обработка продолжается.

В одном примере на этапе запроса 410 осуществляется определение, указывает ли формат трансляции адреса, определенный в записи таблицы устройств, обходную трансляцию. Если да, то адрес передается прямо на контроллер памяти по шине ввода-вывода для осуществления доступа к памяти без какого-либо извлечения записей трансляции. На этапе 426 концентратор вв