Способ и компьютерная система для выполнения команды запуска субканала в вычислительной среде

Иллюстрации

Показать всеИзобретение относится к области вспомогательных запоминающих устройств вычислительной среды. Техническим результатом является повышение эффективности управления вспомогательными запоминающими устройствами. Раскрыт способ выполнения команды запуска субканала в вычислительной среде, содержащей основное запоминающее устройство и твердотельное запоминающее устройство, при этом указанный способ включает: с учетом определения того, что субканал, идентифицированный командой запуска субканала, является субканалом перемещения асинхронных данных (ADM), выполнение: получения блока запроса операции из основного запоминающего устройства, при этом блок запроса операции содержит адрес блока операции; получения блока операции из основного запоминающего устройства на основании адреса блока операции, при этом блок операции состоит из блока запроса, блока ответа и одного или более блоков (MSB) спецификации первого перемещения, причем блок запроса содержит поле счетчика MSB, содержащее значение, указывающее число одного или более блоков MSB, которые блок операции содержит и на которые ссылается, причем блок ответа сконфигурирован содержать условия исключительных ситуаций, причем каждый блок спецификации перемещения сконфигурирован содержать поле кода операции, поле счетчика блоков, поле адреса основного запоминающего устройства для адресации основного запоминающего устройства, поле адреса твердотельного запоминающего устройства для адресации твердотельного запоминающего устройства, поле размера блока и поле флагов; получения блока спецификации перемещения из одного или более блоков спецификации перемещения; определения на основании кода операции в полученном блоке спецификации перемещения операции, которую полученный блок спецификации перемещения сконфигурирован выполнять на блоках твердотельного запоминающего устройства; на основании блока спецификации перемещения запуска операции на блоках твердотельного запоминающего устройства, связанных с адресом твердотельного запоминающего устройства поля адреса твердотельного запоминающего устройства; и с учетом, по меньшей мере, запуска операции и обнаружения условия исключительной ситуации сохранения информации в блоке ответа, причем блок ответа содержит поле флагов исключительной ситуации, поле достоверности поля, поле неверного адреса MSB, поле неверного адреса косвенного адресного слова данных (AIDAW), поле неверного адреса основного запоминающего устройства и поле неверного адреса твердотельного запоминающего устройства, при этом информация касается одной или более исключительных ситуаций, являющихся результатом операции, причем одна или более исключительных ситуаций относятся по меньшей мере к одному из: основному запоминающему устройству, связанному с адресом основного запоминающего устройства из поля адреса основного запоминающего устройства; твердотельному запоминающему устройству, связанному с адресом твердотельного запоминающего устройства из поля адреса твердотельного запоминающего устройства; или полученного блока спецификации перемещения, причем информация содержит признак исключительной ситуации и дополнительную информацию, относящуюся к исключительной ситуации, при этом дополнительная информация определяет одну или более исключительных ситуаций адресации. 2 н. и 6 з.п. ф-лы, 45 ил.

Реферат

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

[0001] Одна или несколько особенностей настоящего изобретения относятся, в общем, к вспомогательному запоминающему устройству вычислительной среды и, в частности, к особенностям управления вспомогательным запоминающим устройством.

[0002] Вычислительная среда может содержать основное запоминающее устройство (также известное как основная память), а также вспомогательное запоминающее устройство. Основное запоминающее устройство - это запоминающее устройство, доступное для процессора, которое является произвольно адресуемым посредством, например, абсолютного адреса. Основное запоминающее устройство рассматривается как запоминающее устройство с быстрой выборкой по сравнению с таким вспомогательным запоминающим устройством, как запоминающие устройства прямого доступа (DASD) или твердотельное запоминающее устройство. Кроме того, адресация основного запоминающего устройства считается более простой, чем адресация DASD или твердотельного запоминающего устройства.

[0003] Твердотельное запоминающее устройство, которое представляет собой объем внешнего запоминающего устройства снаружи классического основного запоминающего устройства, обеспечивает более быстрый доступ, чем запоминающие устройства прямого доступа. В отличие от DASD, твердотельное запоминающее устройство, как правило, не реализовано как вращающиеся диски с механической рукой, но, вместо этого, - как немеханические твердотельные части. Как правило, твердотельное запоминающее устройство реализовано как группы твердотельных устройств, соединенные с вычислительной системой посредством нескольких адаптеров ввода-вывода (I/O), которые применяют для отображения технологии устройства ввода-вывода на шину памяти центрального процессора (процессоров).

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

[0004] На основе изучения недостатков уровня техники предложены способ и система для выполнения команды запуска субканала (далее - Start Subchannel) в вычислительной среде, содержащей основное запоминающее устройство и твердотельное запоминающее устройство. Способ, осуществляемый, в частности, посредством компьютерного программного продукта, содержащего машиночитаемую запоминающую среду, считываемую устройством обработки данных и хранящую соответствующие команды для выполнения устройством обработки данных, включает, например, с учетом определения того, что субканал, идентифицируемый командой Start Subchannel, представляет собой субканал асинхронного перемещения данных (ADM), выполнение: получения блока запроса операций из основного запоминающего устройства, где блок запроса операций содержит адрес блока операции; получения блока операции из основного запоминающего устройства на основании адреса блока операции, где блок операции состоит из блока запроса, блока ответа и одного или нескольких первых блоков спецификации перемещения (MSB), где блок запроса содержит поле счетчика блоков MSB, содержащее значение, которое указывает число одного или нескольких блоков MSB, которые блок операции содержит и на которые ссылается, где блок ответа сконфигурирован для содержания исключительных ситуаций, где каждый блок спецификации перемещения сконфигурирован содержать поле кода операции, поле счетчика блоков, поле адреса основного запоминающего устройства для адресации основного запоминающего устройства, поля адреса памяти твердотельного запоминающего устройства для адресации твердотельного запоминающего устройства, поле размера блоков и поле флагов; получения блока спецификации перемещения одного или нескольких блоков спецификации перемещения; на основе кода операции в полученном блоке спецификации перемещения определения операции, для осуществления которой на блоках твердотельного запоминающего устройства сконфигурирован полученный блок спецификации перемещения; на основе блока спецификации перемещения инициирования операции на блоках твердотельного запоминающего устройства, связанных с адресом памяти твердотельного запоминающего устройства поля адреса памяти твердотельного запоминающего устройства; и с учетом, по меньшей мере, инициирования операции и обнаружения исключительной ситуации, сохранения информации в блоке ответа, где блок ответа содержит поле флагов исключительной ситуации, поле достоверности поля, поле неверного адреса MSB, поле неверного адреса косвенного адресного слова данных (AIDAW), поле неверного адреса основного запоминающего устройства и поле неверного адреса твердотельного запоминающего устройства, где информация касается одной или более исключительных ситуаций, являющихся результатом операции, где одна или несколько исключительных ситуаций относятся по меньшей мере к одному из следующего: основному запоминающему устройству, связанному с адресом основного запоминающего устройства из поля адреса основного запоминающего устройства; твердотельному запоминающему устройству, связанному с адресом твердотельного запоминающего устройства из поля адреса твердотельного запоминающего устройства; или полученного блока спецификации перемещения, причем информация содержит признак исключительной ситуации и дополнительную информацию, относящуюся к исключительной ситуации, при этом дополнительная информация определяет одну или более исключительных ситуаций адресации.

[0005] В изобретении также описаны и заявлены способы и системы, в которых применяют одну или несколько особенностей настоящего изобретения. Кроме того, в данном изобретении также описаны и могут быть заявлены сервисы, относящиеся к одной или нескольким особенностям настоящего изобретения.

[0006] Дополнительные признаки и преимущества реализуются посредством методик согласно настоящему изобретению. Другие варианты осуществления и признаки изобретения подробно описаны в настоящем изобретении и считаются частью заявленного изобретения.

КРАТКОЕ ОПИСАНИЕ ГРАФИЧЕСКИХ МАТЕРИАЛОВ

[0007] Варианты осуществления изобретения буду описаны только в виде примера с отсылкой к сопроводительным графическим материалам, на которых:

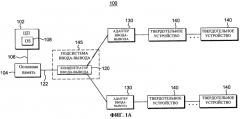

ФИГ.1A иллюстрирует один вариант осуществления вычислительной среды, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

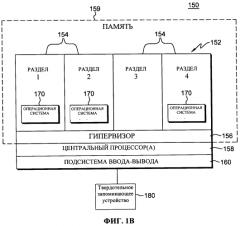

ФИГ.1B иллюстрирует другой вариант осуществления вычислительной среды, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

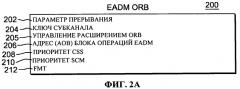

ФИГ.2A иллюстрирует один вариант осуществления блока запроса операций расширенной схемы асинхронного перемещения данных, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.2B иллюстрирует один вариант осуществления блока запроса операций расширенной схемы асинхронного перемещения данных, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.2C иллюстрирует один вариант осуществления блока запроса операций расширенной схемы асинхронного перемещения данных, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.2D иллюстрирует один вариант осуществления блока ответа расширенной схемы асинхронного перемещения данных, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.2E иллюстрирует один вариант осуществления блока спецификации перемещения расширенной схемы асинхронного перемещения данных, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.2F иллюстрирует один вариант осуществления косвенного адресного слова данных расширенной схемы асинхронного перемещения данных, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.3A иллюстрирует один вариант осуществления команды Start Subchannel, используемой согласно одной из особенностей настоящего изобретения;

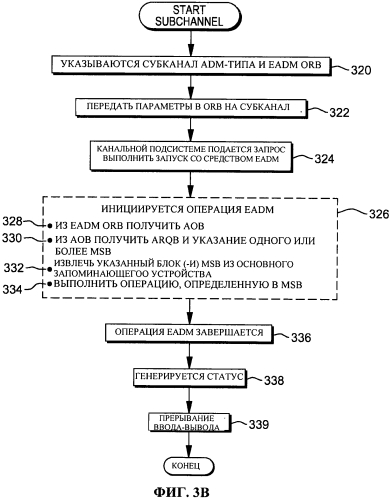

ФИГ.3B иллюстрирует один вариант осуществления логики, связанной с командой Start Subchannel, согласно одной из особенностей настоящего изобретения;

ФИГ.3C иллюстрирует один вариант осуществления команды Clear Subchannel, используемой согласно одной из особенностей настоящего изобретения;

ФИГ.3D иллюстрирует один вариант осуществления команды Test Subchannel, используемой согласно одной из особенностей настоящего изобретения;

ФИГ.3E иллюстрирует один вариант осуществления команды Modify Subchannel, используемой согласно одной из особенностей настоящего изобретения;

ФИГ.3F иллюстрирует один вариант осуществления команды Store Subchannel, используемой согласно одной из особенностей настоящего изобретения;

ФИГ.4A иллюстрирует один вариант осуществления блока информации о субканале расширенной схемы асинхронного перемещения данных, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.4B иллюстрирует один вариант осуществления управляющего слова управления трактами расширенной схемы асинхронного перемещения данных, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.4C иллюстрирует один вариант осуществления слова статуса субканала, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.4D иллюстрирует один вариант осуществления расширенного слова статуса расширенной схемы асинхронного перемещения данных, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.5A иллюстрирует один вариант осуществления блока запроса сохранения информации о твердотельном запоминающем устройстве, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.5B иллюстрирует один вариант осуществления блока ответа сохранения информации о твердотельном запоминающем устройстве, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.5C иллюстрирует один вариант осуществления записи списка адресов запоминающего устройства, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.5D иллюстрирует один вариант осуществления логики, связанной с командой Store Storage Class Memory Information, согласно одной из особенностей настоящего изобретения;

ФИГ.6A иллюстрирует один пример диаграммы состояний, отображающей различные состояния твердотельного запоминающего устройства, согласно одной из особенностей настоящего изобретения;

ФИГ.6B иллюстрирует один вариант осуществления диаграммы состояний, показывающей состояния операций и состояния данных, согласно одной из особенностей настоящего изобретения;

ФИГ.7A иллюстрирует один вариант осуществления блока запроса конфигурирования твердотельного запоминающего устройства, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.7B иллюстрирует один вариант осуществления блока ответа конфигурирования твердотельного запоминающего устройства, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.7C-7D иллюстрируют один вариант осуществления логики, связанной с командой Configure Storage Class Memory, используемой согласно одной из особенностей настоящего изобретения;

ФИГ.8A иллюстрирует один пример блока ответа на уведомление, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.8B иллюстрирует один вариант осуществления блока запроса сохранения информации о событиях, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.8C иллюстрирует один вариант осуществления блока ответа сохранения информации о событиях, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.9A иллюстрирует один вариант осуществления блока запроса деконфигурирования твердотельного запоминающего устройства, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.9B иллюстрирует один вариант осуществления записи списка запроса приращений твердотельного запоминающего устройства, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.9C иллюстрирует один вариант осуществления блока ответа деконфигурирования памяти твердотельного запоминающего устройства, используемого согласно одной из особенностей настоящего изобретения;

ФИГ.9D-9E иллюстрируют один вариант осуществления логики, связанной с командой Deconfigure Storage Class Memory, используемой согласно одной из особенностей настоящего изобретения;

ФИГ.10 иллюстрирует один вариант осуществления компьютерного программного продукта, в котором содержится одна или несколько особенностей настоящего изобретения;

ФИГ.11 иллюстрирует один вариант осуществления хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.12 иллюстрирует дополнительный пример компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.13 иллюстрирует другой пример компьютерной системы, содержащей компьютерную сеть, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.14 иллюстрирует один вариант осуществления различных элементов компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.15A иллюстрирует один вариант осуществления исполнительного устройства компьютерной системы по ФИГ.14, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.15B иллюстрирует один вариант осуществления устройства перехода компьютерной системы по ФИГ.14, в котором содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.15C иллюстрирует один вариант осуществления устройства загрузки/сохранения компьютерной системы по ФИГ.14, в которой содержится и используется одна или несколько особенностей настоящего изобретения; и ФИГ.16 иллюстрирует один вариант осуществления эмулированной хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ

[0008] Согласно одному или нескольким вариантам осуществления изобретения для твердотельного запоминающего устройства предусмотрена абстракция, которая скрывает подробности реализации твердотельного запоминающего устройства от программы (например, от операционной системы) и предусматривает стандартный программный интерфейс канала для осуществления определенных действий, таких как управление перемещением данных между основным запоминающим устройством и твердотельным запоминающим устройством.

[0009] В одном примере предусмотрено средство, называемое средством расширенного асинхронного перемещения данных (EADM), которое позволяет программам запрашивать передачу блоков данных между основным запоминающим устройством и твердотельным запоминающим устройством, а также запрашивать другие операции. Ниже подробно описываются особенности данного средства.

[0010] Также связанным со средством EADM является необязательное средство, называемое средством освобождения EADM. Средство освобождения EADM, если оно установлено, предоставляет программе средства для указания того, что она больше не нуждается в хранении данных в одном или нескольких блоках твердотельного запоминающего устройства. То, поддерживается ли операция освобождения для всех блоков твердотельного запоминающего устройства или только для подмножества твердотельных запоминающих устройств, зависит от модели.

[0011] Когда блок твердотельного запоминающего устройства освобожден, программа может передавать в блок новые данные, в противном случае последующие запросы на передачу данных из блока в основное запоминающее устройство будут неудачными.

[0012] Один вариант осуществления вычислительной среды, который содержит и/или использует одну или несколько особенностей настоящего изобретения, описывается с отсылкой к ФИГ.1А. Вычислительная среда 100 основана, например, на архитектуре z/Architecture® предлагаемой International Business Machines Corporation (IBM®), Армонк, штат Нью-Йорк. Один вариант осуществления архитектуры z/Architecture® IBM опи® z/Architecture Principles of Operation», IBM Publication No. SA22-7832-08, August, 2010 г., которая ссылкой полностью включена в настоящее описание. В одном примере вычислительная среда, основанная на архитектуре z/Architecture® zEnterprise 196 (z196), предлагаемую International Business Machines Corporation. IBM® и z/Architecture® являются зарегистрированными товарными знаками, и zEnterprise 196 и z196 являются товарными знаками International Business Machines Corporation, Армонк, Нью-Йорк, США. Другие названия, используемые в заявке, могут являться зарегистрированными товарными знаками, товарными знаками или названиями продуктов International Business Machines Corporation или других компаний.

[0013] В одном примере вычислительная среда 100 содержит один или несколько центральных процессоров 102, связанных с основной памятью 104 посредством одной или нескольких шин 106. Один или несколько центральных процессоров могут выполнять операционную систему 108, такую как операционная система z/OS® International Business Machines Corporation. В других примерах один или несколько центральных процессоров могут выполнять другие операционные системы или не выполнять ни одной операционной системы. z/OS® является зарегистрированным товарным знаком International Business Machines Corporation, Армонк, Нью-Йорк, США.

[0014] Центральные процессоры 102 и основная память 104 также могут быть связаны с концентратором 120 ввода-вывода посредством одного или нескольких соединений 122 (например, шин или других соединений). Концентратор ввода-вывода обеспечивает соединяемость с одним или несколькими адаптерами 130 ввода-вывода, которые дополнительно связаны с одним или несколькими твердотельными устройствами 140. Адаптеры и твердотельные устройства представляют собой реализацию твердотельного запоминающего устройства (например, флэш-памяти). Концентратор ввода-вывода является частью подсистемы 145 ввода-вывода, содействующей одной или нескольким особенностям одного варианте осуществления изобретения.

[0015] В одном дополнительном варианте осуществления изобретения, как проиллюстрировано на ФИГ.1B, вычислительная среда 150 может содержать центральный процессорный комплекс (CPC) 152, который основан на архитектуре z/Architecture® предлагаемой International Business Machines Corporation. Центральный процессорный комплекс 152 содержит, например, одно или несколько разделов 154, гипервизор 156, один или несколько центральных процессоров 158 и один или несколько компонентов подсистемы 160 ввода-вывода. В данном примере разделы 154 представляют собой логические разделы (например, LPAR), каждый из которых содержит набор аппаратных ресурсов системы, виртуализированный как отдельная система.

[0016] Каждый логический раздел 154 способен функционировать как отдельная система. То есть каждый логический раздел может быть независимо переустановлен, при необходимости, в исходном положении в него может быть загружена операционная система или другой управляющий код, и он может работать с разными программами. Оказывается, что операционная система, или прикладная программа, выполняемая в логическом разделе, имеет доступ к системе во всей полноте, но, на самом деле, доступной является только ее часть. Сочетание аппаратного обеспечения и лицензионного внутреннего кода (LIC), называемого аппаратно-программным обеспечением, защищает программу в одном логическом разделе от создания помех какой-либо программы в другом логическом разделе. Это позволяет нескольким различным логическим разделам работать на одном или нескольких физических процессорах способом квантования времени. Используемое в данном описании программно-аппаратное обеспечение содержит, например, микрокод, милликод и/или макрокод процессора (или сущности, осуществляющей обработку данных). Оно содержит, например, команды аппаратного уровня и/или структуры данных, используемые при реализации высокоуровневого машинного кода. В одном варианте осуществления изобретения оно содержит, например, собственный код, который, как правило, поставляют как микрокод, который содержит выверенное программное обеспечение, или микрокод, характерный для базового аппаратного обеспечения, и управляет доступом операционной системы к аппаратному обеспечению системы.

[0017] В данном примере некоторые из логических разделов содержат резидентную операционную систему (OS) 170, которая может отличаться для одного или нескольких логических разделов. В одном варианте осуществления изобретения, по меньшей мере, один логический раздел выполняет операционную систему z/OS® International Business Machines Corporation, Армонк, Нью-Йорк.

[0018] Логические разделы 154 администрируются гипервизором 156, который реализован посредством аппаратно-программного обеспечения, выполняемого на центральных процессорах 158. Каждый из логических разделов 154 и гипервизор 156 содержат одну или несколько программ, постоянно находящихся в соответствующих частях основной памяти 159, связанного с центральными процессорами. Одним примером гипервизора 156 является Processor Resource/Systems Manager (PR/SM™), предлагаемый International Business Machines Corporation, Армонк, Нью-Йорк.

[0019] Центральные процессоры 158 представляют собой физические процессорные ресурсы, которые выделены логическими разделами. Например, логический раздел 154 содержит один или несколько логических процессоров, каждый из которых отображает весь выделенный разделу физический процессорный ресурс 158 или его часть. Логические процессоры конкретного раздела 154 могут быть или выделены разделу, и тогда базовый процессорный ресурс является зарезервированным для этого раздела; или они могут использоваться совместно с другим разделом, и тогда базовый процессорный ресурс потенциально является доступным и для другого раздела.

[0020] Подсистема 160 ввода-вывода (только часть которой проиллюстрирована) обеспечивает соединяемость с твердотельным запоминающим устройством 180. В данном примере для твердотельного запоминающего устройства предусмотрено адресное пространство, которое представляет память как линейную, скрывающую от программы подробности физической реализации. В одном примере, для твердотельного запоминающего устройства существует одно адресное пространство в масштабе системы, но с точки зрения конфигурации (например, LPAR или в другом варианте осуществления изобретения виртуализированного гостя) существует одно адресное пространство, которое для каждой конфигурации системы заполняется приращениями твердотельного запоминающего устройства. Адресное пространство твердотельного запоминающего устройства является отдельным и не зависящим от адресного пространства основного запоминающего устройства.

[0021] В одном частном примере архитектуры z/Architecture®, подсистема ввода-вывода содержит канальную подсистему, которая не только направляет поток информации не только между периферийными блоками управления (и устройствами) вводом-выводом и основной памятью, но также и между твердотельным запоминающим устройством и основной памятью. Однако подсистема ввода-вывода может представлять собой и иную систему, чем канальная подсистема.

[0022] В случае канальной подсистемы для осуществления операций EADM используют субканалы. Эти субканалы называются субканалами, относящимися к типу схемы асинхронного перемещения данных (ADM), и они связаны с операциями EADM, а не с устройствами ввода-вывода, как другие субканалы, относящиеся к типу ввода-вывода. Субканал ADM-типа не содержит ни номер устройства, ни информацию о канальном тракте. Количество субканалов ADM-типа, предусматриваемых для некоторой конфигурации, зависит от модели. Субканалы ADM-типа адресуются словом идентификации подсистемы (SID).

[0023] Субканалы ADM-типа используют средством расширенного асинхронного перемещения данных, которое представляет собой одно из расширений канальной подсистемы. Как описывается в данном описании, средство EADM позволяет программе запрашивать передачу блоков данных между основным запоминающим устройством и твердотельным запоминающим устройством, а также осуществление других операций, таких как сброс блока твердотельного запоминающего устройства или освобождение блока твердотельного запоминающего устройства. В одном варианте осуществления изобретения, когда средство EADM установлено:

[0024] * Предусмотрен один или несколько субканалов ADM-типа, которые используют для операций EADM.

[0025] * Операции EADM указаны указанным блоком операций EADM (АОВ). АОВ содержит блок запроса EADM (ARQB) и блок ответа EADM (ARSB) и указывает список блоков спецификации перемещения EADM (MSB). Для операции перемещения блоки MSB содержат такую информацию о блоках данных, которые подлежат перемещению, как размер блоков, исходное местоположение и конечное местоположение блоков, и направление перемещения данных.

[0026] Максимальное количество блоков MSB, которое может указываться посредством AOB, зависит от модели. Максимальное число блоков, которое MSB может указывать, как подлежащие перемещению или операциям на них, также зависит от модели.

[0027] * Программа инициирует операции EADM, выдавая команду Start Subchannel, которая указывает субканал ADM-типа и блок запроса операций (ORB) EADM. В свою очередь, EADM ORB указывает AOB. Команда передает содержимое EADM ORB в указанный субканал.

[0028] * Когда для инициирования операций EADM выдается команда Start

Subchannel, канальная подсистема асинхронно осуществляет указанную операцию.

[0029] * Программа следит, что твердотельное запоминающее устройство при зависящем от модели минимальном размере блоков кажется параллельной по блокам. Эта зависящая от модели величина называется размером параллельности блоков SCM.

[0030] * Когда операции EADM завершены, прерывание ввода-вывода для субканала ADM-типа, на котором были инициированы операции, делается ожидающим программу.

[0031] EADM ORB содержит спецификацию ключа субканала и адрес AOB, подлежащего использованию. AOB указывается, например, на границе 4 Кбайт и может иметь размер до 4 Кбайт. Если требуется больше блоков MSB, чем может поместиться в 4 Кбайта AOB, AOB может указывать список блоков MSB, который расширяется на дополнительные области хранения путем использования блоков MSB, которые вместо указания области памяти, подлежащей использованию для передачи данных, указывают адрес следующего MSB в списке.

[0032] Первая операция EADM запускается канальной подсистемой, использующей информацию в указанном EADM ORB и ARQB в указанном AOB для извлечения MSB. MSB содержит информацию, которая указывает операцию EADM, подлежащую обработке, и управляет этой операцией.

[0033] Каждая операция EADM отображается одним MSB. MSB может указывать, например, передачу блоков данных из основного запоминающего устройства в твердотельное запоминающее устройство; передачу блоков данных из твердотельного запоминающего устройства в основное запоминающее устройство; сброс блоков твердотельного запоминающего устройства; и освобождение блоков твердотельного запоминающего устройства.

[0034] Если блоки, подлежащие передаче, не являются непрерывными в основном запоминающем устройстве, может использоваться новый MSB, или MSB может использовать косвенную адресацию путем определения списка косвенных адресных слов данных (AIDAW) для указания блоков, не являющихся непрерывными.

[0035] Так как MSB определяет передачу данных только в одном направлении, в случае, когда происходит изменение в направлении передачи, следует использовать новый MSB.

[0036] Окончание операции EADM обычно указывается комбинированными ситуациями статусов окончания работы канала и окончания работы устройства. Указанная комбинация статусов отображает комбинацию первичного и вторичного статуса, указывающую, что после сброса статуса субканал будет доступен для следующей функции запуска.

[0037] Операция EADM может быть преждевременно прекращена при помощи команды Clear Subchannel. Выполнение команды Clear Subchannel прекращает выполнение AOB в субканале, очищает субканал от указателей выполняемого AOB и асинхронно осуществляет функцию сброса.

[0038] Дополнительные подробности, относящиеся к EADM ORB и связанным с ним управляющим структурам, описаны ниже со ссылкой на ФИГ.2A-2F. В начале со ссылкой на ФИГ.2A описывается один вариант осуществления EADM ORB.

[0039] В одном примере, EADM ORB 200 содержит:

[0040] Параметр 202 прерывания: данное поле сохраняется неизменным в субканале до тех пор, пока оно не будет замещено посредством последующей команды Modify Subchannel или Start Subchannel. Указанные биты помещены в код прерывания ввода-вывода, когда для субканала происходит прерывание ввода вывода, и когда запрос прерывания сбрасывается путем выполнения, например, команды Test Pending Interruption.

[0041] Ключ 204 субканала: данное поле образует ключ субканала для операций EADM, определяемых посредством ARQB, и применяется для извлечения ARQB, извлечения блоков MSB, сохранения ARSB и для получения доступа к основному запоминающему устройству для передачи данных. Значение этого поля является определенным значением; в противном случае, или канальной подсистемой распознается ситуация проверки программы, или распознается исключительная ситуация операнда.

[0042] Управление (X) 205 расширением ORB: данное поле указывает, является ли ORB расширенным. Данное поле представляет собой определенное значение, когда субканал ADM-типа является указанным; в противном случае, распознается или исключительная ситуация операнда, или ситуация проверки программы.

[0043] Адрес 206 блока операций EADM (AOB): данное поле указывает адрес блока операций EADM (AOB). Если некоторые биты данного поля не включают определенное значение, распознается или исключительная ситуация операнда, или ситуация проверки программы.

[0044] Если данное поле указывает местоположение, защищенное от извлечения, или указывает местоположение за пределами конфигурации, функция запуска не инициируется. В этом случае субканал является ожидающим статус с первичным, вторичным и предупреждающим статусом.

[0045] Приоритет 208 канальной подсистемы (CSS): данное поле содержит указатель приоритета канальной подсистемы, который назначен указанному субканалу и используется для упорядочивания выбора субканалов ADM-типа тогда, когда функция запуска подлежит инициированию для одного или нескольких субканалов, которые являются ожидающими запуск.

[0046] Приоритет 210 твердотельного запоминающего устройства (SCM): данное поле содержит указатель приоритета твердотельного запоминающего устройства (SCM), который указывает уровень приоритета, который применяется ко всем операциям EADM, связанным с функцией запуска.

[0047] То, распознается ли поле приоритета SCM средством EADM, зависит от модели. На моделях, которые не распознают это поле, содержимое поля игнорируется, и всем операциям EADM, связанным с функцией запуска, назначается неявный указатель приоритета.

[0048] Формат (FMT) 212: данное поле указывает структуру ORB. Данное поле предназначено для содержания определенного значения тогда, когда указан субканал ADM-типа; в противном случае, распознается исключительная ситуация операнда или устанавливается код особой ситуации.

[0049] Блок операций EADM (AOB), указываемый адресом 206 AOB EADM в EADM ORB, содержит информацию, используемую для вызова операций EADM. AOB выделяется, в одном примере, на границе 4 Кбайт и имеет переменную длину.

[0050] В одном примере, как показано на ФИГ.2B, AOB 220 EADM содержит три секции: блок (ARQB) 222 запроса EADM; блок (ARSB) 224 ответа EADM; и область 226 MSB, содержащую блоки MSB до определенного количества (например, 124). ARQB может указывать использование большего количества блоков MSB, чем определенное, однако только при использовании перехода блоков MSB (то есть путем использования перехода к флагу следующего MSB в MSB).

[0051] Один вариант осуществления блока (ARQB) 222 запроса EADM описан со ссылкой на ФИГ.2C. В одном примере, ARQB 222 содержит:

[0052] Формат 230 (FMT): данное поле указывает структуру ARQB. Значение этого поля представляет собой определенное значение; в противном случае, канальной подсистемой распознается ситуация проверки программы, или в поле кода квалификатора исключительных ситуаций ARSB указывается ошибка кода команды.

[0053] Код 232 команды: это поле предназначено для указания команды перемещения блоков EADM; в противном случае, канальной подсистемой распознается ситуация проверки программы, или в поле кода квалификатора исключительных ситуаций ARSB указывается ошибка кода команды.

[0054] Счетчик 234 блоков MSB: Данное поле указывает счетчик блоков MSB, которые составляют запрос EADM. Максимальное число блоков MSB, которое может быть указано, зависит от модели. Значение этого поля должно быть больше нуля и меньше или равно зависящему от модели максимальному значению счетчика блоков MSB; в противном случае, канальной подсистемой распознается ситуация проверки программы, или в поле кода квалификатора исключительных ситуаций ARSB указывается ошибка в коде команды.

[0055] В дополнение к блоку запроса EADM, EADM ORB также указывает блок ответа EADM (ARSB). В данном варианте осуществления изобретения, блок ответа EADM является значимым только тогда, когда распознается исключительная ситуация. Точнее, ARSB является значимым только тогда, когда в слове статуса субканала EADM (SCSW) присутствует предупреждающий статус, расширенное слово статуса EADM (ESW) является значимым, и блок ответа EADM, хранящий (R) битов, равен единице в расширенном слове отчета EADM (ERW), каждое из них описывается ниже. Когда ARSB не является значимым, содержимое ARSB в AOB является непред сказу емым.

[0056] Если программа сохраняется в ARSB, в то время как связанный субканал является действующим субканалом, могут возникать непредсказуемые результаты.

[0057] Когда ARSB сохраняется, объем данных, которые были переданы, если это имеет место, является непред сказуемым.

[0058] Один вариант осуществления блока ответа EADM описывается со ссылкой на ФИГ. 2D. В одном примере, ARSB 224 содержит:

[0059] формат 240 (FMT): это поле указывает структуру ARSB. Когда ARSB сохраняется, значение этого поля сохраняется как определенное значение.

[0060] Флаги 242 исключительных ситуаций (EF): когда ARSB сохраняется, это поле, если оно установлено, указывает причину исключительной ситуации, по которой сохраняется ARSB. Примеры причин исключительной ситуации включают:

[0061] проверку программы: обнаружена ошибка программирования.

[0062] Проверку защиты: доступу к запоминающему устройству препятствует механизм защиты. Защита распространяется на извлечение ARQB, MSB, AIDAW и данные, подлежащие передаче в твердотельное запоминающее устройство, и на сохранение информации в ARSB и данные, передаваемые из твердотельного запоминающего устройства.

[0063] Проверку канальных данных: неисправленная ошибка запоминающего устройства была обнаружена в отношении данных, которые содержатся в основном запоминающем устройстве и в настоящее время используются для выполнения операции EADM. В случае обнаружения, данная ситуация может указываться, даже если данные не используются при предварительном извлечении. Проверка канальных данных указывается тогда, когда данные, или связанный ключ, имеют недостоверный код проверки блока (СВС) в основном запоминающем устройстве, когда к этим данным обращается канальная подсистема.

[0064] Проверку управления каналом: проверка управления каналом вызывается любым сбоем системы, оказывающим влияние на элементы управления канальной подсистемы. Ситуация включает недостоверный CBC на ARQB, ARSB, MSB, AIDAW или соответствующем связанном ключе. Ситуация может быть указана, когда недостоверный CBC обнаруживается на подвергнутом предварительному извлечению ARQB, MSB, AIDAW или соответствующем связанном ключе, даже если этот ARQB, MSB или AIDAW не используется.

[0065] Проверку средства расширенного асинхронного перемещения данных: неисправленная ошибка была обнаружена в отношении данных, которые содержатся в твердотельном запоминающем устройстве и в настоящее время используются для выполнения операции EADM.

[0066] Идентификаторы 244 блоков управления исключительными ситуациями (ECBI): когда ARSB сохраняется, данное поле представляет собой маску из нескольких битов, биты которой, когда они установлены, указывают какой-либо один из следующих компонентов, которые связаны с распознаванием исключительной ситуации, указываемого полем EF, или их сочетание:

[0067] * блок, или блоки, управления.

[0068] * Область данных основного запоминающего устройства.

[0069] * Твердотельное запоминающее устройство.

[0070] Биты, которые могут быть установлены, отображают, например, блок спецификации перемещения EADM, косвенный адрес данных EADM, данные в основном