Многопортовый контроллер запоминающего устройства с портами, ассоциированными с классами трафика

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в оптимизации пропускной способности запоминающего устройства. Контроллер запоминающего устройства содержит множество портов, в котором каждый порт соединяется для приема операций в запоминающем устройстве из одного или нескольких источников и в котором каждый порт предназначается для трафика операции в запоминающем устройстве конкретного типа, причем контроллер запоминающего устройства содержит блок интерфейса агента, сконфигурированный для переключения трафика операции в запоминающем устройстве с множества портов на множество блоков каналов запоминающего устройства в ответ на относительные параметры качества обслуживания (QoS) для операций в запоминающем устройстве, и причем в ответ на прием первой операции в запоминающем устройстве из первого источника, который передал одну или более предыдущих операций в запоминающем устройстве, и дополнительно в ответ на первый параметр QoS, соответствующий первой операции в запоминающем устройстве, указывающий более высокий уровень обслуживания, чем предыдущие параметры QoS, соответствующие предыдущим операциям в запоминающем устройстве, контроллер запоминающего устройства конфигурируется для повышения предыдущих параметров QoS до уровня обслуживания, указанного первым параметром QoS. 2 н. и 15 з.п. ф-лы, 22 ил.

Реферат

УРОВЕНЬ ТЕХНИКИ

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0001] Это изобретение относится к области контроллеров запоминающего устройства.

ОПИСАНИЕ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

[0002] Цифровые системы обычно включают в себя запоминающую систему, образованную из полупроводниковых запоминающих устройств, например статического оперативного запоминающего устройства (SRAM), динамического оперативного запоминающего устройства (DRAM), синхронного DRAM (SDRAM), SDRAM с удвоенной скоростью передачи данных (DDR, DDR2, DDR3 и т.д.), включая маломощные версии SDRAM (LPDDR, LPDDR2 и т.д.) и т.д. Запоминающая система является энергозависимой, хранящей данные во включенном состоянии, но не в выключенном, однако также обеспечивает доступ с малой задержкой по сравнению с энергонезависимыми запоминающими устройствами, такими как флэш-память, магнитные запоминающие устройства, например накопители на дисках, или оптические запоминающие устройства, например компакт-диск (CD), универсальный цифровой диск (DVD) и накопители BluRay.

[0003] Запоминающие устройства, образующие запоминающую систему, имеют низкоуровневый интерфейс для считывания и записи в запоминающее устройство в соответствии с зависящими от запоминающего устройства протоколами. Источники, которые формируют операции в запоминающем устройстве, обычно взаимодействуют через интерфейс более высокого уровня, например шину, интерфейс двухточечной пакетный передачи и т.п. Источники могут быть процессорами, периферийными устройствами, например устройствами ввода/вывода (I/O), аудио- и видеоустройствами и т.п. Как правило, операции в запоминающем устройстве включают в себя операции считывания запоминающего устройства для передачи данных из запоминающего устройства в устройство и операции записи в запоминающее устройство для передачи данных из источника в запоминающее устройство. Операции считывания запоминающего устройства в этом документе могут короче называться операциями считывания или считываниями, и аналогичным образом операции записи в запоминающее устройство в этом документе могут короче называться операциями записи или записями.

[0004] Соответственно, обычно имеется контроллер запоминающего устройства для приема операций в запоминающем устройстве от интерфейса более высокого уровня и управления запоминающими устройствами для выполнения принятых операций. Контроллер запоминающего устройства обычно также включает в себя очереди для захвата операций в запоминающем устройстве и может включать в себя схемы для повышения быстродействия. Например, некоторые контроллеры запоминающего устройства планируют операции считывания запоминающего устройства перед более ранними операциями записи в запоминающее устройство, которые затрагивают разные адреса.

[0005] Контроллеры запоминающего устройства обладают ограниченной видимостью разных типов трафика, который может выдаваться источниками. Соответственно, контроллеры запоминающего устройства не способы разделять трафик с меньшей крупностью разбиения. Таким образом, повышения быстродействия в контроллерах запоминающего устройства ограничены более грубыми механизмами, например планированием операций считывания до операций записи.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0006] В одном варианте осуществления контроллер запоминающего устройства может включать в себя несколько портов для приема запросов к запоминающему устройству. Каждый порт может ассоциироваться с конкретным типом трафика, например в реальном масштабе времени (RT), графики и не в реальном масштабе времени (NRT). Каждый тип трафика имеет разные требования и характеристику (поведение). В результате предоставления разных портов контроллер запоминающего устройства может параллельно подвергаться воздействию разных типов запросов и соответственно может принимать интеллектуальные решения по планированию на основе смеси трафика.

[0007] В некоторых вариантах осуществления разные порты могут использовать разные протоколы связи. Например, интерфейс центрального процессора (CPU) может использоваться для процессоров, графический интерфейс может использоваться для графических устройств и т.п. В некоторых вариантах осуществления сторонние производители могут разработать один или несколько интерфейсов и могут продавать устройства, которые взаимодействуют с использованием этих интерфейсов. Поскольку в контроллере запоминающего устройства поддерживаются разные порты, системы, которые заключают в себе и контроллер запоминающего устройства и сторонние устройства, могут отказаться от промежуточных схем для преобразования протоколов между сторонними устройствами и контроллером запоминающего устройства. Системы могут стать проще и дешевле, и можно устранить задержку, которая добавлялась бы промежуточными схемами.

[0008] В некоторых вариантах осуществления параметры качества обслуживания (QoS) могут передаваться контроллеру запоминающего устройства вместе с операциями в запоминающем устройстве. Контроллер запоминающего устройства может использовать относительные уровни QoS для планирования запросов к запоминающему устройству из портов в каналы запоминающего устройства. Разные типы трафика могут иметь разные спецификации уровней QoS, и контроллер запоминающего устройства может конфигурироваться для разрешения конфликтов между разными типами параметров QoS для планирования. Более того, средства управления совместным использованием полосы частот могут влиять на планирование.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0009] Нижеследующее подробное описание ссылается на прилагаемые чертежи, которые теперь описываются вкратце.

[0010] Фиг. 1 - блок-схема одного варианта осуществления системы, включающей в себя контроллер запоминающего устройства.

[0011] Фиг. 2 - блок-схема одного варианта осуществления уровней QoS, которые могут задаваться для классов RT и NRT трафика.

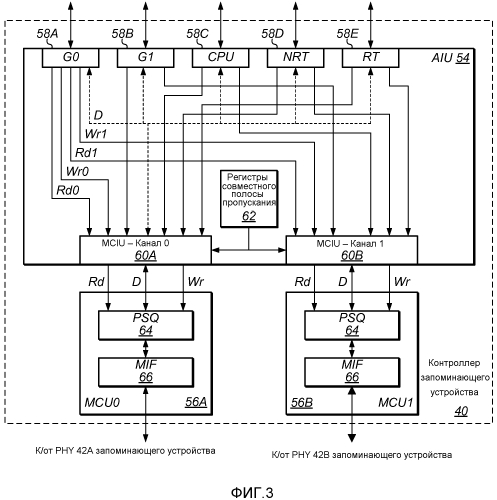

[0012] Фиг. 3 - блок-схема одного варианта осуществления контроллера запоминающего устройства, показанного на фиг. 1.

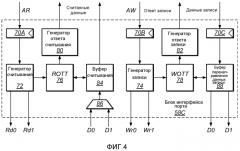

[0013] Фиг. 4 - блок-схема одного варианта осуществления блока интерфейса порта, который может включаться в один вариант осуществления блока интерфейса агента, показанный на фиг. 3.

[0014] Фиг. 5 - блок-схема одного варианта осуществления блока интерфейса канала запоминающего устройства, который может включаться в один вариант осуществления блока интерфейса агента, показанный на фиг. 3.

[0015] Фиг. 6 - блок-схема операций, иллюстрирующая работу одного варианта осуществления арбитра QoS, показанного на фиг. 5.

[0016] Фиг. 7 - блок-схема одного варианта осуществления очереди предварительной сортировки (PSQ), проиллюстрированной в блоке канала запоминающего устройства на фиг. 3.

[0017] Фиг. 8 - блок-схема операций, иллюстрирующая работу одного варианта осуществления блока управления постановкой в очередь, показанного на фиг. 7.

[0018] Фиг. 9 - блок-схема операций, иллюстрирующая работу одного варианта осуществления планировщика, показанного на фиг. 7, для выбора между считываниями и записями, которые нужно планировать.

[0019] Фиг. 10 - блок-схема операций, иллюстрирующая работу одного варианта осуществления планировщика, показанного на фиг. 7, для выбора операции записи, которую нужно планировать.

[0020] Фиг. 11 - таблица, иллюстрирующая работу одного варианта осуществления планировщика, показанного на фиг. 7, для выбора считывания, которое нужно планировать.

[0021] Фиг. 12 - блок-схема одного варианта осуществления блока интерфейса запоминающего устройства (MIF), показанного на фиг. 3.

[0022] Фиг. 13 - блок-схема операций, иллюстрирующая работу одного варианта осуществления блока управления постановкой в очередь MIF, показанного на фиг. 12.

[0023] Фиг. 14 - блок-схема операций, иллюстрирующая работу одного варианта осуществления планировщика активации, показанного на фиг. 12.

[0024] Фиг. 15 - блок-схема операций, иллюстрирующая работу одного варианта осуществления планировщика строба адреса столбца (CAS), показанного на фиг. 12.

[0025] Фиг. 16 - таблица, иллюстрирующая работу одного варианта осуществления конечного планировщика, показанного на фиг. 12.

[0026] Фиг. 17 - блок-схема одного варианта осуществления организации очереди на высоком уровне и относительной важности параметров QoS и оптимизации пропускной способности запоминающего устройства при планировании на различных уровнях.

[0027] Фиг. 18 - блок-схема одного варианта осуществления возможностей контроллера запоминающего устройства для поддержки внутриполосного повышения QoS.

[0028] Фиг. 19 - блок-схема операций, иллюстрирующая работу одного варианта осуществления внутриполосного повышения QoS.

[0029] Фиг. 20 - блок-схема одного варианта осуществления интерфейса повышения QoS боковой полосы.

[0030] Фиг. 21 - блок-схема операций, иллюстрирующая один вариант осуществления повышения QoS вследствие старения операций.

[0031] Фиг. 22 - блок-схема одного варианта осуществления системы, включающей в себя интегральную схему, проиллюстрированную на фиг. 1.

[0032] Хотя изобретение допускает различные модификации и альтернативные виды, его характерные варианты осуществления показаны в качестве примера на чертежах и будут подробно описаны в этом документе. Однако следует понимать, что чертежи и подробное описание к ним не предназначены для ограничения изобретения конкретным раскрытым видом, а наоборот, направлены на охват всех модификаций, эквивалентов и альтернатив, входящих в сущность и объем настоящего изобретения, которые заданы прилагаемой формулой изобретения. Заголовки, используемые в этом документе, служат только для организационных целей и не предназначены для использования в ограничении объема описания. При использовании по всей данной заявке слово "может" используется в разрешающем смысле (то есть в значении "имеющий возможность для..."), а не в обязательном смысле (то есть в значении "должен"). Аналогичным образом слова "включают в себя", "включающий" и "включает в себя" означают "включающий", но не только.

[0033] Различные блоки, схемы или другие компоненты могут описываться как "сконфигурированные для" выполнения задачи или задач. В таком контексте "сконфигурированный для" является свободным изложением структуры, в целом означающей "имеющий схемы, которые" выполняют задачу или задачи во время работы. По существу, блок/схема/компонент может быть сконфигурирован для выполнения задачи, даже когда блок/схема/компонент в настоящее время не включен. Вообще, схемы, которые образуют структуру, соответствующую "сконфигурированный для", могут включать в себя аппаратные схемы. Аналогичным образом для удобства в описании различные блоки/схемы/компоненты могут описываться как выполняющие задачу или задачи. Такие описания следует интерпретировать как включающие в себя фразу "сконфигурированный для". Перечисление блока/схемы/компонента, который конфигурируется для выполнения одной или нескольких задач, в явной форме предназначено не для применения интерпретации шестого пункта 35 U.S.C. § 112 для того блока/схемы/компонента.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0034] Обращаясь теперь к фиг. 1, показана блок-схема одного варианта осуществления системы 5. В варианте осуществления по фиг. 1 система 5 включает в себя интегральную схему 10 (IC), соединенную с внешними запоминающими устройствами 12A-12B. В проиллюстрированном варианте осуществления интегральная схема 10 включает в себя центральный процессор 14 (CPU), который включает в себя один или несколько процессоров 16 и кэш 18 уровня 2 (L2). Другие варианты осуществления могут не включать в себя кэш 18 L2 и/или могут включать в себя дополнительные уровни кэша. Более того, рассматриваются варианты осуществления, которые включают в себя более двух процессоров 16 и которые включают в себя только один процессор 16. Интегральная схема 10 дополнительно включает в себя набор из одного или нескольких периферийных устройств 20, не относящихся к реальному масштабу времени (NRT), и набор из одного или нескольких периферийных устройств 22 реального масштаба времени (RT). В проиллюстрированном варианте осуществления периферийные устройства RT включают в себя процессор 24 изображений, один или несколько каналов 26 отображения и арбитр 28 портов. Другие варианты осуществления по желанию могут включать в себя больше или меньше процессоров 24 изображений, больше или меньше каналов 26 отображения и/или любые дополнительные периферийные устройства реального масштаба времени. Процессор 24 изображений может соединяться для приема данных изображений от одной или нескольких камер в системе 5. Аналогичным образом каналы 26 отображения могут соединяться с одним или несколькими контроллерами дисплея (не показаны), которые управляют одним или несколькими дисплеями в системе. В проиллюстрированном варианте осуществления CPU 14 соединяется с контроллером 30 моста/прямого доступа к памяти (DMA), который может соединяться с одним или несколькими периферийными устройствами 32 и/или одним или несколькими контроллерами 34 интерфейса периферийных устройств. Количество периферийных устройств 32 и контроллеров 34 интерфейса периферийных устройств может меняться от нуля до любого нужного числа в различных вариантах осуществления. Система 5, проиллюстрированная на фиг. 1, дополнительно включает в себя графический блок 36, содержащий один или несколько графических контроллеров, например G0 38A и G1 38B. Количество графических контроллеров в расчете на графический блок и количество графических блоков в других вариантах осуществления может меняться. Как проиллюстрировано на фиг. 1, система 5 включает в себя контроллер 40 запоминающего устройства, соединенный с одной или несколькими схемами 42A-42B физического интерфейса (PHY) запоминающих устройств. PHY 42A-42B запоминающих устройств конфигурируются для взаимодействия по выводам интегральной схемы 10 с запоминающими устройствами 12A-12B. Контроллер 40 запоминающего устройства также включает в себя набор портов 44A-44E. Порты 44A-44B соединяются с графическими контроллерами 38A-38B соответственно с помощью первого типа интерфейса (Интерфейс 1). CPU 14 соединяется с портом 44C с помощью второго типа интерфейса (Интерфейс 2). Периферийные устройства 20 NRT и периферийные устройства 22 RT соединяются с портами 44D-44E соответственно с помощью второго типа интерфейса. Количество портов, включенных в контроллер 40 запоминающего устройства, может меняться в других вариантах осуществления, как и количество контроллеров запоминающего устройства. Количество PHY 42A-42B запоминающих устройств и соответствующих запоминающих устройств 12A-12B в других вариантах осуществления может быть равно одному или более двух.

[0035] В одном варианте осуществления каждый порт 44A-44E может ассоциироваться с конкретным типом трафика. Например, в одном варианте осуществления типы трафика могут включать в себя трафик RT, трафик NRT и графический трафик. Другие варианты осуществления могут включать в себя другие типы трафика в дополнение или вместо подмножества вышеупомянутых типов трафика. Каждый тип трафика может характеризоваться по-разному (например, в показателях требований и характеристики (поведения)), и контроллер запоминающего устройства может по-разному обрабатывать типы трафика, чтобы обеспечить более высокое быстродействие на основе этих характеристик. Например, трафик RT требует обслуживания каждой операции в запоминающем устройстве в рамках конкретного количества времени. Если задержка операции превышает конкретное количество времени, то в периферийном устройстве RT может произойти ошибочная операция. Например, данные изображений могут потеряться в процессоре 24 изображений, или может визуально исказиться отображенное изображение на дисплеях, с которыми соединяются каналы 26 отображения. Трафик RT можно охарактеризовать, например, как изохронный. С другой стороны, графический трафик может иметь относительно большую полосу частот, но не является чувствительным к задержке. Трафик NRT, например от процессоров 16, более чувствителен к задержке по причинам быстродействия, но выдерживает большую задержку. То есть трафик NRT обычно может обслуживаться с любой задержкой, не вызывая ошибочную работу в устройствах, формирующих трафик NRT. Аналогичным образом, менее чувствительный к задержке графический трафик, но с большей полосой частот обычно может обслуживаться с любой задержкой. Другой трафик NRT может включать в себя трафик аудио, который имеет относительно малую полосу частот и обычно может обслуживаться с разумной задержкой. Большая часть трафика периферийных устройств также может быть NRT (например, трафик к запоминающим устройствам, например магнитному, оптическому или твердотельному запоминающему устройству).

[0036] В результате предоставления портов 44A-44E, ассоциированных с разными типами трафика, контроллер 40 запоминающего устройства может подвергаться воздействию разных типов трафика параллельно, и соответственно может допускать принятие лучших решений о том, какие операции в запоминающем устройстве обслуживать перед другими, на основе типа трафика. В некоторых вариантах осуществления каждый порт может предназначаться исключительно для трафика RT либо трафика NRT. В других вариантах осуществления порты могут ассоциироваться с конкретным типом трафика, но в порту могут поддерживаться другие типы трафика. В варианте осуществления графический трафик может считаться трафиком NRT, но наличие видимости для графического трафика отдельно от другого трафика NRT может быть полезным для балансирования полосы частот между другими источниками NRT и источником RT. Аналогичным образом, наличие процессорного трафика отдельно от других источников NRT может быть полезным при балансировании полосы частот. В проиллюстрированном варианте осуществления порт 44E RT может ассоциироваться с трафиком RT, а оставшиеся порты 44A-44D могут ассоциироваться с трафиком NRT.

[0037] Как правило, порт может быть точкой связи в контроллере 40 запоминающего устройства для взаимодействия с одним или несколькими источниками. В некоторых случаях порт может предназначаться для источника (например, порты 44A-44B могут предназначаться графическим контроллерам 38A-38B соответственно). В других случаях порт может совместно использоваться несколькими источниками (например, процессоры 16 могут совместно использовать порт 44C CPU, периферийные устройства 20 NRT могут совместно использовать порт 44D NRT, и периферийные устройства RT, например каналы 26 отображения и процессор 24 изображений, могут совместно использовать порт 44E RT). Порт может соединяться с одним интерфейсом для взаимодействия с одним или несколькими источниками. Таким образом, когда источники совместно используют некий интерфейс, может присутствовать арбитр на стороне источников интерфейса для выбора между источниками. Например, кэш 18 L2 может служить для контроллера 40 запоминающего устройства в качестве арбитра для порта 44C CPU. Арбитр 28 портов может служить в качестве арбитра для порта 44E RT, и аналогичный арбитр портов (не показан) может быть арбитром для порта 44D NRT. Одиночный источник в порту или сочетание источников в порту может называться агентом.

[0038] Каждый порт 44A-44E соединяется с интерфейсом для взаимодействия с соответствующим агентом. Интерфейс может быть любым типом средств связи (например, шиной, двухточечным межсоединением и т.п.) и может реализовывать любой протокол. В некоторых вариантах осуществления все порты 44A-44E могут реализовать один и тот же интерфейс и протокол. В других вариантах осуществления разные порты могут реализовывать разные интерфейсы и/или протоколы. Например, проиллюстрированный на фиг. 1 вариант осуществления включает в себя графические контроллеры 38A-38B, использующие один тип интерфейса/протокола, и CPU 14, периферийные устройства 20 NRT и периферийные устройства 22 RT, использующие другой тип интерфейса/протокола. Интерфейс может обращаться к определениям сигналов и электрическим свойствам интерфейса, а протокол может быть логическим определением связи по интерфейсу (например, включающим в себя команды, правила упорядочения, поддержку когерентности, при их наличии и т.п.). Поддержка более одного интерфейса в различных портах 44A-44E может устранить потребность в преобразовании из одного интерфейса, поддерживаемого источником/агентом, в интерфейс, поддерживаемый контроллером 40 запоминающего устройства, что может повысить быстродействие в некоторых вариантах осуществления. Дополнительно некоторые варианты осуществления интегральной схемы 10 могут включать в себя схемы, приобретенные у стороннего производителя в виде предварительно размещенного в корпусе блока, обычно называемого в промышленности интеллектуальной собственностью (IP). IP может быть "жесткой" (в этом случае она задается в виде таблицы соединений схем, которые разводятся и размещаются на IC в виде блока) или "мягкой" (в этом случае она задается в виде синтезируемого блока, который можно синтезировать вместе с другими блоками, которые нужно включить в интегральную схему 10). И жесткая и мягкая IP включает в себя заданный интерфейс и протокол, которые проектировщику интегральной схемы 10 обычно нельзя изменять (по меньшей мере без уплаты пошлины стороннему производителю, который владеет этой IP). Соответственно, поддержка нескольких интерфейсов/протоколов может дать возможность упрощенного включения IP стороннего производителя.

[0039] В варианте осуществления каждый источник может назначать параметр качества обслуживания (QoS) каждой операции в запоминающем устройстве, переданной этим источником. Параметр QoS может идентифицировать запрошенный уровень обслуживания для операции в запоминающем устройстве. Операциям в запоминающем устройстве со значениями параметров QoS, запрашивающими более высокие уровни обслуживания, может отдаваться предпочтение перед операциями в запоминающем устройстве, запрашивающими более низкие уровни обслуживания. Например, каждый из интерфейсов к портам 44A-44E на фиг. 1 показан включающим в себя команду (Cmd), идентификатор потока (FID) и параметр QoS (QoS). Команда может идентифицировать операцию в запоминающем устройстве (например, считывание или запись). Команда/операция считывания запоминающего устройства вызывает передачу данных из запоминающего устройства 12A-12B в источник, тогда как команда/операция записи в запоминающее устройство вызывает передачу данных из источника в запоминающее устройство 12A-12B. Команды также могут включать в себя команды для программирования контроллера 40 запоминающего устройства. Например, то, какие диапазоны адресов отображаются в какие каналы запоминающего устройства, параметры совместного использования полосы пропускания и т.п. могут быть программируемыми в контроллере 40 запоминающего устройства. FID может идентифицировать операцию в запоминающем устройстве как часть потока операций в запоминающем устройстве. Поток операций в запоминающем устройстве обычно может быть связанным, тогда как операции в запоминающем устройстве из разных потоков, даже от одного и того же источника, могут быть не связаны. Часть FID (например, поле источника) может идентифицировать источник, а оставшаяся часть FID может идентифицировать поток (например, поле потока). Таким образом, FID может быть аналогичен ID транзакции, и некоторые источники могут просто передавать ID транзакции в качестве FID. В таком случае поле источника в ID транзакции может быть полем источника в FID, и порядковый номер (который идентифицирует транзакцию среди транзакций от одного и того же источника) в ID транзакции может быть полем потока в FID. Однако источники, которые группируют транзакции в виде потока, могут по-разному использовать FID. В качестве альтернативы потоки могут соотноситься с полем источника (например, операции от одного и того же источника могут быть частью одного и того же потока, а операции от другого источника являются частью другого потока). Возможность идентифицировать транзакции потока может использоваться различными способами, описанными ниже (например, повышение QoS, переупорядочение и т.п.).

[0040] Таким образом, заданный источник может конфигурироваться для использования параметров QoS, чтобы идентифицировать, какие операции в запоминающем устройстве важнее для источника (и соответственно должны обслуживаться до других операций в запоминающем устройстве от того же источника), особенно для источников, которые поддерживают неупорядоченные передачи данных относительно адресных передач от источника. Кроме того, параметры QoS могут позволить источникам запрашивать более высокие уровни обслуживания, нежели другие источники в том же порту и/или источники в других портах.

[0041] В некоторых вариантах осуществления разные типы трафика могут иметь разные определения параметров QoS. То есть разные типы трафика могут иметь разные наборы параметров QoS. Значимость данного значения параметра QoS зависит от набора параметров QoS, из которого он извлекается. Например, может быть задан набор параметров QoS RT, и может быть задан набор параметров QoS NRT. Таким образом, значению параметра QoS RT придается значимость в рамках набора параметров QoS RT, а значению параметра QoS NRT придается значимость в рамках набора параметров QoS NRT. Другие варианты осуществления могут реализовать одинаковый набор параметров QoS во всех портах или среди всех типов трафика.

[0042] Контроллер 40 запоминающего устройства может конфигурироваться для обработки параметров QoS, принятых в каждом порту 44A-44E, и может использовать относительные значения параметров QoS для планирования операций в запоминающем устройстве, принятых в портах, относительно других операций в запоминающем устройстве из этого порта и относительно других операций в запоминающем устройстве, принятых в других портах. Точнее говоря, контроллер 40 запоминающего устройства может конфигурироваться для сравнения параметров QoS, которые извлекаются из разных наборов параметров QoS (например, параметры QoS RT и параметры QoS NRT), и может конфигурироваться для принятия решений по планированию на основе этих параметров QoS.

[0043] Параметры QoS соответственно могут быть значениями, которые передаются вместе с операциями в запоминающем устройстве и которые могут использоваться в контроллере запоминающего устройства для идентификации запрошенных уровней QoS. Уровни QoS могут находиться относительно других уровней и могут задавать, какие операции в запоминающем устройстве предпочтительно выбирать перед другими, имеющими более низкие уровни QoS. Таким образом, уровни QoS могут функционировать как своего рода приоритет после интерпретации контроллером 40 запоминающего устройства для рассмотрения уровней QoS, заданных в разных наборах, хотя приоритет может быть сбалансирован другими факторами.

[0044] В некоторых вариантах осуществления контроллер 40 запоминающего устройства может конфигурироваться для повышения уровней QoS для ожидающих операций в запоминающем устройстве. Могут поддерживаться различные механизмы повышения. Например, контроллер 40 запоминающего устройства может конфигурироваться для повышения уровня QoS для ожидающих операций в запоминающем устройстве из потока в ответ на прием другой операции в запоминающем устройстве из того же потока, которая имеет параметр QoS, задающий более высокий уровень QoS. Этот вид повышения QoS может называться внутриполосным повышением, поскольку параметры QoS, переданные с использованием обычного способа передачи операции в запоминающем устройстве, также служат в качестве неявного запроса повышения для операций в запоминающем устройстве в том же потоке. Контроллер 40 запоминающего устройства может конфигурироваться для принудительной отправки ожидающих операций в запоминающем устройстве из одинакового порта или источника, но не одинакового потока, в качестве вновь принятой операции в запоминающем устройстве, задающей более высокий уровень QoS. В качестве другого примера контроллер 40 запоминающего устройства может конфигурироваться для соединения с интерфейсом боковой полосы от одного или нескольких агентов, и может повышать уровни QoS в ответ на прием запроса повышения по интерфейсу боковой полосы. В другом примере контроллер 40 запоминающего устройства может конфигурироваться для отслеживания относительного срока ожидающих операций в запоминающем устройстве. Контроллер 40 запоминающего устройства может конфигурироваться для повышения уровня QoS старых операций в запоминающем устройстве с определенными сроками. Сроки, при которых происходит повышение, могут зависеть от текущего параметра QoS старой операции в запоминающем устройстве.

[0045] Контроллер 40 запоминающего устройства может конфигурироваться для определения канала запоминающего устройства, адресуемого каждой операцией в запоминающем устройстве, принятой в портах, и может конфигурироваться для передачи операций в запоминающем устройстве запоминающему устройству 12A-12B по соответствующему каналу. Количество каналов и отображение адресов в каналы может меняться в различных вариантах осуществления и может быть программируемым в контроллере запоминающего устройства. Контроллер запоминающего устройства может использовать параметры QoS у операций в запоминающем устройстве, отображенных в один и тот же канал, для определения порядка операций в запоминающем устройстве, переданных в тот канал. То есть контроллер запоминающего устройства может переупорядочить операции в запоминающем устройстве от их исходного порядка приема в портах. Более того, во время обработки в канале операции в запоминающем устройстве могут быть снова переупорядочены в одной или нескольких точках. На каждом уровне переупорядочения можно уменьшить внимание, уделенное параметрам QoS, и можно увеличить факторы, которые влияют на эффективность пропускной способности запоминающего устройства. Как только операции в запоминающем устройстве достигают конца конвейера канала запоминающего устройства, операции можно упорядочить по сочетанию уровней QoS и эффективности пропускной способности запоминающего устройства. В некоторых вариантах осуществления можно реализовать высокое быстродействие.

[0046] Процессоры 16 могут реализовывать любую архитектуру системы команд и могут конфигурироваться для выполнения команд, заданных в этой архитектуре системы команд. Процессоры 16 могут применять любую микроархитектуру, включающую в себя скалярную, суперскалярную, конвейерную, суперконвейерную, неупорядоченную, упорядоченную, спекулятивную, неспекулятивную и т.п., или их сочетания. Процессоры 16 могут включать в себя схемы и опционально могут реализовывать методики микропрограммирования. Процессоры 16 могут включать в себя один или несколько кэшей уровня 1, и соответственно кэш 18 является кэшем L2. Другие варианты осуществления могут включать в себя несколько уровней кэшей в процессорах 16, и кэш 18 может быть следующим уровнем ниже по иерархии. Кэш 18 может применять любой размер и любую конфигурацию (наборно-ассоциативный кэш, кэш прямого отображения и т.п.).

[0047] Графические контроллеры 38A-38B могут быть любыми схемами графической обработки. В целом, графические контроллеры 38A-38B могут конфигурироваться для представления объектов, которые нужно отобразить, в буфере кадра. Графические контроллеры 38A-38B могут включать в себя графические процессоры, которые могут выполнять программное обеспечение графики для выполнения части или всей графической операции и/или аппаратное ускорение некоторых графических операций. Величина аппаратного ускорения и программной реализации может меняться от одного варианта осуществления к другому.

[0048] Периферийные устройства 20 NRT могут включать в себя любые периферийные устройства, не относящиеся к реальному масштабу времени, которым по причинам быстродействия и/или полосы пропускания предоставляется независимый доступ к запоминающему устройству 12A-12B. То есть доступ периферийных устройств 20 NRT не зависит от CPU 14 и может проходить параллельно операциям CPU в запоминающем устройстве. Другие периферийные устройства, например периферийное устройство 32 и/или периферийные устройства, соединенные с интерфейсом периферийных устройств, управляемым контроллером 34 интерфейса периферийных устройств, также могут быть периферийными устройствами, не относящимися к реальному масштабу времени, но могут не требовать независимого доступа к запоминающему устройству. Различные варианты осуществления периферийных устройств 20 NRT могут включать в себя видеокодеры и декодеры, схемы преобразователя масштаба/вращателя, схемы сжатия/восстановления изображений и т.п.

[0049] Как упоминалось выше, периферийные устройства 22 RT могут включать в себя процессор 24 изображений и каналы 26 отображения. Каналы 26 отображения могут включать в себя схемы для выборки одного или нескольких кадров и для смешивания кадров, чтобы создать изображение на дисплее. Каналы 26 отображения могут дополнительно включать в себя один или несколько видеоконвейеров. Результатом каналов 26 отображения может быть поток пикселей, которые нужно отобразить на экране дисплея. Значения пикселей могут передаваться контроллеру дисплея для отображения на экране дисплея. Процессор 26 изображений может принимать данные с камеры и перерабатывать эти данные в изображение для сохранения в запоминающем устройстве.

[0050] Контроллер 30 моста/DMA может содержать схемы для сопряжения периферийного устройства (устройств) 32 и контроллера (контроллеров) 34 интерфейса периферийных устройств с областью памяти. В проиллюстрированном варианте осуществления контроллер 30 моста/DMA может переносить операции в запоминающем устройстве от периферийных устройств/контроллеров интерфейса периферийных устройств через CPU 14 в контроллер 40 запоминающего устройства. CPU 14 также может поддерживать когерентность между перенесенными операциями в запоминающем устройстве и операциями в запоминающем устройстве от процессоров 16/кэша 18 L2. Кэш 18 L2 также может разрешать конфликты перенесенных операций в запоминающем устройстве с операциями в запоминающем устройстве от процессоров 16, которые нужно передать по интерфейсу CPU в порт 44C CPU. Контроллер 30 моста/DMA также может предоставлять операцию DMA от лица периферийных устройств 32 и контроллеров 34 интерфейса периферийных устройств для передачи блоков данных в запоминающее устройство и из него. Конкретнее, контроллер DMA может конфигурироваться для выполнения передач в запоминающее устройство 12A-12B и из него посредством контроллера 40 запоминающего устройства от лица периферийных устройств 32 и контроллеров 34 интерфейса периферийных устройств. Контроллер DMA может быть программируемым с помощью процессоров 16 для выполнения операций DMA. Например, контроллер DMA может быть программируемым посредством дескрипторов. Дескрипторы могут быть структурами данных, сохраненными в запоминающем устройстве 12A-12B, которые описывают передачи DMA (например, адреса источника и назначения, размер и т.п.). В качестве альтернативы контроллер DMA может быть программируемым посредством регистров в контроллере DMA (не показаны).

[0051] Периферийные устройства 32 могут включать в себя любые требуемые устройства ввода/вывода или другие аппаратные средства, которые включаются в интегральную схему 10. Например, периферийные устройства 32 могут включать в себя сетевые периферийные устройства, например один или несколько контроллеров управления доступом к среде передачи (MAC), таких как MAC Ethernet или контроллер Wireless Fidelity (WiFi). В периферийные устройства 32 может включаться звуковой блок, включающий в себя различные устройства обработки звуковых сигналов. В периферийные устройства 32 может включаться один или несколько цифровых процессоров сигналов. Периферийные устройства 32 могут включать в себя любой другой требуемый функционал, например таймеры, встроенное в кристалл запоминающее устройство секретных значений, механизм шифрования и т.п., или любое их сочетание.

[0052] Контроллеры 34 интерфейса периферийных устройств могут включать в себя любые контроллеры для любого типа интерфейса периферийных устройств. Например, контроллеры интерфейса периферийных устройств могут включать в себя различные контроллеры интерфейса, например контроллер универсальной последовательной шины (USB), контроллер межсоединения периферийных компонентов (PCIe)