Устройство для контроля операции суммирования

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

255649

1 Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства Х

Заявлено 09.1.1968 (№ 1208870/18-24) с присоединением заявки т№

Приоритет

Опубликовано 28.Х.1969. Бюллетень ¹ 33

Дата опубликования описания 16.111.1970

Кл. 42птз 11,2 00

МПК С 061

УДК 681.326.77 (088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Автор изобретения

В. П. Гондарев

Таганрогский радиотехнический институт

Заявитель

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОПЕРАЦИИ СУММИРОВАНИЯ

ОДНОРАЗРЯДНЬ|Х ПРИРАЩЕНИЙ С и-РАЗРЯДНЫМИ

ДВОИЧНЫМИ ЧИСЛАМИ

01

15

Настоящее изобретение предназначено для контроля операции суммирования одноразрядных приращений применительно к последовательно-последовательным и параллельно-последовательным цифровым интегрирующим машинам.

Известны устройства контроля операции суммирования, осуществляющие контроль на чети ость.

С целью упрощения и повышения эффективности контроля предлагается устройство для случая, когда суммируются одноразрядные приращения с п-разрядными двоичными числамии.

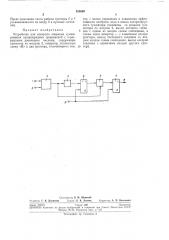

Оно содержит сумматор по модулю 2, инвертор, логическую схему «И» и два триггера. В отличие от известных вход и выход контролируемого сумматора соединены со входами сумматора по модулю 2, выход которого соединен с одним из входов схемы совпадения, а также через инвертор — с единичным входом триггера, выход последнего соединен со вторым входом схемы совпадения, выход которой соединен с единичным входом другого триггера.

На чертеже приведена функциональная схема устройства.

Она содержит вход 1 устройства контроля, подключающийся ко входу контролируемого сумматора; вход 2 устройства контроля, подключа2ощийся к выходу контролируемого сумматора; сумматор 8 по модулю 2; инвертор 4; логическую схему «И» 5; триггеры б, 7; выход

8; вход 9 импульса начальной установки.

Как известно, при сложении по модулю 2 двух и-разрядных двоичных кодов, отличающихся друг от друга на + 1,0 или — 1, получается одно из следующих п-разрядных чисел:

00 ... 0000

00 ... 0001

00 ... 0011

Устройство выдает сигнал «сбой» при фиксации первой единицы после нуля в сумме по модулю 2.

Кодовые п-разрядные двоичные числа с входа и выхода контролируемого сумматора подаются на входы 1 и 2 сумматора 3 по модулю 2. Первый нуль суммы по модулю 2 инвертируется инвертором 4 и перебрасывает триггер б в единичное состояние. При этом на схему 5 совпадения поступает единичный потенциал. Если после первого нуля в кодовом слоье, выходящем из сумматора по модулю 2, появится единица, она проходит через схему 5 и перебрасывает триггер 7 в единичное сос30 тояние. С выхода 8 снимается сигнал «сбой».

255649

Составитель В. М. Шумский

Редактор Т. В. Данилова Техред Л. Я. Левина

Корректор А. П. Васильева

Заказ 512/15 Тира>к 480 Подписное

ЦНИИПИ Комитета по делам изобретепйй и открытий при Совете Министров СССР

Москва Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

После окончания такта работы триггеры б и 7 устанавливаются по входу 9 в нулевые состояния.

Предмет изобретения

Устройство для контроля операции суммирования одноразрядных приращений с и-разрядными двоичными числами, содержащее сумматор по модулю 2, инвертор, логическую схему «И» и два триггера, отличающееся тем, что, с целью упрощения и повышения эффективности контроля, вход и выход контролируемого сумматора соединены со входами сумматора по модулю 2, выход которого соединен с одним из входов схемы совпадения, а также через инвертор — с единичным входом триггера, выход последнего соединен со вторым входом схемы совпадения, выход которой соединен с единичным входом другого триг10 гера.