Цифровой фазовый детектор (варианты)

Иллюстрации

Показать всеИзобретение относится к области радиоизмерений и предназначено для определения фазового сдвига импульсных последовательностей с произвольными длительностями импульсов и скважностями. Цифровой фазовый детектор может найти применение при построении как фазометров широкого назначения, универсальных средств фазовой автоподстройки частоты, так и специализированных средств контроля временных параметров. Техническим результатом является повышение эффективности функционирования цифрового фазового детектора за счет исключения ошибки, связанной с нарушением порядка поступления информационных импульсов. Цифровой фазовый детектор содержит четыре D-триггера, а также логические элементы ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ. 3 н. и 1 з.п. ф-лы, 4 ил.

Реферат

Изобретение относится к области радиоизмерений и предназначено для определения фазового сдвига импульсных последовательностей с произвольными длительностями импульсов и скважностями. Фазовый детектор может найти применение при построении как фазометров широкого назначения, универсальных средств фазовой автоподстройки частоты, так и специализированных средств контроля временных параметров.

Достаточно распространенной является схема фазового детектора, в основе которой находится RS-триггер с формирователями коротких импульсов на установочных входах, входы формирователей импульсов являются информационными входами фазового детектора, выходом которого служит выход RS-триггера [Партала О.Н. Цифровая электроника. - СПб: Наука и техника, 2001, стр.109, рис.19.5; Метрология и радиоизмерения / Под ред. В.И. Нефедова. - М: Высшая школа, 2003, стр.301, рис.9.8.]. Недостатком указанной схемы является то, что для корректного определения фазовых сдвигов требуется подавать на S-вход RS-триггера опережающую последовательность импульсов, а на R-вход запаздывающую, т.е. требуется априорная информация о знаке временного рассогласования процессов. Указанное ограничивает области применений детектора и снижает его эффективность, так как при неизвестном знаке фазового сдвига возможно неправильное определение его значения.

Более эффективным является фазовый детектор, выбранный в качестве прототипа и описанный в [Patent US 8026742 B1. Phase detector. Marvell International Ltd. Sep.27, 2011.]. Детектор содержит два D-триггера, четыре логических элемента И и два логических элемента ИЛИ, тактовые входы D-триггеров являются информационными входами детектора, выходы D-триггеров соединены со входами первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с объединенными обнуляющими входами D-триггеров, второй вход первого элемента ИЛИ соединен с выходом второго элемента И, входы которого объединены с информационными входами детектора, первые входы второго и третьего элементов И соединены с выходами D-триггеров, а вторые входы объединены и подключены к выходу второго элемента ИЛИ, входы которого объединены с информационными входами детектора, выходами которого являются выходы второго и третьего элементов И.

Описанный фазовый детектор не требует априорного знания знака фазового сдвига исследуемых сигналов, его входы являются равнозначными. На выходах устройства формируются импульсы, длительности которых определяют искомый фазовый сдвиг. Однако, если в процессе работы детектора по какой-либо причине на один из его входов первым поступил не опережающий сигнал, а запаздывающий, то фазовый сдвиг будет определен с ошибкой, которая может быть весьма существенной. В этом случае вместо формирования импульса длительностью, равной относительному временному сдвигу положительных фронтов импульсов, поступающих на информационные входы, будет сформирован выходной импульс длительностью, равной разности периода следования информационных импульсов и искомого временного сдвига. Это является существенным недостатком устройства. Другим его недостатком является то, что формирование отрицательного фронта выходного импульса происходит только после поступления по цепи обратной связи на входы сброса D-триггеров обнуляющего импульса, а этому в свою очередь предшествует срабатывание (перевод в состояние высокого логического уровня на выходе) триггера, на вход которого поступил импульс запаздывающей последовательности. Таким образом происходит задержка формирования отрицательного фронта выходного импульса, приводящая к его растягиванию и, следовательно, к ошибке определения фазового сдвига, что может быть весьма существенно при прецизионных измерениях с высоким разрешением.

Технический результат, достигаемый при использовании изобретения, заключается в повышении эффективности функционирования цифровых фазовых детекторов за счет исключения ошибки, связанной с нарушением порядка поступления информационных импульсов и повышения точности формирования временных интервалов, определяющих искомый фазовый сдвиг.

Технический результат достигается тем, что в цифровой фазовый детектор (вариант 1), содержащий первый и второй D-триггеры, тактовые входы которых являются соответственно первым и вторым информационными входами детектора и логический элемент ИЛИ, выход которого соединен с объединенными входами обнуления первого и второго D-триггеров, согласно изобретению, введены дополнительно третий и четвертый D-триггеры и логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом детектора, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с прямыми выходами первого и второго D-триггеров соответственно, D-входы первого и второго D-триггеров соединены с их инверсными выходами, первый вход элемента ИЛИ соединен с выходом третьего D-триггера, а второй вход соединен с выходом четвертого D-триггера, установочные входы третьего и четвертого D-триггеров объединены и составляют вход обнуления детектора, инверсные тактовые входы третьего и четвертого D-триггеров объединены с тактовыми входами соответственно первого и второго D-триггеров, D-входы третьего и четвертого D-триггеров являются входами фиксированного уровня логического нуля.

Технический результат достигается тем, что в цифровой фазовый детектор (вариант 2), содержащий первый и второй D-триггеры, тактовые входы которых являются соответственно первым и вторым информационными входами детектора и логический элемент ИЛИ, выход которого соединен с объединенными входами обнуления первого и второго D-триггеров, согласно изобретению, введены дополнительно третий, четвертый, пятый D-триггеры и логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом детектора, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с прямыми выходами первого и второго D-триггеров соответственно, D-входы первого и второго D-триггеров соединены с их инверсными выходами, первый вход элемента ИЛИ соединен с выходом третьего D-триггера, а второй вход соединен с выходом четвертого D-триггера, установочные входы третьего и четвертого D-триггеров объединены и составляют вход обнуления детектора, инверсные тактовые входы третьего и четвертого D-триггеров объединены с тактовыми входами соответственно первого и второго D-триггеров, D-входы третьего и четвертого D-триггеров являются входами фиксированного уровня логического нуля, D-вход пятого D-триггера соединен с прямым выходом первого D-триггера, а тактовый вход пятого D-триггера соединен с прямым выходом второго D-триггера, выход пятого D-триггера является знаковым выходом детектора.

Технический результат достигается тем, что в цифровой фазовый детектор (вариант 3), содержащий первый и второй D-триггеры, тактовые входы которых являются соответственно первым и вторым информационными входами детектора и логический элемент ИЛИ, выход которого соединен с объединенными входами обнуления первого и второго D-триггеров, согласно изобретению, введены дополнительно третий, четвертый, пятый D-триггеры, логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и демультиплексор, выходы которого являются первым и вторым выходами детектора, информационный вход демультиплексора соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены с прямыми выходами первого и второго D-триггеров соответственно, D-входы первого и второго D-триггеров соединены с их инверсными выходами, первый вход элемента ИЛИ соединен с выходом третьего D-триггера, а второй вход соединен с выходом четвертого D-триггера, установочные входы третьего и четвертого D-триггеров объединены и составляют вход обнуления детектора, инверсные тактовые входы третьего и четвертого D-триггеров объединены с тактовыми входами соответственно первого и второго D-триггеров, D-входы третьего и четвертого D-триггеров являются входами фиксированного уровня логического нуля, D-вход пятого D-триггера соединен с прямым выходом первого D-триггера, а тактовый вход пятого D-триггера соединен с прямым выходом второго D-триггера, выход пятого D-триггера соединен с адресным входом демультиплексора.

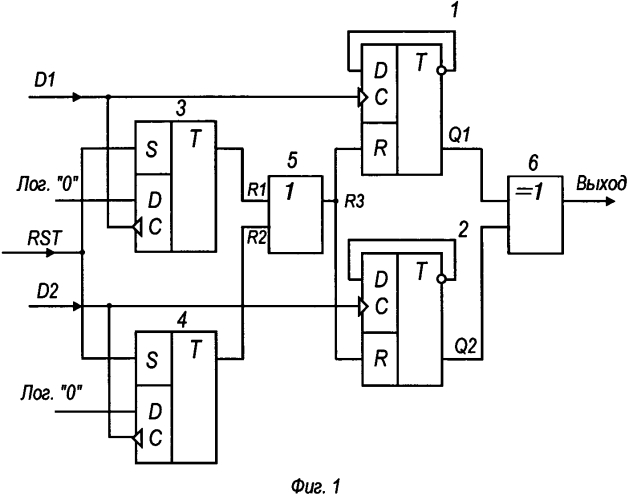

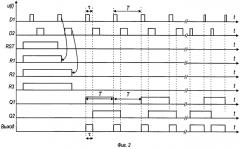

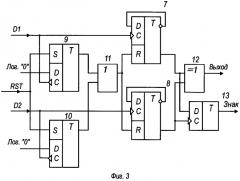

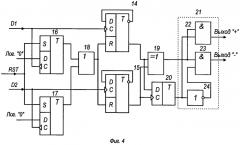

Сущность изобретения поясняется графическим материалом. На фиг.1 показана функциональная схема фазового детектора по первому варианту, на фиг.2 - временные диаграммы, иллюстрирующие работу детектора, показанного на фиг.1. На фиг.3 и фиг.4 показаны функциональные схемы фазовых детекторов по второму и третьему вариантам соответственно.

Схема по фиг.1 содержит D-триггеры 1, 2, 3, 4, логический элемент ИЛИ 5 и логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, тактовые входы D-триггеров 1, 2 являются соответственно первым D1 и вторым D2 информационными входами детектора, выходом которого является выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6, первый и второй входы которого соединены с прямыми выходами D-триггеров 1, 2 соответственно, D-входы которых соединены с их инверсными выходами, входы обнуления D-триггеров 1, 2 соединены с выходом элемента ИЛИ 5, первый и второй входы которого соединены с выходами D-триггеров 3 и 4 соответственно, установочные входы D-триггеров 3, 4 объединены и составляют вход обнуления RST детектора, инверсные тактовые входы D-триггеров 3, 4 объединены с тактовыми входами D-триггеров 1, 2 соответственно, D-входы D-триггеров 3, 4 являются входами фиксированного уровня логического нуля.

Временные диаграммы (см. фиг.2) содержат импульсы на входах D1 и D2 следующие с периодом Т, фазовый сдвиг между которыми следует определить, показанный в виде временного интервала τ, импульс обнуления на входе RST, логические уровни R1 и R2 на выходах D-триггеров 3 и 4 соответственно, логический уровень R3 на выходе элемента ИЛИ 5, импульсы на прямых выходах Q1 и Q2 D-триггеров 1 и 2 соответственно, импульсы (Выход) длительностью τ на выходе фазового детектора.

Схема по фиг.3 содержит D-триггеры 7, 8, 9,10, 13 логический элемент ИЛИ 11 и логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12, тактовые входы D-триггеров 7, 8 являются соответственно первым D1 и вторым D2 информационными входами детектора, выходом которого является выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12, первый и второй входы которого соединены с прямыми выходами D-триггеров 7, 8 соответственно, D-входы которых соединены с их инверсными выходами, входы обнуления D-триггеров 7, 8 соединены с выходом элемента ИЛИ 11, первый и второй входы которого соединены с выходами D-триггеров 9 и 10 соответственно, установочные входы D-триггеров 9, 10 объединены и составляют вход обнуления RST детектора, инверсные тактовые входы D-триггеров 9, 10 объединены с тактовыми входами D-триггеров 7, 8 соответственно, D-входы D-триггеров 9, 10 являются входами фиксированного уровня логического нуля, D-вход D-триггера 13 соединен с прямым выходом D-триггера 7, а тактовый вход D-триггера 13 соединен с прямым выходом D-триггера 8, выход D-триггера 13 является знаковым выходом детектора.

Схема по фиг.4 содержит D-триггеры 14, 15, 16, 17, 20 логический элемент ИЛИ 18, логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19 и демультиплексор 21, состоящий из логических элементов И 22, 23 и инвертора 24, тактовые входы D-триггеров 14, 15 являются соответственно первым D1 и вторым D2 информационными входами детектора, выходами которого является выходы демультиплексора 21, информационный вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19, первый и второй входы которого соединены с прямыми выходами D-триггеров 14, 15 соответственно, D-входы которых соединены с их инверсными выходами, входы обнуления D-триггеров 14, 15 соединены с выходом элемента ИЛИ 18, первый и второй входы которого соединены с выходами D-триггеров 16 и 17 соответственно, установочные входы D-триггеров 16, 17 объединены и составляют вход обнуления RST детектора, инверсные тактовые входы D-триггеров 16, 17 объединены с тактовыми входами D-триггеров 14, 15 соответственно, D-входы D-триггеров 16, 17 являются входами фиксированного уровня логического нуля, D-вход D-триггера 20 соединен с прямым выходом D-триггера 14, а тактовый вход D-триггера 20 соединен с прямым выходом D-триггера 15, выход D-триггера 20 является знаковым выходом детектора. Демультиплексор 21 содержит логические элементы И 22, 23 и инвертор 24, вход которого объединен с первым входом элемента И 22 и является адресным входом демультиплексора, информационным входом которого являются объединенные вторые входы элементов И 22, 23, первый вход элемента И 23 соединен с выходом инвертора 24, выходами демультиплексора являются выходы элементов И 22, 23.

Работа фазового детектора (см. фиг.1) сводится к следующему.

Информационные сигналы, представляющие собой последовательности импульсов, следующие с периодом Т, фазовый сдвиг между которыми, выраженный в виде интервала времени τ, следует определить, поступают на входы D1 и D2 устройства (см. фиг.2), откуда направляются непосредственно на тактовые входы D-триггеров 1 и 2, работающих в счетном режиме (в режиме деления на два). Началу детектирования предшествует подача на вход обнуления RST детектора импульса обнуления. Это необходимо для перевода D-триггеров 1, 2 из произвольного состояния в состояние низкого логического уровня на выходе и удержания их в этом состоянии до наступления пауз между информационными импульсами. Для этой цели служат D-триггеры 3, 4, каждый из которых по импульсу RST переводится в состояние высокого логического уровня на выходе (точки R1 и R2) и устанавливает такой же уровень на выходе элемента ИЛИ 5 (точка R3), а следовательно и на входах обнуления D-триггеров 1, 2. Однако сбрасывание D-триггеров 3, 4 в исходное состояние происходит не сразу по окончании действия импульса RST, а только после того как сформируются отрицательные фронты импульсов на входах D1, D2 (см. временные диаграммы на фиг.2). Указанное приводит к тому, что D-триггеры 1 и 2 получают разрешение на начало счета строго в паузах между информационными импульсами и только после того, как поочередно проследуют, по одному, импульсы из опережающей и запаздывающей последовательностей, каждый из которых сбрасывает в исходное нулевое состояние свой D-триггер 3 или 4. Это обеспечивает начало переключений D-триггеров 1, 2 от момента поступления импульсов опережающей последовательности, что необходимо для корректного выделения временных интервалов τ, определяющих искомый фазовый сдвиг. В процессе поступления на тактовые входы D-триггеров 1, 2 информационных импульсов происходят поимпульсные переключения указанных триггеров приводящие к появлению на их выходах Q1 и Q2 последовательностей с периодом следования 2Т и с сохранением искомого фазового сдвига. Полученные последовательности импульсов сравниваются путем выполнения логической операции «неравнозначность» - для этого служит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, в результате чего на выходе фазового детектора формируется последовательность импульсов с длительностями, равными временным интервалам τ и с частотой 1/Т, равной частоте следования информационных импульсов (предполагается, что частоты сравниваемых процессов равны).

Предложенное техническое решение, как это видно из вышеприведенного описания, свободно от недостатков, присущих прототипу: в фазовом детекторе исключается некорректное выделение временных интервалов при нарушении порядка поступления информационных импульсов. И таким образом исключается составляющая абсолютной погрешности оценки Δ интервалов τ, выражаемая как Δ=Т-2τ. Причем, как несложно понять из приведенного, погрешность Δ может быть весьма существенной при относительно больших периодах Т и малых сдвигах τ. Это легко видеть из выражения для относительной погрешности оценки, характерной для прототипа и других подобных устройств: δ = ( T τ − 2 ) 100 % . В ряде случаев, например при мониторинге расхождения шкал времени, отношение T τ может достигать десятков и сотен тысяч, что в случае некорректного выделения временных интервалов может привести к достаточно серьезным ошибкам.

Кроме того, в заявленном фазовом детекторе исключается погрешность выделения временных интервалов, вызванная задержкой формирования задних фронтов импульсов на выходе детектора. Последнее объясняется тем, что формирование заднего фронта выходного импульса в настоящем устройстве происходит в момент переключения одного из триггеров 1, 2 под действием импульса запаздывающей последовательности, и отсутствует цепь обратной связи, задерживающая момент формирования указанного заднего фронта, как это имеет место в прототипе.

Описанный фазовый детектор позволяет одновременно с фазовым сдвигом определять и период Т следования информационных импульсов: он равен длительности импульсов на одном из выходов Q1, Q2 D-триггеров 1, 2. Для измерения частоты или периода достаточно снять сигнал с одного из упомянутых выходов.

Фазовый детектор, схема которого приведена на фиг.1 (вариант 1), служит для определения модуля разности фаз. Результат представляется на выходе в виде импульса, длительность τ которого определяет указанную разность (фазовый сдвиг). В тех же случаях, когда требуется иметь информацию о знаке фазового сдвига, схема может быть дополнена D-триггером 13, как показано на фиг.3 (вариант 2). В этой схеме предусмотрен дополнительный знаковый выход, на котором появляется высокий логический уровень, если последовательность импульсов на входе D1 опережает последовательность на входе D2 и низкий логический уровень - если последовательность импульсов на входе D2 опережает последовательность на входе D1. Для получения информации о фазовых сдвигах, в зависимости от их знака на различных выходах, то есть для формирования раздельно импульсов опережения и импульсов отставания, может быть использована схема, представленная на фиг.4 (вариант 3). Здесь импульсы опережения и отставания появляются на выходах детектора Выход «+» и Выход «-» соответственно. Опережение и отставание относятся к последовательности импульсов на входе D1 относительно последовательности на входе D2.

1. Цифровой фазовый детектор, содержащий первый и второй D-триггеры, тактовые входы которых являются соответственно первым и вторым информационными входами детектора, и логический элемент ИЛИ, выход которого соединен с объединенными входами обнуления первого и второго D-триггеров, отличающийся тем, что в него введены дополнительно третий и четвертый D-триггеры и логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом детектора, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с прямыми выходами первого и второго D-триггеров соответственно, D-входы первого и второго D-триггеров соединены с их инверсными выходами, первый вход элемента ИЛИ соединен с выходом третьего D-триггера, а второй вход соединен с выходом четвертого D-триггера, установочные входы третьего и четвертого D-триггеров объединены и составляют вход обнуления детектора, инверсные тактовые входы третьего и четвертого D-триггеров объединены с тактовыми входами соответственно первого и второго D-триггеров, D-входы третьего и четвертого D-триггеров являются входами фиксированного уровня логического нуля.

2. Цифровой фазовый детектор, содержащий первый и второй D-триггеры, тактовые входы которых являются соответственно первым и вторым информационными входами детектора, и логический элемент ИЛИ, выход которого соединен с объединенными входами обнуления первого и второго D-триггеров, отличающийся тем, что в него введены дополнительно третий, четвертый, пятый D-триггеры и логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом детектора, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с прямыми выходами первого и второго D-триггеров соответственно, D-входы первого и второго D-триггеров соединены с их инверсными выходами, первый вход элемента ИЛИ соединен с выходом третьего D-триггера, а второй вход соединен с выходом четвертого D-триггера, установочные входы третьего и четвертого D-триггеров объединены и составляют вход обнуления детектора, инверсные тактовые входы третьего и четвертого D-триггеров объединены с тактовыми входами соответственно первого и второго D-триггеров, D-входы третьего и четвертого D-триггеров являются входами фиксированного уровня логического нуля, D-вход пятого D-триггера соединен с прямым выходом первого D-триггера, а тактовый вход пятого D-триггера соединен с прямым выходом второго D-триггера, выход пятого D-триггера является знаковым выходом детектора.

3. Цифровой фазовый детектор, содержащий первый и второй D-триггеры, тактовые входы которых являются соответственно первым и вторым информационными входами детектора, и логический элемент ИЛИ, выход которого соединен с объединенными входами обнуления первого и второго D-триггеров, отличающийся тем, что в него введены дополнительно третий, четвертый, пятый D-триггеры, логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и демультиплексор, выходы которого являются первым и вторым выходами детектора, информационный вход демультиплексора соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены с прямыми выходами первого и второго D-триггеров соответственно, D-входы первого и второго D-триггеров соединены с их инверсными выходами, первый вход элемента ИЛИ соединен с выходом третьего D-триггера, а второй вход соединен с выходом четвертого D-триггера, установочные входы третьего и четвертого D-триггеров объединены и составляют вход обнуления детектора, инверсные тактовые входы третьего и четвертого D-триггеров объединены с тактовыми входами соответственно первого и второго D-триггеров, D-входы третьего и четвертого D-триггеров являются входами фиксированного уровня логического нуля, D-вход пятого D-триггера соединен с прямым выходом первого D-триггера, а тактовый вход пятого D-триггера соединен с прямым выходом второго D-триггера, выход пятого D-триггера соединен с адресным входом демультиплексора.

4. Цифровой фазовый детектор, по п.3, отличающийся тем, что демультиплексор состоит из двух логических элементов И и одного инвертора, вход которого объединен с первым входом первого элемента И и является адресным входом демультиплексора, информационным входом которого являются объединенные вторые входы элементов И, первый вход второго элемента И соединен с выходом инвертора, выходами демультиплексора являются выходы элементов И.