Устройство для синхронизации параметров подключаемых на параллельную работу генераторов

Иллюстрации

Показать всеИзобретение относится к измерительной технике и может быть использовано при синхронизации по частоте подключаемых на параллельную работу генераторов, под которой понимается подключение их на общую нагрузку. Техническим результатом является повышение точности определения рассогласования амплитуд, частот и фаз подключаемых на параллельную работу генераторов и, как следствие, снижение погрешности синхронизации данных параметров бортового сетевого напряжения за счет устранения динамической составляющей погрешности. Результат достигается тем, что устройство для синхронизации параметров подключаемых на параллельную работу генераторов содержит два устройства деления, два компаратора с исполнительным элементом на выходе, которые образуют совместно первый блок регулирования, общий вычитатель, амплитудный детектор, соединенный с выходом опорного генератора и включающий дифференциатор, вычитатель, интегратор, элемент задержки сигнала, два умножителя, блок извлечения корня и два дополнительных амплитудных детектора. 2 ил.

Реферат

Изобретение относится к измерительной технике и может быть использовано при синхронизации по частоте подключаемых на параллельную работу генераторов, под которой понимается подключение их на общую нагрузку. Необходимость в параллельной работе возникает при переменном характере нагрузки, а также для повышения надежности электроснабжения потребителей. Идеальные условия для включения генераторов на параллельную работу (точная синхронизация) - это равенство частоты, напряжения, порядка чередования фаз и углов фазового сдвига на каждом генераторе. Коммутация на сборную шину производится после входа этих параметров в предварительно заданную зону уставок - окно синхронизации. Включение на параллельную работу без точного соблюдения перечисленных условий (грубая синхронизация) сопровождается сильными толчками момента и бросками тока.

Известно реле разности частот подключаемых на параллельную работу генераторов [Патент RU №2460193, H02J 3/40, опубл. 27.08.2012], содержащее вычитатель, два компаратора, информационные входы которых соединены, а входы уставок подключены к входам задания опорного напряжения устройства, и два исполнительных элемента, инвертор, третий компаратор и одновибратор, элемент задержки сигнала, два дифференциатора, интегратор, умножитель, блок извлечения корня и делитель, причем входы вычитателя соединены с входами реле разности частот, а выход подключен через элемент задержки сигнала к первому входу делителя, ко второму входу вычитателя подключены также вход первого дифференциатора и вход интегратора, выходы которых соединены со входами умножителя, выход последнего соединен через инвертор и блок извлечения корня со вторым входом делителя, выход которого соединен через второй дифференциатор с информационными входами компараторов, выходы "больше" и "меньше" которых соединены соответственно с входами исполнительных элементов, а входы синхронизации через одновибратор и третий компаратор соединены со вторым входом вычитателя.

Недостатком данного устройства является его ограниченные функциональные возможности, поскольку данное устройство предназначено лишь только для синхронизации подключаемых на параллельную работу генераторов по частоте при условии совпадения синхронизируемого и опорного генераторов по амплитуде и фазе. В общем же случае при подключении на параллельную работу генераторов возникает их рассинхронизация по всем параметрам синусоидальных сигналов: амплитуде, частоте и фазе. В случае включения на параллельную работу при неравенстве амплитуд, частот или фаз один из агрегатов будет иметь некоторый запас избыточной кинетической энергии, под действием которой его ротор начнет опережать ротор другого и, таким образом, будет воспринимать уравнительную активную мощность, определяемую значениями тока и ЭДС в переходном режиме. В итоге данное ограничение функционалых возможностей приводит также к появлению динамической погрешности измерения частоты.

Известно реле разности фаз подключаемых на параллельную работу генераторов [Патент RU №2460192, H02J 3/40, опубл. 27.08.2012], содержащее вычитатель, три компаратора, одновибратор, элемент задержки сигнала, дифференциатор, интегратор, умножитель, делитель, инвертор и два исполнительных элемента, входы которых соединены с выходами первого и второго компараторов, информационные входы которых объединены и подключены к выходу делителя, первый вход которого через элемент задержки сигнала соединен с выходом вычитателя, оба входа вычитателя подключены к входам реле разности фаз, входы опорного напряжения компараторов подключены к соответствующим входам задания уставок реле разности фаз, а входы синхронизации первого и второго компараторов объединены и через одновибратор и третий компаратор соединены вторым входом вычитателя, а также с входом интегратора, дифференциатора, выход интегратора и дифференциатора подключены к входам умножителя, выход которого через инвертор и блок извлечения корня соединены со вторым входом делителя.

Недостатком данного устройства является его ограниченные функциональные возможности, поскольку данное устройство предназначено лишь только для синхронизации подключаемых на параллельную работу генераторов по фазе при условии совпадения синхронизируемого и опорного генераторов по амплитуде и частоте. В общем же случае при подключении на параллельную работу генераторов возникает их рассинхронизация по всем параметрам синусоидальных сигналов: амплитуде, частоте и фазе. В случае включения на параллельную работу при неравенстве амплитуд, частот или фаз один из агрегатов будет иметь некоторый запас избыточной кинетической энергии, под действием которой его ротор начнет опережать ротор другого и, таким образом, будет воспринимать уравнительную активную мощность, определяемую значениями тока и ЭДС в переходном режиме. В итоге данное ограничение функциональных возможностей приводит также к появлению динамической погрешности измерения фазы.

Наиболее близким к предлагаемому изобретению является реле разности амплитуд подключаемых на параллельную работу генераторов [Патент №2459338, H02J 3/40, опубл. 20.08.2012], содержащее два вычитателя, два компаратора с исполнительным элементом на выходе и амплитудный детектор, а амплитудный детектор содержит дифференциатор, интегратор, два элемента задержки сигнала, два умножителя, два устройства деления и блок извлечения корня, причем входы первого вычитателя соединены с входами реле разности амплитуд, а выход соединен с первым входом амплитудного детектора, второй вход амплитудного детектора соединен со вторым входом первого вычитателя, который соединен со входом дифференциатора, интегратора и к обоим входам первого умножителя, выход последнего соединен через второй элемент задержки с первым входом второго вычитателя, а выход дифференциатора и интегратора подключены к входам второго умножителя, выход которого соединен со вторым входом второго вычитателя, выход последнего соединен через блок извлечения корня с входом делителя первого устройства деления, вход делимого которого соединен с выходом опорного генератора, а выход к входу делителя второго устройства деления, вход делимого второго устройства деления соединен через первый элемент задержки с первым входом амплитудного детектора, выход второго устройства деления является выходом амплитудного детектора и подключен к информационным входам первого и второго компараторов, входы опорного напряжения которых подключены к входам уставок реле разности амплитуд, выход второго компаратора подключен к входу второго исполнительного элемента.

Недостатком данного устройства является его ограниченные функциональные возможности, поскольку данное устройство предназначено лишь только для синхронизации подключаемых на параллельную работу генераторов по амплитуде при условии совпадения синхронизируемого и опорного генераторов по амплитуде и частоте. В общем же случае при подключении на параллельную работу генераторов возникает их рассинхронизация по всем параметрам синусоидальных сигналов: амплитуде, частоте и фазе. В случае включения на параллельную работу при неравенстве амплитуд, частот или фаз один из агрегатов будет иметь некоторый запас избыточной кинетической энергии, под действием которой его ротор начнет опережать ротор другого и, таким образом, будет воспринимать уравнительную активную мощность, определяемую значениями тока и ЭДС в переходном режиме. Данное ограничение функциональных возможностей приводит также к появлению динамической погрешности измерения амплитуд.

Задачей изобретения является расширение функциональных возможностей устройства за счет синхронизации не только по амплитуде, но и по частоте и фазе подключаемых на параллельную работу генераторов. Техническим результатом является повышение точности определения рассогласования амплитуд, частот и фаз подключаемых на параллельную работу генераторов и, как следствие, снижение погрешности синхронизации данных параметров бортового сетевого напряжения за счет устранения динамической составляющей погрешности.

Решение задачи достигается тем, что в устройство для синхронизации параметров подключаемых на параллельную работу генераторов, которое содержит два устройства деления, два компаратора с исполнительным элементом на выходе, которые образуют совместно первый блок регулирования, общий вычитатель, амплитудный детектор, соединенный с выходом опорного генератора и включающий дифференциатор, вычитатель, интегратор, элемент задержки сигнала, два умножителя, блок извлечения корня, причем вход амплитудного детектора соединен с входом дифференциатора, интегратора и с обоими входами первого умножителя, выход первого умножителя соединен через элемент задержки сигнала амплитудного детектора с входом уменьшаемого вычитателя амплитудного детектора, а выход дифференциатора амплитудного детектора и интегратора подключены к входам второго умножителя, выход которого соединен с входом вычитаемого вычитателя амплитудного детектора, выход последнего соединен через блок извлечения корня с первым выходом амплитудного детектора, входы опорного напряжения первого и второго компараторов первого блока регулирования подключены к входам уставок устройства для синхронизации параметров подключаемых на параллельную работу генераторов, причем в устройство дополнительно введены два амплитудных детектора, а также два входных адаптера и два вычислителя по каналам опорного и синхронизируемого генератора, причем каждый из входных адаптеров содержит ключ и дифференциатор, вход которого подключен к первому входу ключа и входу входного адаптера, а выход ко второму входу ключа, выход последнего соединен с первым выходом входного адаптера, второй выход которого соединен с выходом его дифференциатора, а вход управления ключа соединен с входом управления входного адаптера, первый выход первого входного адаптера соединен с входом первого, а выход второго входного адаптера с входом третьего амплитудного детектора, кроме этого блок управления, два дополнительных блока регулирования, информационный вход каждого блока регулирования соединен также с информационным входом исполнительного элемента блока регулирования, причем вход второго амплитудного детектора подключен к выходу опорного генератора, выход блока извлечения корня амплитудного детектора соединен с его первым выходом, второй выход которого с выходом его элемента задержки, первый выход первого амплитудного детектора подключен к входу уменьшаемого первого общего вычитателя, а третьего - к его входу вычитаемого, а выход первого общего вычитателя соединен с информационным входом первого блока регулирования и с входом делимого общего устройства деления, вход делителя которого соединен с первым выходом второго амплитудного детектора, а выход общего устройства деления подключен к информационному входу второго блока регулирования, причем каждый из вычислителей содержит вычитатель, блок извлечения корня и устройство деления, выход которого соединен с выходом вычислителя, а вход делителя устройства деления подключен к выходу вычитателя вычислителя, вход уменьшаемого которого соединен с первым его входом, который подключен к первому выходу второго амплитудного детектора, а вход вычитаемого вычитателя вычислителя соединен с вторым его входом, который подключен к второму выходу первого амплитудного детектора, вход делимого устройства деления соединен с третьим входом вычислителя, который подключен ко второму выходу соответствующего входного адаптера, выход первого вычислителя подключен к входу уменьшаемого второго общего вычитателя, вход вычитаемого которого соединен с выходом второго вычислителя, а выход второго общего вычитателя через общий интегратор с информационным входом третьего блока регулирования, выход "К ключам" блока управления подключен к входам управления обоих входных адаптеров, вход синхронизации каждого блока регулирования подключен к соответствующему выходу "Синхросигнал" блока управления, а выходы компараторов блоков регулирования объединены на элементе "ИЛИ", выход которого через последовательно соединенные элемент задержки сигналов и одновибратор с выходом блока регулирования, который подключен к входу блока управления.

Сравнение заявляемого технического решения с прототипом позволяет установить соответствие его критерию "новизна".

Преимущество предлагаемого устройства для синхронизации параметров подключаемых на параллельную работу генераторов заключается в его универсальности, позволяющей определять рассогласование между амплитудой, фазой и частотой двух параллельно работающих генераторов, с сохранением преимущества устройства-прототипа, которое состоит в повышенной точности измерения рассогласования фаз и частоты, и некоторым снижением точности детектирования амплитуд. Повышение точности измерения рассогласования амплитуды достигается как за счет изменения порядка операции детектирования и определения разности на переменном напряжении, так и за счет повышения точности детектирования путем математической реализации данной процедуры.

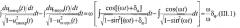

На фиг. 1 приведена структурная схема устройства для синхронизации по амплитуде подключаемых на параллельную работу генераторов, а на фиг. 2 приведен пример реализации блока управления 26.

Устройство для синхронизации параметров подключаемых на параллельную работу синхронизируемого генератора (СГ) и опорного генератора (ОГ) (фиг.1) содержит два вычислителя 1, 1′, состоящие из вычитателя 2, блока извлечения корня 3, устройства деления 4, а также три амплитудных детектора АД1 5, АД2 5′, АД3 5′′, каждый из которых включает вычитатель 6, дифференциатор 7 и интегратор 8, два умножителя 9, 10 и элемент задержки сигнала 11, блок извлечения корня 12, кроме этого два общих вычитателя 13, 14, общее устройство деления 15, общий интегратор 16, три узла регулирования 17.1, 17.2, 17.3, в каждый из которых входит два компаратора Κ1 18 и K2 18′, два исполнительных элемента ИЭ1 19 и ИЭ2 19′, элемент ИЛИ 20, элемент задержки сигналов τИЭ 21, одновибратор ОВ 22, кроме этого устройство содержит два входных адаптера BA1 23, ВА2 23′, каждый из которых включает дифференциатор 24 и ключ 25, и блок управления 26.

Входы устройства (выходы опорного ОГ и синхронизируемого СГ генераторов) подключены к входу первого BA1 23 и второго ВА2 23′ входного адаптера, к выходу опорного ОГ также подключен вход второго амплитудного детектора АД2 5′, первый выход которого соединен с входом делителя общего устройства деления 15, а второй выход с первыми входами вычислителей Выч.1 1, Выч.2 1′. Выход общего устройства деления 15 соединен с информационным входом второго узла регулирования 17.2.

Вход каждого входного адаптера BA1 23 (ВА2 23′) соединен с входом его дифференциатора 24 и с первым входом его ключа 25, выход которого соединен с первым выходом входного адаптера BA1 23 (ВА2 23′). Ко второму входу ключа 25 подключен выход дифференциатора 24 и второй выход входного адаптера BA1 23 (ВА2 23′), вход управления которого соединен с входом управления его ключа S 25. Первый выход каждого входного адаптера подключен к входу первого (третьего) амплитудного детектора АД1 5 (АД3 5′′). К входу каждого амплитудного детектора АД1 5, АД2 5′, АД3 5′′ подключен дифференциатор 7 амплитудного детектора, интегратор 8 и оба входа первого умножителя 9. Выходы дифференциатора 7 и интегратора 8 подключены к входам второго умножителя 10. Выход второго умножителя 10 соединен с входом вычитаемого вычитателя 6 амплитудного детектора, вход уменьшаемого которого соединен с третьим выходом соответствующего амплитудного детектора и через элемент задержки сигнала 11 амплитудного детектора соединен с выходом первого умножителя сигналов 9. Выход вычитателя 6 амплитудного детектора соединен со вторым выходом амплитудного детектора 5 (5′, 5′′) и через блок извлечения корня 12 соединен с первым выходом амплитудного детектора 5 (5′, 5′′). Первый выход первого амплитудного детектора 5 соединен с входом уменьшаемого первого общего вычитателя 13, к входу вычитаемого которого подключен первый выход третьего амплитудного детектора АД3 5′′. Выход первого общего вычитателя 13 соединен с входом делимого общего делителя 15. Третий выход первого АД1 5 (третьего АД3 5′′) амплитудного детектора соединен со вторым входом соответственно первого Выч.1 1 (второго Выч.2 1′) вычислителя, к которому подключен вход вычитаемого его вычитателя 2. Первый вход обоих вычислителей Выч.1 1 (Выч.2 1′) соединен с входом уменьшаемого его вычитателя 2, выход которого через блок извлечения корня 3 соединен со входом делителя устройства деления 4, вход делимого которого соединен с третьим входом вычислителя Выч.1 1 (Выч.2 1′), который для первого Выч.1 1 (второго Выч.2 1′) вычислителя соединен с вторым выходом первого ΒΑ1 (второго ВА2) входного адаптера 23 (23′). Выход устройства деления 4 обоих вычислителей Выч.1 1 (Выч.2 1′) соединен с его выходом, который для первого вычислителя Выч.1 1 подключен к входу уменьшаемого второго общего вычитателя 14, а для второго вычислителя Выч.2 1′ к входу вычитаемого второго общего вычитателя 14. Выход второго общего вычитателя 14 через общий интегратор 16 соединен с информационным входом третьего узла регулирования 17.3.

Выход управления блока управления 26 соединен с входом управления обоих входных адаптеров BA1 23, ВА2 23′, а выходы синхронизации блока управления 26 соединены с входами синхронизации соответствующего узла регулирования 17.1, 17.2, 17.3.

Информационный вход узлов регулирования 17.1, 17.2, 17.3 соединен с информационными входами компараторов Κ1 18, K2 18′ и исполнительных элементов 19, 19′. Входы уставки компараторов Κ1 18, K2 18′ подключены к входам задания соответствующего опорного напряжения Uоп1 и Uоп2, а выходы компараторов Κ1 18, K2 18′, объединенные на элементе "ИЛИ" 20, подключены через последовательно соединенные элемент задержки τИэ 21 и одновибратор ОВ 22 с выходом узла регулирования 17.1 (17.2), который соединен с соответствующим входом блока управления 26, входы "СБРОС" и "ПУСК" которого подключены к соответствующим входам управления устройства для синхронизации параметров подключаемых на параллельную работу генераторов.

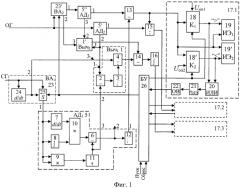

Блок управления 26 может быть, например, реализован в виде, приведенном на фиг. 2, и включать генератор импульсов 27, четыре элемента "И" И0 28, И1 29, И2 30, И3 31, четыре R-S триггера Т0 32, Т1 33, Т2 34, Т3 35, три регистра сдвига PC1 36, РС2 37, РС3 38.

Блок управления 26 должен последовательно на выходах "Синхронизация" формировать импульсы для синхронизации работы компараторов Κ1 18, K2 18′ специализированных выходных узлов регулирования, которые предназначены для регулирования соответственно амплитуды 17.1, частоты 17.2 и фазы 17.3, а также при определении рассинхронизации частоты (второй этап функционирования устройства) на выходе "К ключу" формировать импульс управления ключом S 25 для образования соответствующей структуры при выделении рассогласования частоты.

Устройство для синхронизации параметров подключаемых на параллельную работу генераторов работает следующим образом.

Входные синусоидальные напряжения Uсинх(t) от синхронизируемого генератора СГ и Uопор(t) от опорного генератора ОГ, отличающиеся друг от друга по амплитуде А, частоте ω и фазе φ, поступают на входы синхронизируемого и опорного генераторов.

По сигналу "ПУСК" блока управления 26 начинается процесс измерения и синхронизации параметров подключаемых на параллельную работу генераторов. Сигнал "ПУСК" пройдя через открытый в исходном состоянии элемент "И0" 28 взводит триггер Т0 32 и включает генератор импульсов ГИ 27. При поступлении на вход блока управления 26 импульса от узла регистрации 17.1 (17.2) (для первого триггера Т1 данный импульс совпадает с сигналом "ПУСК") взводится триггер Τ1 33 (Т2 34, Т3 35), который открывает элемент "И1" 29 ("И2" 30, "И3" 31). Через открытые элементы "И1" 29 ("И2" 30, "И3" 31) на тактовый вход регистра сдвига PC1 36 (РС2 37, РС3 38) поступают импульсы от генератора импульсов 27. Через заданное количество тактов на соответствующем выходе регистра сдвига PC1 33 (РС2 34, РС3 35) формируется задержанный импульс, который является синхроимпульсом для компараторов K1 18, K2 18′ узла регулирования 17.1 (17.2, 17.3).

Исходное состояние предлагаемого устройства для синхронизации параметров подключаемых на параллельную работу генераторов определяется установкой блока управления 26 в исходное состояние, которое задается сигналом по входам R триггеров T0, T1, Т2, T3 и PC1, РС2, РС3. Данные связи не изображены на фиг. 2.

I. В предлагаемом устройстве при включении генераторов на параллельную работу на первом этапе определяется рассогласование амплитуд. При этом учтем, что при неравенстве амплитуд напряжение опорного генератора имеет вид

а синхронизируемого

где A0 - амплитуда опорного генератора, ΔA - рассинхронизация (разница) амплитуд синхронизируемого и опорного генераторов; ω - круговая частота опорного генератора, δω - рассинхронизация (разница) частот синхронизируемого и опорного генераторов; δφ - рассинхронизация фазы синхронизируемого генератора относительно опорного генератора; t - время.

Продетектировав напряжение опорного I.1 и синхронизируемого I.2 генераторов, можно определить величину рассинхронизации амплитуд генераторов ΔA. Для детектирования амплитуды опорного генератора воспользуемся при этом известную из тригонометрии формулу

Первое слагаемое выражения (I.3) можно получить путем перемножения выходного сигнала опорного генератора

Для формирования второго слагаемого выражения I.3 продифференцируем выходной сигнал опорного генератора. При этом получим

d[A0sin(ωt)]/dt=d[A0sin(ωt)]/dt=A0ωcos(ωt).

А после интегрирования выходного сигнал опорного генератора получаем

Перемножив данные выражения, получаем

Вычтя из выражения I.4 выражение I.5, получаем в соответствии с выражением I.3 квадрат амплитуды опорного генератора A 0 2 . Если извлечь квадратный корень из полученного результата, то в результате получится амплитуда опорного сигнала.

Аналогично определяется амплитуда и синхронизируемого генератора A0+ΔA.

Вычтя из амплитуды синхронизируемого генератора амплитуду опорного генератора, получаем ΔA. Таким образом, используя высокоточные математические операции, можно осуществить детектирование ΔА, не используя стандартных детекторов, которые характеризуются сами по себе низким качеством детектирования (большая инструментальная погрешность). Реализовав полученный алгоритм в компьютере или в виде структуры устройства в соответствии с выражением

,

можно определить рассинхронизацию амплитуд подключаемых на параллельную работу двух генераторов.

Так, для определения рассинхронизации амплитуд ΔA через ключ S 25, находящийся при этом в исходном состоянии, входной сигнал с СГ (ОГ) поступает непосредственно на первый выход соответствующего входного адаптера BA1 23 (ВА2 23′) и далее на информационный вход амплитудных детекторов АД1 5 и АД3 5′′. В данных амплитудных детекторах АД1 5 и АД3 5′′ сигналы опорного и синхронизируемого генераторов дифференцируются на дифференциаторе 7 и интегрируется на интеграторе 8 напряжение опорного генератора (синхронизируемого генератора), которое также перемножается на первом умножителе 9. Напряжения с выхода дифференциатора 7 и интегратора 8 перемножаются друг на друга на втором умножителе 10 и поступают на вход уменьшаемого вычитателя 6 амплитудного детектора 5 (5′), на вход вычитаемого которого синхронно поступает перемноженное на первом умножителе 9 само на себя выходное напряжение синхронного (опорного) генератора. Синхронность обеспечивается за счет задержки данного сигнала на элементе задержки τ 11. При этом на выходе вычитателя 6 амплитудного детектора 5 (5′′) формируется квадрат амплитуды напряжения опорного генератора. После извлечения корня квадратного из полученного результата в блоке извлечения корня 12 выходное напряжение первого амплитудного детектора АД1 5 поступает на вход уменьшаемого первого общего вычитателя 13, на вход вычитаемого которого поступает выходное напряжение третьего амплитудного детектора АД3 5′′, а выходное напряжение которого поступает на информационный вход первого узла регулирования 17.1. Таким образом, напряжение, пропорциональное величине рассогласования амплитуд синхронизируемых генераторов ΔA, поступает на информационные входы первого и второго компараторов Κ1 18, K2 18′. Данное напряжение в зависимости от знака рассогласования амплитуд синхронизируемых генераторов может быть как отрицательным, так и положительным, поэтому для того чтобы соответствующий исполнительный элемент ИЭ1 19 и ИЭ2 19′ выполнил действия по согласованию амплитуд синхронизируемых генераторов, компаратор 18 и 18′ определяет направления этого действия, а величина регулирования амплитуды для узла регистрации 17.1 определяется величиной рассинхронизации по амплитуде ΔA. На выходе узлов регистрации 17.1 (17.2) формируются также выходные сигналы на элементе "ИЛИ" 20 от сигналов срабатывания компараторов K1 18 или K2 18′, задержанные на элементе задержки сигнала τИЭ 21 и сформированные на одновибраторе 22. Значение времени задержки сигнала на элементе τИЭ 21 выбирается немного больше времени регулирования исполнительных элементов ИЭ1 19 и ИЭ2 19′ соответствующего узла регистрации 17.1 (17.2).

II. После синхронизации амплитуд (ΔA=0) синхронизируемых напряжений импульс с выхода первого узла регулирования 17.1 поступает на вход 1 блока управления 26 и устройство переходит на этап определения рассинхронизации частот δω с последующей ее компенсацией при A0=A1=A2.

При этом синхронизируемое напряжение имеет вид

Uсинх=A0{sin[(ω+δω)t+δφ],

а опорное

Uопор=A0sinωt.

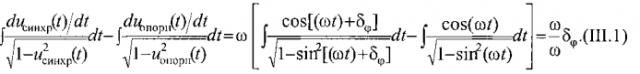

Взяв производную по времени от данных выражений, имеем

Выделив амплитуды сигналов uсинхр(t) и uопорн(t) аналогично предыдущему этапу функционирования устройства и вычтя

а затем, разделив на амплитуду опорного генератора A0, определяем значение δω.

Реализовав данную последовательность действий и выражения (II.1, II.2, II.3) в виде алгоритма в компьютере или в виде структуры устройства можно определить рассинхронизацию частот подключаемых на параллельную работу двух генераторов. При этом входное напряжение во входном адаптере ΒΑ1 (ВА2) по синхронизируемому (опорному) входу после дифференцирования элементом дифференцирования 24 (выражение II.1 и II.2) через ключ S 25, находящийся при этом в переключенном состоянии, поступает на информационный вход амплитудного детектора АД1 5 (АД3 5′′). Выделенные при этом амплитуды синхронизируемого и опорного сигналов после вычитания на вычитателе 13 (выражение II.3) и деления на величину амплитуды А0 опорного генератора, выделенную во втором амплитудном детекторе АД2 5′, в делителе 15 поступает на информационный вход узла регулирования 17.2 и при поступлении синхросигнала на его синхровход элементы ИЭ 19, ИЭ 19′ данного узла регулирования синхронизируют генераторы по частоте.

III. После синхронизации частоты (δω=0) синхронизируемых напряжений импульс с выхода второго узла регулирования 17.2 поступает на вход 2 блока управления 26. В этом случае входные адаптеры ВΑ1 23 и ВА2 23′ переходят в исходное состояние и входное напряжение непосредственно через ключ 25 входных адаптеров ΒΑ1 23 и ВА2 23′ поступает на вход соответствующего амплитудного детектора АД1 5 и АД3 5′′

При этом устройство переходит на этап определения рассинхронизации фаз δφ с последующей ее компенсацией при условии A0=A1=A2, ω1=ω2. В этом случае

имеем для синхронизируемого генератора

а аналогично для опорного генератора

т.е.

Воспользовавшись выражениями 512.1 и 470.2 [Двайт Г.Б. Таблицы интегралов и другие математические формулы. Наука. М.: 1977] (при m=1 и x=ωt+δφ для синхронизируемого генератора и x=ωt для опорного генератора), последнее выражение можно преобразовать к виду

По данному выражению определяется погрешность рассинхронизации по фазе δφ. При этом учтем, что на выходе 3 амплитудного детектора АД1 5 по сигналу синхронизируемого генератора формируется напряжение, равное и аналогично на выходе 3 АД3 5′′ по сигналу опорного генератора формируется напряжение

Для определения погрешности рассинхронизации по фазе δφ на вычитателе 2 первого вычислителя Выч.1 1 из квадрата амплитуды опорного генератора A 0 2 , который формируется на втором выходе амплитудного детектора АД2 5′, вычитается напряжение с выхода 3 первого амплитудного детектора АД1 5. Напряжение с выхода вычитателя 2 поступает на вход блока извлечения квадратного корня 3, выходное напряжение которого поступает на вход делителя устройства деления 4, а на вход делимого напряжение со второго выхода входного адаптера 23. Результат деления поступает на выход первого вычислителя Выч.1 1 и далее на вход уменьшаемого вычитателя 14. На вход вычитаемого вычитателя 14 поступает напряжение, сформированное аналогично вторым вычислителем Выч.2 1′, которое задается напряжениями на втором и третьем выходах третьего амплитудного детектора АД3 5′′, которые в свою очередь определяются напряжением с входа опорного генератора. В результате на выходе второго общего вычитателя 14 формируется напряжение, которое после интегрирования на интеграторе 16 реализует выражение III.1.

Данное напряжение поступает на информационный вход третьего узла регулирования 18.3. По синхросигналу с 3-го выхода блока управления 26 в узле регулирования 18.3 распознается на компараторах 19 и 19′ направление регулирования фазы, а по ее величине и величина регулирующего воздействия соответствующего исполнительного элемента ИЭ 20 (20′).

Следует отметить, что предложенное устройство может быть реализовано в виде одного CHIPа, в котором реализуются предлагаемые алгоритмы детектирования амплитуды, частоты и фазы.

Устройство для синхронизации параметров подключаемых на параллельную работу генераторов, содержащее два устройства деления, два компаратора с исполнительным элементом на выходе, которые образуют совместно первый блок регулирования, общий вычитатель, амплитудный детектор, соединенный с выходом опорного генератора и включающий дифференциатор, вычитатель, интегратор, элемент задержки сигнала, два умножителя, блок извлечения корня, причем вход амплитудного детектора соединен с входом дифференциатора, интегратора и с обоими входами первого умножителя, выход первого умножителя соединен через элемент задержки сигнала амплитудного детектора с входом уменьшаемого вычитателя амплитудного детектора, а выход дифференциатора амплитудного детектора и интегратора подключены к входам второго умножителя, выход которого соединен с входом вычитаемого вычитателя амплитудного детектора, выход последнего соединен через блок извлечения корня с первым выходом амплитудного детектора, входы опорного напряжения первого и второго компараторов первого блока регулирования подключены к входам уставок устройства для синхронизации параметров подключаемых на параллельную работу генераторов, отличающееся тем, что в устройство дополнительно введены два амплитудного детектора, а также два входных адаптера и два вычислителя по каналам опорного и синхронизируемого генератора, причем каждый из входных адаптеров содержит ключ и дифференциатор, вход которого подключен к первому входу ключа и входу входного адаптера, а выход ко второму входу ключа, выход последнего соединен с первым выходом входного адаптера, второй выход которого соединен с выходом его дифференциатора, а вход управления ключа соединен с входом управления входного адаптера, первый выход первого входного адаптера соединен с входом первого, а выход второго входного адаптера с входом третьего амплитудного детектора, кроме этого блок управления, два дополнительных блока регулирования, информационный вход каждого блока регулирования соединен также с информационным входом исполнительного элемента блока регулирования, причем вход второго амплитудного детектора подключен к выходу опорного генератора, выход блока извлечения корня амплитудного детектора соединен с его первым выходом, второй выход которого с выходом его элемента задержки, первый выход первого амплитудного детектора подключен к входу уменьшаемого первого общего вычитателя, а третьего - к его входу вычитаемого, а выход первого общего вычитателя соединен с информационным входом первого блока регулирования и с входом делимого общего устройства деления, вход делителя которого соединен с первым выходом второго амплитудного детектора, а выход общего устройства деления подключен к информационному входу второго блока регулирования, причем каждый из вычислителей содержит вычитатель, блок извлечения корня и устройство деления, выход которого соединен с выходом вычислителя, а вход делителя устройства деления подключен к выходу вычитателя вычислителя, вход уменьшаемого которого соединен с первым его входом, который подключен к первому выходу второго амплитудного детектора, а вход вычитаемого вычитателя вычислителя соединен с вторым его входом, который подключен к второму выходу первого амплитудного детектора, вход делимого устройства деления соединен с третьим входом вычислителя, который подключен ко второму выходу соответствующего входного адаптера, выход первого вычислителя подключен к входу уменьшаемого второго общего вычитателя, вход вычитаемого которого соединен с выходом второго вычислителя, а выход второго общего вычитателя через общий интегратор с информационным входом третьего блока регулирования, выход "К ключам" блока управления подключен к входам управления обоих входных адаптеров, вход синхронизации каждого блока регулирования подключен к соответствующему выходу "Синхросигнал" блока управления, а выходы компараторов блоков регулирования объединены на элементе "ИЛИ", выход которого соединен через последовательно соединенные элемент задержки сигналов и одновибратор с выходом блока регулирования, который подключен к входу блока управл