Устройство управления передачей данных по радиоканалу

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано в узлах коммутации сообщений сети передачи данных автоматизированной системы управления при управлении передачей данных по широковещательному многоточечному радиоканалу. Технический результат - повышение качества управления передачей данных в радиоканале. Указанный результат достигается в устройстве управления передачей данных по радиоканалу, которое включает, в частности, блок хранения отсчетов, коммутационную матрицу, первый и второй блоки обработки отсчетов, блок определения отсчета искомого ранга и логические элементы И и ИЛИ. Устройство управления передачей данных по радиоканалу обеспечивает ускоренную обработку полученной при тестировании радиоканала выборки сигналов для получения статистических характеристик радиоканала и, соответственно, повышение качества управления передачей данных в радиоканале. 10 ил.

Реферат

Изобретение относится к вычислительной технике и может быть использовано в узлах коммутации сообщений (пакетов) сети передачи данных (сети ПД) автоматизированной системы управления (АСУ) при управлении передачей данных по широковещательному многоточечному радиоканалу.

Известно устройство для управления передачей данных по радиоканалу (А.С. СССР №1162016.16, МПК5 H04L 7/00, 1985 г.), содержащее последовательно соединенные синхронизатор и первый элемент И, а также элемент задержки, элемент ИЛИ и последовательно соединенные счетчик и триггер цикла передачи, последовательно соединенные генератор случайных чисел, блок сравнения и триггер разрешения передачи, а также последовательно соединенные второй элемент И и формирователь импульсов, что позволяет увеличить степень использования пропускной способности канала. Однако данное устройство обладает недостаточной скоростью передачи по радиоканалу, в устройстве отсутствуют средства обработки выборки тестовых сигналов.

Наиболее близким по технической сущности и выполняемым функциям к заявляемому является устройство для управления передачей данных по радиоканалу (А.С. СССР №1319298, МПК5 H04L 7/00, опубликованное 23.06.87), содержащее генератор случайных чисел, синхронизатор, счетчик, первый элемент И, первый вход которого является управляющим входом устройства, RS-триггер, второй элемент И, блок сравнения, причем выход синхронизатора соединен с входом счетчика и первым входом второго элемента И, групповой выход счетчика соединен с счетным входом блока сравнения, вход случайных чисел которого соединен с групповым выходом генератора случайных чисел, выход первого элемента И соединен со входом генератора случайных чисел и нулевым входом RS-триггера, выход которого соединен со вторым входом второго элемента И, выход которого соединен с вторым входом первого элемента И, выход блока сравнения соединен с единичным входом RS-триггера. Устройство обеспечивает увеличение скорости передачи информации по радиоканалу.

Однако устройство-прототип не обеспечивает достаточную пропускную способность, так как в нем не реализована ускоренная обработка выборки тестовых сигналов для получения статистических характеристик радиоканала.

Целью изобретения является повышение качества управления передачи данных в радиоканале.

Поставленная цель достигается тем, что устройство управления передачей данных по радиоканалу, содержащее генератор случайных чисел, синхронизатор, счетчик, первый элемент И, первый вход которого является управляющим входом устройства, RS-триггер, второй элемент И, блок сравнения, причем выход синхронизатора соединен со входом счетчика и первым входом второго элемента И, групповой выход счетчика соединен со счетным входом блока сравнения, вход случайных чисел которого соединен с групповым выходом генератора случайных чисел, выход первого элемента И соединен со входом генератора случайных чисел, выход первого элемента И соединен с входом генератора случайных чисел и нулевым входом RS-триггера, выход которого соединен с вторым входом второго элемента И, выход которого соединен с вторым входом первого элемента И, выход блока сравнения соединен с единичным входом RS-триггера, дополнительно введены третий элемент И, блок хранения отсчетов, коммутационная матрица, n блоков разделения, первый и второй блоки обработки отсчетов, элемент ИЛИ и блок определения отсчета искомого ранга, причем первый информационный вход блока хранения отсчетов является информационным входом устройства, n выходов блока хранения отсчетов являются входами коммутационной матрицы, n-1 пар выходов которой соединены с соответствующими входами n-1 блоков разделения, первые выходы которых соединены с n-1 входами первого блока обработки отсчетов, а вторые выходы соединены с n-1 входами второго блока обработки отсчетов, при этом тактовые входы первого, второго блоков обработки отсчетов и блока определения отсчета искомого ранга соединены с тактовым выходом блока хранения отсчетов, причем информационные выходы первого и второго блоков обработки отсчетов соединены со вторым и первым входами элемента ИЛИ соответственно, выход которого соединен со вторым информационным входом блока хранения отсчетов, при этом счетный выход первого блока обработки отсчетов соединен с первым счетным входом блока определения отсчета искомого ранга, а счетный выход второго блока обработки отсчетов соединен со вторым счетным входом блока определения отсчета искомого ранга, первый и второй сигнальные выходы которого соединены с сигнальными входами второго и первого блоков обработки отсчетов соответственно, а первый и второй групповые управляющие выходы блока определения отсчета искомого ранга соединены с групповыми управляющими входами первого и второго блоков обработки отсчетов, третий сигнальный выход блока определения отсчета искомого ранга соединен со вторым входом третьего элемента И, первый вход которого соединен с выходом блока сравнения, выход третьего элемента И является управляющим выходом устройства, четвертый сигнальный выход блока определения отсчета искомого ранга соединен с сигнальным входом блока хранения отсчетов, а кодовый выход блока определения отсчета искомого ранга является кодовым выходом устройства.

Благодаря новой совокупности существенных признаков за счет введения блока хранения отсчетов, коммутационной матрицы, блоков разделения, первого и второго блоков обработки отсчетов, блока определения отсчета искомого ранга, третьего элемента И и элемента ИЛИ обеспечивается ускоренная обработка полученной при тестировании радиоканала выборки сигналов для получения статистических характеристик радиоканала и, соответственно, повышение качества управления передачей данных в радиоканале.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного изобретения условию патентоспособности «новизна». Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности «изобретательский уровень».

Заявляемое устройство поясняется чертежами, на которых показаны:

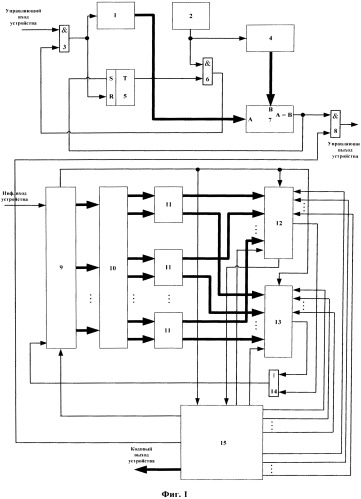

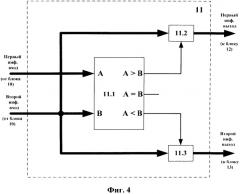

Фиг.1 - Функциональная схема устройства контроля передачи данных по радиоканалу;

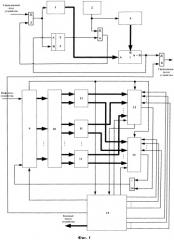

Фиг.2 - Схема блока хранения отсчетов;

Фиг.3 - Схема коммутационной матрицы;

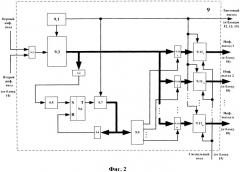

Фиг.4 - Схема блока разделения;

Фиг.5 - Схема первого блока обработки отсчетов;

Фиг.6 - Схема второго блока обработки отсчетов;

Фиг.7 - Схема блока определения отсчета искомого ранга;

Фиг.8 - Схема генератора случайных чисел;

Фиг.9 - Схема электронного ключа;

Фиг.10 - Схема распределителя импульсов.

Заявляемое устройство управления передачей данных по радиоканалу, показанное на фиг.1, состоит из: генератора случайных чисел 1, синхронизатора 2, первого элемента И 3, счетчика 4, RS-триггера 5, второго элемента И 6, блока сравнения 7, третьего элемента И 8, блока хранения отсчетов 9, коммутационной матрицы 10, блоков разделения 111-11m, первого блока обработки отсчетов 12, второго блока обработки отсчетов 13, элемента ИЛИ 14 и блока определения отсчета искомого ранга 15. Первый вход первого элемента И 3 является управляющим входом устройства. Выход синхронизатора 2 соединен со входом счетчика 4 и первым входом второго элемента И 6. Групповой выход счетчика 4 соединен со счетным входом блока сравнения 7. Вход случайных чисел блока сравнения 7 соединен с групповым выходом генератора случайных чисел 1. Выход первого элемента И 3 соединен со входом генератора случайных чисел 1 и входом сброса R RS-триггера 5. Вход установки S RS-триггера соединен с выходом блока сравнения 7 и первым входом третьего элемента И 8. Выход второго элемента И 6 соединен со вторым входом первого элемента И 3. Выход RS-триггера 5 соединен со вторым входом второго элемента И 6. При этом n выходов блока хранения отсчетов 9 являются входами коммутационной матрицы 10. n-1 пар выходов коммутационной матрицы 10 соединены с соответствующими входами n-1 блоков разделения 11. Первые выходы блоков разделения 11 соединены с п-1 входами первого блока обработки отсчетов 12, а вторые выходы соединены с n-1 входами второго блока обработки отсчетов 13. При этом тактовые входы первого 12, второго 13 блоков обработки отсчетов и блока определения отсчета искомого ранга 15 соединены с тактовым выходом блока хранения отсчетов 9. Информационные выходы первого 12 и второго 13 блоков обработки отсчетов соединены со вторым и первым входами элемента ИЛИ 14 соответственно. Выход элемента ИЛИ 14 соединен со вторым информационным входом блока хранения отсчетов 9. При этом счетный выход первого блока обработки отсчетов 12 соединен с первым счетным входом блока определения отсчета искомого ранга 15, а счетный выход второго блока обработки отсчетов 13 соединен со вторым счетным входом блока определения отсчета искомого ранга 15. Первый и второй сигнальные выходы блока определения отсчета искомого ранга 15 соединены с сигнальными входами второго 13 и первого 12 блоков обработки отсчетов соответственно. Первый и второй групповые управляющие выходы блока определения отсчета искомого ранга 15 соединены с групповыми управляющими входами первого 12 и второго 13 блоков обработки отсчетов. Третий сигнальный выход блока определения отсчета искомого ранга 15 соединен со вторым входом третьего элемента И 8. Первый вход третьего элемента И 8 соединен с выходом блока сравнения 7. Выход третьего элемента И является управляющим выходом устройства. Четвертый сигнальный выход блока определения отсчета искомого ранга 15 соединен с сигнальным входом блока хранения отсчетов 9. Кодовый выход блока определения отсчета искомого ранга 15 является кодовым выходом устройства.

Блок хранения отсчетов предназначен для хранения отсчетов выборки сигнала в параллельном коде до начала их обработки (включая последующие итерации). Может быть реализован в соответствии со схемой, показанной на фиг.2. Он состоит из генератора тактовых импульсов 9.1, первого элемента ИЛИ 9.2, преобразователя кода 9.3, второго элемента ИЛИ 9.4, формирователя коротких импульсов 9.5, RS-триггера 9.6, счетчика 9.7, третьего элемента ИЛИ 9.8, дешифратора 9.9, электронных ключей 9.101-9.10n, регистров сдвига 9.111-9.11n.

Коммутационная матрица предназначена для коммутации отсчетов выборки на соответствующие входы блоков разделения. Может быть реализована в соответствии со схемой, приведенной на фиг.3.

Блок разделения предназначен для реализации процедуры сравнения двух отсчетов выборки сигнала и передачи сравниваемого отсчета в один из блоков обработки отсчетов. Может быть реализован в соответствии со схемой, показанной на фиг.4. Он состоит из блока сравнения 11.1 и первого и второго электронных ключей 11.2 и 11.3.

Первый блок обработки отсчетов предназначен для формирования и промежуточного хранения последовательности отсчетов выборки, имеющих ранг, меньший ранга первого отсчета в последовательности. Может быть реализован в соответствии со схемой, показанной на фиг.5. Он состоит из распределителя импульсов 12.1, первых регистров сдвига 12.21-12.2m, первых элементов ИЛИ 12.31-12.3m, электронных ключей 12.41-12.4m, элементов задержки 12.51-12.5m, вторых регистров сдвига 12.61-12.6m, вторых элементов ИЛИ 12.71-12.7m, элементов И 12.81-12.8m, первого 12.9 и второго 12.10 многовходовых элементов ИЛИ.

Второй блок обработки отсчетов предназначен для формирования и промежуточного хранения последовательности отсчетов выборки, имеющих ранг, больший ранга первого отсчета в последовательности. Может быть реализован в соответствии со схемой, показанной на фиг.6. Он состоит из первых регистров сдвига 13.11-13.1m, первых элементов ИЛИ 13.21-13.2m, элементов задержки 13.31-13.3m, вторых регистров сдвига 13.41-13.4m, вторых элементов ИЛИ 13.51-13.5m, элементов И 13.61-13.6m и многовходового элемента ИЛИ 13.7.

Блок определения отсчета искомого ранга предназначен для управления процессом обработки выборки сигнала и отыскания отсчета требуемого ранга. Может быть реализован в соответствии со схемой, показанной на фиг.7. Он состоит из первого15.1, второго 15.5 и третьего 15.15 счетчиков, первого 15.2 и второго 15.12 формирователей коротких импульсов, первого 15.3 и второго 15.13 RS-триггеров, первого 15.4, второго 15.11 и третьего 15.14 электронных ключей, первого 15.6 и второго 15.16 дешифраторов, двоичного сумматора 15.8, элемента задержки 15.9, схемы сравнения 15.10, элемента ИЛИ 15.18.

Генератор случайных чисел 1 предназначен для случайного выбора момента начала передачи. Может быть реализован в соответствии со схемой, показанной на фиг.8. Он состоит из р D-триггеров (элементы 1.11-1.1р) и р генераторов шума (элементы 1.2,-1.2p). Тактовые входы С всех D-триггеров объединены и являются входом блока. Информационные входы D D-триггеров соединены с выходами генераторов шума 1.21-1.2р. Выходы D-триггеров 1.11-1.1р являются групповым выходом блока.

Генератор шума 1.21-1.2р предназначен для формирования случайно изменяющихся во времени выходных напряжений и описан -Элементы радиоэлектронных устройств. / Б.И. Короткое, - М.: Радио и связь, 1988, рис.7.24, с.107.

D-триггеры 1.11-1.1р описаны - Основы импульсной и цифровой техники / Под общей ред. A.M. Сидорова, - СПВВИУС, 1995, с.90-91.

Синхронизатор 2 представляет собой генератор тактовых импульсов и описан - Микросхемы и их применение: Справ.пособие / 1984, с.213, рис.7.6. Может быть реализован на интегральных микросхемах (ИМС) серий 511, 176.

Счетчик 4 описан - Журнал «Радио», 1987, 1, стр.43. Может быть реализован на ИМС КА561ИЕ15б (счетчик с переменным коэффициентом деления).

Блок сравнения 7 описан - Импульсные цифровые устройства /И.О. Лебедев, A.M. Сидоров. - Л.: ВАС, 1980, с.51, рис.2.33, 2.34. Может быть реализован на ИМС серий 133, 564.

Генератор тактовых импульсов 9.1 описан - Микросхемы и их применение: Справ.пособие / 1984, - с.213, рис.7.6. Может быть реализован на интегральных микросхемах (ИМС) серий 511, 176.

Счетчики 9.7, 15.1, 15.5, 15.15 известны и описаны - Основы импульсной и цифровой техники / Под общей ред. A.M. Сидорова, - СПВВИУС, 1995, рис.5.38, с.169-172.

Регистры сдвига 9.11, 12.2, 12.6, 13.1, 13.4 известны и описаны - Основы импульсной и цифровой техники / Под общей ред. A.M. Сидорова, - СПВВИУС, 1995, рис.5.28, с.158-159.

Формирователи импульсов 9.5, 15.2, 15.12 известны и описаны - Основы цифровой техники. /Л.А. Мальцева, - М.: Радио и связь, 1986, - рис.21, с.30.

Логические элементы И 12.8, 13.6 известны и описаны - Основы цифровой техники /Л.А. Мальцева, Э.М. Фромберг. - М.: Радио и связь, с.30-31. Могут быть реализованы на ИМС серий 133 и 564.

Логические элементы ИЛИ 9.2, 9.4, 9.8, 12.3, 12.7, 12.9, 12.10, 12.11, 13.2, 13.5, 13.7, 13.8, 15.18 известны и описаны - Основы импульсной и цифровой техники/ Под общей ред. A.M. Сидорова, -СПВВИУС, 1995, рис.2.4, с.39-41.

RS-триггеры 9.6, 15.3, 15.13 известны и описаны - Микросхемы и их применение: Справ.пособие / В.А. Батушев, В.Н. Вениаминов, В.Г. Ковалев и др. - М.: Радио и связь 1984, - с.122, рис.4.16. Могут быть реализованы на ИМС серий 133, 564.

Блоки сравнения 11.1, 15.10 известны и описаны - Популярные цифровые микросхемы: справочник. / В.Л. Шило, - Челябинск: Металлургия 1989, - с.261.

Элементы задержки 12.5, 13.3, 15.9 известны и описаны - Цифровые интегральные микросхемы: Справочник. / П.П. Мальцев и др., - М.: Радио и связь, 1994, с.52.

Дешифраторы 9.9, 15.6, 15.16 известны и описаны - Популярные цифровые микросхемы. Справочник / В.Л. Шило, - М.: Радио и связь, 1987, рис.1.95, с.130-142.

Преобразователь кода 9.3 известен и описан - Шило В.Л. Популярные цифровые микросхемы: Справочник. 2-е изд. - Челябинск: Металлургия, 1989, рис.2,52а, с.246-250.

Двоичный сумматор 15.8 известен и описан - Основы импульсной и цифровой техники / Под общей ред. А.М. Сидорова. - СПб: СПВВИУС: 1995, - рис.5.5, с.137-139.

Электронные ключи 9.10, 11.2, 11.3, 12.4, 15.4, 15.11, 15.14 могут быть реализованы в соответствии со схемой, приведенной на фиг.9.

Распределитель импульсов 12.1 может быть реализован в соответствии со схемой, приведенной на фиг.10.

Сущность изобретения заключается в следующем.

Для реализуемых в системах радиосвязи робастных методов обработки данных тестирования радиоканалов главной операцией является отыскание отсчета выборки с заданным рангом. Известные методы решения этой задачи требуют большого числа сравнений и, соответственно, временных затрат. В заявляемом устройстве вычисление ранга первого отсчета в выборке осуществляется путем сравнения со всеми остальными отсчетами. В последующих итерациях для отсчетов, заведомо не удовлетворяющих заданным условиям, ранг не вычисляется. При нахождении отсчета, потенциально выполняющего условия, вычисляется его ранг, и если условие не выполнено, пределы поиска сужаются. При этом затраты на вычисление ранга уменьшаются линейно с уменьшением интервала неопределенности.

Реализованный в заявляемом устройстве алгоритм отыскания отсчета выборки с заданным рангом позволяет снизить количество сравнений с 500000 до 5000 (при объеме выборки 1000 отсчетов).

Функциональная схема устройства, реализующего выполнение описанных функций контроля передачи данных по радиоканалу, приведена на фиг.1.

Заявленное устройство работает следующим образом.

При включении питания (схема питания не приводится) триггер 5 устанавливается в режим хранения логической единицы. Синхронизатор 2 выдает импульсы с интервалом времени, равным длительности интервала передачи пакета, при этом импульсы поступают на первый вход второго элемента И 6 и на тактовый вход счетчика 4, вызывая последовательную смену кодовых комбинаций на выходе счетчика 4 (число кодовых комбинаций равно числу «окон» в цикле передачи).

При возникновении необходимости в передаче пакета на управляющий вход устройства поступает сигнал запроса передачи (в виде уровня логической единицы). При этом очередной сигнал с выхода синхронизатора 2 (в виде единичного импульса) через открытый второй элемент И 6 поступает на управляющий вход первого элемента И 3. Так как первый элемент И 3 открыт по сигнальному входу сигналом запроса передачи, то единичный импульс с выхода первого элемента И 3 поступает на вход R триггера 5, переводя его в нулевое состояние, а также на управляющий вход генератора случайных чисел 1, который выдает в параллельном коде на второй сигнальный вход блока сравнения 7 кодовую комбинацию, соответствующую номеру окна в цикле передачи, выбранного для передачи пакета. При этом триггер 5 закрывает второй элемент И 6.

В момент совпадения кодовых комбинаций на первом и втором входах блока сравнения 7 последний выдает сигнал «Разрешение передачи» в виде единичного импульса через открытый третий элемент И 8 (третий элемент И 8 открыт, если работа алгоритма отыскания отсчета выборки тестовых сигналов завершена) на управляющий выход устройства, а также переводит триггер 5 в единичный режим (сигнал «Запрос передачи» с управляющего входа устройства снимается). Таким образом, устройство готово к передаче очередного пакета.

Отсчеты выборки в последовательном коде поступают от АЦП на первый информационный вход блока хранения отсчетов 9, где в параллельном коде записываются в соответствующие регистры сдвига. После этого данные отсчеты в параллельном коде поступают также на соответствующие входы коммутационной матрицы 10, в которой обеспечивается коммутация, требуемая для попарного сравнения данных отсчетов с первым из них.

С выходов коммутационной матрицы 10 попарно сгруппированные отсчеты (1-2, 1-3, 1-4, …, 1-n) поступают на входы соответствующих блоков разделения 111-11n, в которых осуществляются операции сравнения и в конечном итоге определение всех отсчетов, больших или меньших отсчета, первого в выборке.

В процессе первой итерации вся совокупность отсчетов выборки делится на две группы по отношению к первому отсчету выборки с рангом r1. Все отсчеты, имеющие ранг, меньший r1, записываются и хранятся в первом блоке обработки отсчетов 12. Соответственно, все отсчеты, имеющие ранг, больший r1, записываются и хранятся во втором блоке обработки отсчетов 13.

При этом в блоке определения отсчета искомого ранга 15 осуществляется сравнение ранга первого отсчета r1 с рангом, который является искомым (rиск). В зависимости от исхода сравнения дальнейшая работа идет либо с данными, хранящимися в блоке 12, либо с данными, хранящимися в блоке 13.

Например, если r1<rиск, то хранящиеся в блоке 13 отсчеты (ранг которых больше r1) в последовательном коде считываются на второй информационный вход блока хранения отсчетов 9 (соответственно, в блоке 12 данные обработки отсчетов обнуляются).

Далее осуществляется вторая итерация отыскания отсчета с заданным рангом (при этом количество отсчетов, записанных в регистры сдвига блока 9, может составлять от 0 до n-1).

В конечном итоге после завершения последней итерации кодовая комбинация, соответствующая найденному отсчету с искомым рангом, поступает с выхода блока 15 на кодовый выход устройства, при этом на третьем сигнальном выходе блока 15 появляется сигнал с уровнем логической единицы, открывающий по второму входу третий элемент И 8, сигнал «Разрешение передачи» поступает на управляющий выход устройства.

Блок хранения отсчетов 9, функциональная схема которого приведена на фиг.2, работает следующим образом.

При первой итерации отсчеты выборки поступают от АЦП на первый информационный вход блока 9 и далее через первый элемент ИЛИ 9.2 на информационный вход преобразователя кода 9.3. На тактовый вход преобразователя кода 9.3 поступает последовательность тактовых импульсов от генератора тактовых импульсов 9.1. При этом на выходе преобразователя кода 9.3 с периодичностью 1/n в параллельном коде появляются кодовые комбинации, соответствующие принятым отсчетам выборки. Так как все комбинации, соответствующие отсчетам, являются ненулевыми, периодически появляющийся на выходе второго элемента ИЛИ сигнал логической единицы поступает на вход формирователя импульсов 9.5, который коротким импульсом переводит RS-триггер 9.6 в режим хранения логической единицы. В свою очередь, триггер 9.6 подает на счетный вход двоичного счетчика 9.7 сигнал с уровнем логической единицы. При этом кодовая комбинация, поступающая с выхода счетчика 9.7 на вход дешифратора 9.9, вызывает появление сигнала с уровнем логической единицы на одном из его n выходов. Данный сигнал поступает на управляющий вход одного из n электронных ключей 9.10 и обеспечивает прохождение кодовой комбинации данного отсчета с выхода преобразователя кода 9.3 на вход соответствующего регистра сдвига 9.11. Одновременно кодовая комбинация с выхода счетчика 9.7 вызывает появление на выходе третьего элемента ИЛИ 9.8 сигнала с уровнем логической единицы, который переводит RS-триггер 9.6 в режим хранения логического нуля (до появления на выходе преобразователя кода 9.3 очередной кодовой комбинации, соответствующей очередному отсчету выборки).

Блок разделения 11, функциональная схема которого приведена на фиг.4, работает следующим образом.

С выходов коммутационной матрицы 10 на первые (А) входы всех блоков сравнения 11.1 поступает кодовая комбинация отсчета, первого в выборке отсчетов тестовых сигналов. На вторые (В) входы всех блоков сравнения 11.1 поступают соответствующие кодовые комбинации остальных отсчетов выборки. Если текущий отсчет больше первого (А<В), то сигнал с уровнем логической единицы с выхода «А<В» блока сравнения 11.1 открывает электронный ключ 11.3, при этом кодовая комбинация отсчета в параллельном коде поступает во второй блок обработки отсчетов 13. В противном случае (А>В, то есть текущий отсчет меньше первого) открывается электронный ключ 11.2, и кодовая комбинация отсчета поступает в первый блок обработки отсчетов 12.

Первый блок обработки отсчетов 12, функциональная схема которого приведена на фиг.5, работает следующим образом.

В результате обработки выборки тестовых сигналов в блоках разделения 111-llm (m-n-1) в некоторые регистры сдвига 12.21-12.2m будут записаны кодовые комбинации всех отсчетов выборки с рангом, меньшим ранга первого отсчета выборки r1. При этом остальные регистры сдвига будут пустыми. Для определения количества отсчетов, записанных в регистры сдвига первого блока обработки отсчетов 12 распределитель импульсов 12.1 выдает в цикле сигналы с уровнем логической единицы поочередно на управляющие входы электронных ключей 12.41-12.4m.

Если в соответствующий регистр сдвига 12.2i записана кодовая комбинация, то она через соответствующий электронный ключ 12.4i в параллельном коде поступает на входы многовходового элемента ИЛИ 12.10 и вызывает (так как является ненулевой) кратковременное появление на выходе данного элемента ИЛИ 12.10 сигнала с уровнем логической единицы, поступающего далее в блок определения отсчета искомого ранга 15. Опрос пустого сдвига регистра такого сигнала не дает. Следовательно, в блок 15 от блока 12 поступит столько сигналов с уровнем логической единицы, сколько отсчетов выборки имеют ранг, меньший r1.

Одновременно все кодовые комбинации отсчетов поступают на входы соответствующих регистров сдвига 12.61-12.6m и на соответствующие элементы ИЛИ 12.71-12.7m, вызывая появление сигналов с уровнем логической единицы на первых входах соответствующих элементов И 12.81-12.8m

Далее в зависимости от принятого блоком определения отсчета искомого ранга 15 решения, либо содержимое регистров сдвига 12.11-12.1m обнуляется (сигналом с уровнем логической единицы, поступающим от блока 15 на сигнальный вход первого блока обработки отсчетов 12), либо начинается вторая итерация обработки отсчетов, для чего поступающие на групповой управляющий вход от блока 15 сигналы с уровнем логической единицы обеспечивают поочередное считывание в последовательном коде всех кодовых комбинаций отсчетов, хранящихся в первом блоке обработки отсчетов 12 (то есть укороченной последовательности отсчетов), через элемент ИЛИ 12.9 и элемент ИЛИ 14 (фиг.1) в блок хранения отсчетов 9.

Второй блок обработки отсчетов 13, функциональная схема которого приведена на фиг.6, работает следующим образом.

В результате обработки выборки тестовых сигналов в блоках разделения 111-11m (m=n-1) в некоторые регистры сдвига 13.11-13.lm будут записаны кодовые комбинации всех отсчетов выборки с рангом, большим ранга первого отсчета выборки r1.

Одновременно все кодовые комбинации отсчетов поступают на входы соответствующих регистров сдвига 13.41-13.4m и на соответствующие элементы ИЛИ 13.51-13.5m, вызывая появление сигналов с уровнем логической единицы на первых входах соответствующих элементов И 13.61-13.6m.

Далее в зависимости от принятого блоком определения отсчета искомого ранга 15 решения, либо содержимое регистров сдвига 13.41-13.4m обнуляется (сигналом с уровнем логической единицы, поступающим от блока 15 на сигнальный вход второго блока обработки отсчетов 13), либо начинается вторая итерация обработки отсчетов, для чего поступающие на групповой управляющий вход от блока 15 сигналы с уровнем логической единицы обеспечивают поочередное считывание в последовательном коде всех кодовых комбинаций отсчетов, хранящихся во втором блоке обработки отсчетов 13 (то есть укороченной последовательности отсчетов), через элемент ИЛИ 13.7 и элемент ИЛИ 14 (фиг.1) в блок хранения отсчетов 9.

Блок определения отсчета искомого ранга 15, функциональная схема которого приведена на фиг.7, работает следующим образом. В данном блоке осуществляются следующие операции:

- определение ранга первого в выборке отсчета (r1);

- сравнение r1 с искомым рангом rиск;

- в зависимости от результатов предыдущей операции выбор одной из двух укороченных последовательностей отсчетов выборки для дальнейшей обработки;

- управление считыванием выбранной укороченной последовательности из блоков 12 или 13 в блок хранения отсчетов 9.

Поступающие на счетный вход блока 15 единичные импульсы от блока 12 определяют количество отсчетов выборки с ri<r1, записанных в регистре сдвига блока 12. После требуемой задержки элементом 15.9 на вход В блока сравнения 15.10 поступает кодовая комбинация, соответствующая рангу первого отсчета в выборке r1 (r1 определяется как количество отсчетов укороченной последовательности с ri<r1, увеличенное на единицу в сумматоре 15.8). На вход А блока сравнения 15.10 поступает кодовая комбинация, соответствующая искомому рангу rиск.

Если А>В (то есть rиск>r1), то дальнейшей обработке подлежит укороченная последовательность из отсчетов с рангом, большим, чем r1. При этом регистры сдвига блока 12 обнуляются сигналом с уровнем логической единицы с первого сигнального выхода блока 15, а также запускается цепь, состоящая из элементов 15.2-15.7, обеспечивающая считывание в последовательном коде из блока 13 в блок 9 данной укороченной последовательности.

При этом короткий единичный импульс с выхода формирователя импульсов 15.2 переводит RS-триггер 15.3 в режим хранения логической единицы. Сигнал с уровнем логической единицы с выхода триггера 15.3 открывает электронный ключ 15.4 на время прохождения требуемого количества тактовых импульсов, необходимых для полного цикла работы счетчика 15.5 и дешифратора 15.6. Последняя (единичная) кодовая комбинация, поступая с выхода счетчика 15.5 на вход элемента И 15.7, вызывает появление на его выходе сигнала с уровнем логической единицы, переводящего триггер 15.3 в режим хранения логического нуля.

В противном случае (если А<В, то есть rиск<r1) обнуляются регистры сдвига блока 13 (сигналом с уровнем логической единицы со второго сигнального выхода блока 15), запускается цепь считывания укороченной последовательности отсчетов из блока 12 (элементы 15.12-15.17).

В обоих случаях сигнал с уровнем логической единицы с выходов А>В или А<В блока сравнения 15.10 через элемент ИЛИ 15.18 поступает на четвертый сигнальный выход блока 15 и далее на сигнальный вход блока хранения отсчетов 9, обнуляя регистры сдвига данного блока.

Устройство управления передачей данных по радиоканалу, содержащее генератор случайных чисел, синхронизатор, счетчик, первый элемент И, первый вход которого является управляющим входом устройства, RS-триггер, второй элемент И, блок сравнения, причем выход синхронизатора соединен с входом счетчика и первым входом второго элемента И, групповой выход счетчика соединен со счетным входом блока сравнения, вход случайных чисел которого соединен с групповым выходом генератора случайных чисел, выход первого элемента И соединен со входом генератора случайных чисел и нулевым входом RS-триггера, выход которого соединен со вторым входом второго элемента И, выход которого соединен со вторым входом первого элемента И, выход блока сравнения соединен с единичным входом RS-триггера, отличающееся тем, что дополнительно введены третий элемент И, блок хранения отсчетов, коммутационная матрица, n блоков разделения, первый и второй блоки обработки отсчетов, элемент ИЛИ и блок определения отсчета искомого ранга, причем первый вход тестового сигнала блока хранения отсчетов является входом тестового сигнала устройства, n выходов блока хранения отсчетов являются входами коммутационной матрицы, n-1 пар выходов которой соединены с соответствующими входами n-1 блоков разделения, первые выходы которых соединены с n-1 входами первого блока обработки отсчетов, а вторые выходы соединены с n-1 входами второго блока обработки отсчетов, при этом тактовые входы первого, второго блоков обработки отсчетов и блока определения отсчета искомого ранга соединены с тактовым выходом блока хранения отсчетов, причем информационные выходы первого и второго блоков обработки отсчетов соединены со вторым и первым входами элемента ИЛИ соответственно, выход которого соединен со вторым входом тестового сигнала блока хранения отсчетов, при этом счетный выход первого блока обработки отсчетов соединен с первым счетным входом блока определения отсчета искомого ранга, а счетный выход второго блока обработки отсчетов соединен со вторым счетным входом блока определения отсчета искомого ранга, первый и второй сигнальные выходы которого соединены с сигнальными входами второго и первого блоков обработки отсчетов соответственно, а первый и второй групповые управляющие выходы блока определения отсчета искомого ранга соединены с групповыми управляющими входами первого и второго блоков обработки отсчетов, третий сигнальный выход блока определения отсчета искомого ранга соединен со вторым входом третьего элемента И, первый вход которого соединен с выходом блока сравнения, выход третьего элемента И является управляющим выходом устройства, четвертый сигнальный выход блока определения отсчета искомого ранга соединен с сигнальным входом блока хранения отсчетов, а кодовый выход блока определения отсчета искомого ранга является кодовым выходом устройства.