Способ изготовления статического оперативного запоминающего устройства и статическое оперативное запоминающее устройство (озу)

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в повышении помехоустойчивости ОЗУ путем уменьшения емкостей паразитных конденсаторов между элементами устройства. Способ изготовления статического оперативного запоминающего устройства включает размещение узлов хранения бита данных и шин чтения данных и шин записи данных в пространстве, причем ячейку памяти конструктивно разделяют на модули трех типов: модуль хранения бита данных, модуль порта записи и модуль порта чтения, причем модуль порта записи размещают отдельно от модуля хранения и подключают ко входу модуля хранения бита данных, а модуль порта чтения размещают отдельно от модуля хранения и подключают к выходу модуля хранения. 2 н. и 1 з.п. ф-лы, 3 ил.

Реферат

Изобретение относится к области вычислительной цифровой техники, а именно к вычислительным системам на основе микропроцессоров со статическим ОЗУ.

Известен способ записи и хранения данных в статическом оперативном запоминающем устройстве (ОЗУ), основанный на применении ячеек памяти с разными потенциалами на истоках n-канальных транзисторов ячейки памяти (Патент US №5,986,923 кл. G11C 11/00, опубл. 1999 г.).

Недостатком описанного способа является сложность системы управления питанием и необходимость трассировки дополнительных проводников питания внутри статического ОЗУ.

Наиболее близким по технической сути и достигаемому результату является способ изготовления статического ОЗУ, включающий размещение узлов хранения бита данных и шин чтения данных и шин записи данных в пространстве и разделение ячейки памяти на модули, которое осуществляется устройством, состоящим из ячейки памяти, имеющей транзисторы, соединенные между собой проводниками, а также битовую шину чтения, словарную шину чтения, битовые шины записи и словарную шину записи (Патент US №8294212, кл. H01L 27/11, опублик. 2003 г.).

Недостатком описанных выше способа и устройства является трассировка битовых шин записи вблизи узлов хранения бита данных в ячейках памяти или непосредственно над этими узлами, в результате чего из-за большой емкости указанных шин, управляемых мощными усилителями, в узлах хранения бита данных возникают помехи, которые способны изменить состояние ячейки, особенно в современных схемах, использующих пониженное напряжение питания, уменьшенные размеры транзисторов и обладающих вследствие этого низкой помехоустойчивостью.

Техническим результатом, ожидаемым от использования изобретения, является повышение помехоустойчивости ОЗУ путем уменьшения емкостей паразитных конденсаторов между элементами устройства.

Указанный технический результат достигается тем, что в способе изготовления статического оперативного запоминающего устройства, включающем размещение узлов хранения бита данных и шин чтения данных и шин записи данных в пространстве и разделение ячейки памяти на модули, согласно изобретению ячейку памяти конструктивно разделяют на модули трех типов: модуль хранения бита данных, модуль порта записи, и модуль порта чтения, причем модуль порта записи размещают отдельно от модуля хранения и подключают ко входу модуля хранения бита данных, а модуль порта чтения размещают отдельно от модуля хранения и подключают к выходу модуля хранения;

и тем, что каждый из трех модулей выполняют из транзисторов с пороговым напряжением больше или меньше порогового напряжения транзисторов в остальных модулях.

По описанному способу изготавливают устройство, состоящее из ячейки памяти, имеющей транзисторы, соединенные между собой проводниками, а также битовую шину чтения, словарную шину чтения, битовые шины записи и словарную шину записи, в котором согласно изобретению ячейка памяти выполнена из трех отдельно стоящих модулей, при этом модуль хранения бита данных имеет один парафазный вход и один однофазный выход, модуль порта чтения, расположенный с одной стороны модуля хранения бита данных и подключенный к выходу модуля хранения бита данных проводником, проложенным внутри модуля порта чтения на всю его ширину, и модулем порта записи, расположенным с другой стороны модуля хранения бита данных и подключенным ко входу модуля хранения бита данных проводниками, проложенными внутри модуля порта записи на всю его ширину.

В результате за счет разнесения битовых шин чтения и битовых шин записи в пространстве и вынесении их за пределы модуля хранения бита данных уменьшается взаимная емкость между этими шинами и узлами хранения бита данных, а следовательно, и амплитуда помех на узлах хранения бита данных.

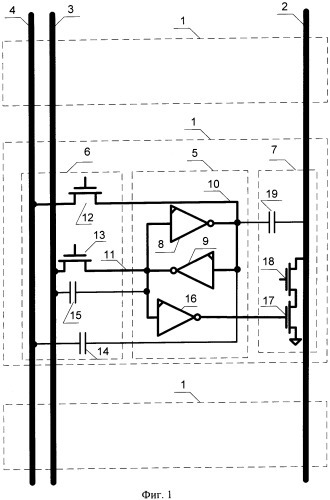

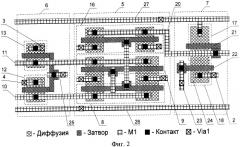

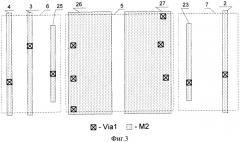

Изобретение поясняется чертежами, где на фиг.1 представлена схема способа обеспечения помехоустойчивости статического ОЗУ, на фиг.2 - конструкция нижних слоев устройства, реализующего способ, на фиг.3 - конструкция верхних слоев устройства, реализующего способ.

Столбец запоминающего массива составляют из ячеек памяти 1, через которые проводят сквозные вертикальные шины: битовая шина чтения 2, прямая битовая шина записи 3 и инверсная битовая шина записи 4. Ячейку памяти разделяют на три модуля: модуль хранения бита данных 5, модуль порта записи 6 и модуль порта чтения 7. В модуле хранения бита данных 5 два встречно включенных инвертора 8 и 9 соединяют между собой перекрестными связями, которые являются узлом хранения инверсного бита данных 10 и узлом хранения прямого бита данных 11. Инверсный бит данных записывают с инверсной битовой шины записи 4 через транзистор 12, а прямой бит данных записывают с прямой битовой шины записи 3 через транзистор 13. Транзисторы 12 и 13 размещают в модуле порта записи 6 и располагают данный модуль в стороне от модуля хранения бита данных 5, а прямую битовую шину записи 3 и инверсную битовую шину записи 4 проводят на максимальном удалении от модуля хранения бита данных 5. При таком способе взаимного расположения модуля хранения бита данных 5 и модуля порта записи 6 емкости паразитных конденсаторов 14 и 15 уменьшаются за счет удаления прямой битовой шины записи 3 и инверсной битовой шины записи 4 от инверторов 8 и 9, так как фрагменты узла хранения инверсного бита данных 10 и узла хранения прямого бита данных 11, которые при таком способе размещения проводников и транзисторов пересекаются в соседних слоях с прямой битовой шиной записи 3 и инверсной битовой шиной записи 4 или проходят в одном слое рядом с ними, обладают минимальной площадью. Поскольку паразитные конденсаторы 14 и 15, образованные пересечениями прямой битовой шиной 3 и инверсной битовой шиной 4 с узлом хранения инверсного бита данных 10 и узлом хранения прямого бита данных 11 или близким расположением прямой битовой шины 3 и инверсной битовой шины 4 с узлом хранения инверсного бита данных 10 и узлом хранения прямого бита данных 11, вносят существенный вклад в уровень помех в ячейке памяти, уменьшение их емкости заметно увеличивает помехоустойчивость ячейки и, следовательно, помехоустойчивость ОЗУ в целом. Через разделительный инвертор 16 записанный бит данных подают на вход модуля порта чтения 7, состоящего из двух транзисторов 17 и 18, и через них - на битовую шину чтения 2. Так как транзисторы 17 и 18 выделены в отдельный модуль порта чтения 7, разнесенный в пространстве с модулем хранения бита данных 5, емкость паразитного конденсатора 19 между битовой шиной чтения 2 и узлом хранения инверсного бита данных 10 мала, что увеличивает помехоустойчивость ячейки памяти и всего ОЗУ в целом.

Устройство для осуществления способа обеспечения помехоустойчивости статического ОЗУ состоит из модуля хранения бита данных 5, одного или более модуля порта записи 6 и одного или более модуля порта чтения 7. Модуль хранения 5 образуется двумя инверторами 8 и 9, соединенными перекрестными связями, которые являются узлом хранения инверсного бита данных 10 и узлом хранения прямого бита данных 11, и разделительного инвертора 16, управляющего выходом 20 модуля хранения бита данных 5. Бит данных записывается в модуль хранения бита данных 5 через модуль порта записи 6. Модуль порта записи 6 состоит из двух транзисторов 12 и 13, первый из которых соединяет инверсную битовую шину записи 4 с узлом хранения инверсного бита данных 10, а второй соединяет прямую битовую шину записи 3 с узлом хранения прямого бита данных 11. К выходу 20 разделительного инвертора 16 подключается модуль порта чтения 7. Модуль порта чтения 7 состоит из двух транзисторов 17 и 18. Затвор 21 транзистора 17 подключается к выходу 20 разделительного инвертора 16, затвор 22 транзистора 18 - к словарной шине чтения 23, а его сток 24 - к битовой шине чтения 2. На второй уровень металла выводятся прямая битовая шина записи 3 и инверсная битовая шина записи 4, битовая шина чтения 2, словарная шина чтения 23, словарная шина записи 25, шина питания 26 и шина земли 27. Шина земли 26 и шина питания 27 во втором слое металлизации полностью накрывают модуль хранения бита данных 5, обеспечивая таким образом его экранирование от помех, возникающих при переключении тока в любых сигнальных проводниках в остальных слоях металлизации, начиная с третьего.

Каждый из модулей, образующих ячейку памяти (модуль хранения бита данных 5, модуль порта записи 6 и модуль порта чтения 7), конструктивно выполняется отдельно от двух других. При этом узел хранения инверсного бита данных 10 и узел хранения прямого бита данных 11 выведены с одной стороны модуля хранения бита данных 5, а проводник в первом металле, образующий выход 20 разделительного инвертора 16, выведен с противоположной стороны модуля хранения бита данных 5. Та часть узла хранения инверсного бита данных 10 и узла хранения прямого бита данных 11, которая находится внутри модуля порта записи 6, проложена внутри этого модуля от его правой границы до левой. Таким образом, если модули порта записи 6 конструктивно располагаются с левой стороны от модуля хранения 5, то независимо от количества модулей порта записи 6 узел хранения инверсного бита данных 10 и узел хранения прямого бита данных 11 продлеваются автоматически при добавлении модулей порта записи 6. Та часть выхода 20 разделительного инвертора 16, которая находится внутри модуля порта чтения 7, проложена внутри этого модуля от его левой границы до правой. Таким образом, если модули порта чтения 7 конструктивно располагаются с правой стороны от модуля хранения бита данных 5, то независимо от количества модулей порта чтения 7 выход 20 продлевается автоматически при добавлении модулей порта чтения 7. Данное конструктивное решение позволяет произвольно изменять количество модулей порта чтения 7 и модулей порта записи 6 без изменения конструкции самих модулей порта записи 6 и порта чтения 7.

Вместе с разделением ячейки памяти на модули с разнесением модулей в пространстве используют следующий способ увеличения помехоустойчивости ОЗУ: каждый из трех модулей выполняют из транзисторов с пороговым напряжением больше или меньше порогового напряжения транзисторов в остальных модулях. Этим способом изменяют статическую переключательную характеристику таким образом, чтобы повысить помехоустойчивость ячейки памяти, а следовательно, и всего ОЗУ в целом.

Устройство работает следующим образом. Запись бита данных происходит при подаче сигнала словарной шины записи 25. Транзисторы 12 и 13 в этом режиме открыты и через них данные с прямой битовой шины записи 3 и инверсной битовой шины записи 4 поступают в модуль хранения бита данных 5 и записываются в узел хранения инверсного бита данных 10 и узел хранения прямого бита данных 11. При выключении сигнала на словарной шине записи 25 транзисторы 12 и 13 закрыты, и устройство находится в режиме хранения записанного бита данных.

В режиме хранения по прямой и инверсной битовым шинам записи 3 и 4 происходит передача сигналов в соседние ячейки памяти 1, а также производится предзаряд битовых шин записи 3 и 4. Переключение сигналов на указанных шинах приводит к наведению помех на близко расположенные проводники. Амплитуда помех, возникающих в узле хранения инверсного бита данных 10 и узле хранения прямого бита данных 11 при переключении тока в битовых шинах записи 3 и 4, прямо пропорциональна взаимным емкостям указанных шин с узлом хранения инверсного бита данных 10 и узлом хранения прямого бита данных 11. При увеличении расстояния между инверторами 8 и 9 и битовыми шинами записи 3 и 4 величина емкостей паразитных конденсаторов 14 и 15 уменьшается, вследствие чего снижается амплитуда помех. Дополнительно при разнесении в пространстве модуля порта записи 6 и модуля хранения бита данных 5 увеличивается величина собственной емкости узла хранения инверсного бита данных 10 и собственной емкости узла хранения прямого бита данных 11, что также приводит к уменьшению амплитуды помех и наводок на упомянутые узлы от других проводников. От источников помех, расположенных в слоях металлизации, начиная с третьего, модуль хранения экранирован шинами земли 27 и питания 26 во втором слое металлизации. Такими мерами увеличивают помехоустойчивость устройства и всего ОЗУ в целом.

Если через прямую битовую шину записи 3 в узел хранения прямого бита данных 11 была записана логическая единица, то на выходе 20 разделительного инвертора 16 установится логический ноль. Транзистор 17 порта чтения 7 окажется закрыт, и при подаче сигнала словарной шины чтения 23 на затвор 22 транзистора 18 потенциал предварительно заряженной до напряжения питания битовой шины чтения 2 останется высоким. Если через прямую битовую шину записи 3 в узел хранения прямого бита данных 11 был записан логический ноль, то на выходе 20 разделительного инвертора 16 установится логическая единица. При этом транзистор 17 открыт и при подаче сигнала словарной шины чтения 23 на затвор 22 транзистора 18 потенциал предварительно заряженной до напряжения питания битовой шины чтения 2 разрядится до уровня логического нуля. Таким образом из ячейки считывается записанный в нее бит данных.

Изобретение позволяет повысить помехоустойчивость статического ОЗУ путем разделения ячеек памяти на модули и разнесения модулей в пространстве.

1. Способ изготовления статического оперативного запоминающего устройства, включающий размещение узлов хранения бита данных и шин чтения данных и шин записи данных в пространстве, отличающийся тем, что ячейку памяти конструктивно разделяют на модули трех типов: модуль хранения бита данных, модуль порта записи, и модуль порта чтения, причем модуль порта записи размещают отдельно от модуля хранения и подключают ко входу модуля хранения бита данных, а модуль порта чтения размещают отдельно от модуля хранения и подключают к выходу модуля хранения.

2. Способ по п. 1, отличающийся тем, что каждый из трех модулей выполняют из транзисторов с пороговым напряжением больше или меньше порогового напряжения транзисторов в остальных модулях.

3. Статическое оперативное запоминающее устройство (ОЗУ), состоящее из ячейки памяти, имеющей транзисторы, соединенные между собой проводниками, а также битовую шину чтения, словарную шину чтения, битовые шины записи и словарную шину записи, отличающееся тем, что ячейка памяти выполнена из трех отдельно стоящих модулей, при этом модуль хранения бита данных имеет один парафазный вход и один однофазный выход, при этом модуль порта чтения расположен с одной стороны модуля хранения бита данных и подключен к выходу модуля хранения бита данных проводником, проложенным внутри модуля порта чтения на всю его ширину, а модуль порта записи расположен с другой стороны модуля хранения бита данных и подключен к входу модуля хранения бита данных проводниками, проложенными внутри модуля порта записи на всю его ширину.