Система управления космического аппарата

Иллюстрации

Показать всеИзобретение относится к системам автоматического управления (САУ) авиационно-космическими объектами, работающими, главным образом, в экстремальных условиях внешней среды. САУ содержит последовательно связанные массив датчиков, блок сбора информации (БСИ), управляющие вычислители (УВУ), переключатель каналов, управляемый блоком контроля. УВУ подключены к исполнительным органам объекта управления. САУ также содержит бесплатформенную инерциальную навигационную подсистему с соответствующими датчиками и (нейро-) вычислителями. САУ имеет сообщенные с БСИ типовую аппаратуру спутниковой навигации и оригинальную подсистему оптической коррекции с датчиками разных диапазонов спектра, микропроцессорными и др. элементами. В составе САУ предусмотрено запоминающее устройство, сохраняющее рестартовые массивы для восстановления работоспособности УВУ после импульса ионизирующего или электромагнитного излучения. Для нейтрализации параметрических отказов предусмотрен источник вторичного (постоянного и импульсного) питания, управляемый от УВУ схемами на полевых транзисторах. Все средства нейтрализации катастрофических отказов имеют внутреннее резервирование с контролем их функционирования и переключением на правильно работающий канал. Технический результат изобретения состоит в повышении надежности и точности работы САУ длительное время в условиях воздействия внешних дестабилизирующих факторов и расширении диапазона применения САУ. 27 з.п. ф-лы, 30 ил.

Реферат

Настоящее изобретение относится к системам автоматического управления широким классом подвижных объектов, а именно движением объектов как водного, так и наземного транспорта, а также системам управления авиационными объектами, изделиями ракетно-космической техники (РКТ) и робототехническими комплексами (РТК), к которым предъявляются повышенные требования по точности и надежности работы в экстремальных условиях и полях ионизирующего излучения. Экстремальность условий определяют широкий диапазон изменения температуры окружающей среды (от -60 до +125 градусов по Цельсию, импульсные удары и широкополосная вибрация). Ионизирующие стационарные поля обусловлены космическим излучением, фоном ядерных энергетических установок (ЯЭУ) и загрязненной местности, а импульсные вызываются вспышками на Солнце, авариями ЯЭУ и направленным противодействием.

Известна система автоматического управления судном (см. патент RU 2248914 (В63Н 25/04) от 01.03.2004), содержащая датчик и задатчик курса, датчик угловой скорости, датчик кормовых рулей, выходы которых подключены к входам первого сумматора-усилителя, выход которого соединен с входом рулевого привода кормовых рулей, датчик угла дрейфа и датчик носовых рулей, выход которого подключен к первому входу второго сумматора-усилителя. Кроме того, в состав системы введены датчик и задатчик бокового смещения судна, задатчик допустимого угла дрейфа и блок логики, содержащий алгебраический сумматор, сумматор модулей двух сигналов, диод и электромагнитное реле с двумя нормально-разомкнутой и нормально-замкнутой контактными группами. Недостатками данного технического решения являются:

1. Нестабильность характеристик. В связи с применением аналоговых узлов, параметры которых существенно зависят от условий эксплуатации (в первую очередь от температуры окружающей среды),будет наблюдаться дрейф параметров системы в целом.

2. Недостаточная отказоустойчивость. В системе не предусмотрено каких-либо средств нейтрализации отказов отдельных узлов, поэтому выход из строя любого узла приведет к отказу системы в целом.

3. Ограниченные функциональные возможности. Внедрение дополнительных управляющих задач или расширение состава входной информации требует полной переработки аппаратуры системы управления.

4. Фиксированный алгоритм управления. Как в случае расширения состава задач, при изменении алгоритма управления требуется существенная переработка аппаратуры.

Задачи расширения функциональных возможностей, применения различных алгоритмов управления и повышения стабильности, благодаря наличию цифрового вычислителя, частично решаются в изобретении - аппаратура автоматического управления движением судна (см. патент RU №2221728 (В632Н 25/04) от 13.05.2002), содержащей, кроме вычислителя, задатчик путевого угла, датчик угла перекладки руля, рулевой привод, опорную и вспомогательную антенну, аппаратуру спутниковой навигации (АСН), сумматор, два интегратора и дифференциатор. Однако недостаток - низкая отказоустойчивость - в данной аппаратуре по-прежнему присутствует, так как любой отказ вычислительного устройства или других компонентов системы влечет за собой отказ всей системы.

В то же время катастрофический отказ может быть нейтрализован за счет использования заранее введенных в состав системы резервных компонентов, а температурный и ионизационный дрейф параметров отдельных узлов может быть нейтрализован перестройкой режимов работы электрических схем изменением быстродействия блоков цифровой обработки или учетом изменения характеристик, например, номиналов стабильных токов и напряжений аналоговых узлов их измерениям в процессе работы и последующим учетом отклонений от номиналов при обработке данных в вычислительных устройствах. Наиболее полно задача нейтрализации одиночных отказов в вычислительном устройстве, являющимся центральным звеном системы решена в СИСТЕМЕ УПРАВЛЕНИЯ СУДНОМ (см. патент RU №242944) данное решение может быть принято за прототип.

Для нейтрализации последствий одиночных отказов вычислительного устройства и сохранения работоспособности системы управления в целом в состав системы введены три управляющих вычислительных устройства (УВУ) с общим устройством синхронизации, обеспечивающим синхронную и синфазную работу вычислителей, выходные сигналы которых, прежде чем поступить на исполнительные органы объекта, проходят через узел мажоритации.

Данное решение обеспечивает нейтрализацию первого одиночного отказа в любом из вычислителей. Однако после возникновения первой неисправности в любом из вычислительных устройств надежность дальнейшей работы системы резко снижается, так как возникновение второго отказа в любом из двух оставшихся исправными вычислителей приводит к отказу системы в целом, а интенсивность отказов вычислителей, приводящих к потере управления при таком варианте резервирования в два раза больше, чем при работе с одним оставшимся исправным вычислителем.

Целесообразно после возникновения первого отказа перейти от структуры с мажоритацией к структуре, в которой к выходу подключен один из вычислителей, что требует введения дополнительных средств контроля работы вычислителей и переключения их выходных сигналов УВУ.

Кроме того, наличие общего устройства синхронизации, отказ в котором приводит к неработоспособности системы, также не способствует обеспечению высокой надежности системы. Устройство синхронизации реализовано с жесткой тактовой сеткой, а при переключении каналов изменяется длина цепей прохождения информации, поэтому при жесткой сетке синхроимпульсов данные могут исказиться. Необходимо менять частоту синхронизации при перестройке структуры и изменении задержек в цепях прохождения информации, в том числе при изменениях, вызванных изменением температуры окружающей среды и действием ионизирующих полей, с учетом фактического быстродействия цепей передачи информации и работы цифровых элементов и особенно широко применяемых в последнее время микромощных КМОП БИС.

В большинстве вычислительных устройств, работающих длительное время в неблагоприятных внешних условиях, а именно в расширенном диапазоне температур, потоках ионизирующего излучения, кроме того, происходит дрейф параметров элементов, приводящий в цифровых устройствах, как правило, к изменению быстродействия, а в аналоговых узлах - к изменению стабильности и точности их работы. В то же время, подстраивая частоту обработки информации в цифровых узлах под фактическое быстродействие БИС и фактические времена передачи информации, а также, учитывая дрейф параметров в аналоговых узлах (например, в аналого-цифровых преобразователях), можно сохранить работоспособность и точностные характеристики системы управления. Кроме того, при создании радиационно-стойких БИС для таких систем создатели БИС технологическими мерами (например, перелегированием) производят сдвиг параметров этих БИС в сторону, противоположную их изменению при наборе дозы от ионизирующего излучения. Поэтому при начальном наборе дозы быстродействие БИС может возрастать и представляется целесообразным использовать повышение быстродействия для увеличения производительности УВУ и эффективности системы в целом за счет расширения состава задач и точности вычислений.

Решение этих задач требует существенной переработки известных решений.

С целью повышения эффективности, надежности и точности работы системы управления и расширения состава объектов для ее применения предлагается СИСТЕМА УПРАВЛЕНИЯ КОСМИЧЕСКОГО АППАРАТА. Далее по тексту «СИСТЕМА УПРАВЛЕНИЯ» или просто «СИСТЕМА».

СИСТЕМА содержит различные датчики: датчики угловой скорости (ДУС), датчики ускорения (акселерометры (АК)) и т.д., АСН, блок сбора информации (БСИ), три управляющих вычислительных устройства (УВУ) и исполнительные органы (ИО) объекта управления. В систему введены бесплатформенная инерциальная навигационная подсистема (БИНПС), подсистема оптической коррекции (ПОК) и подсистема электропитания (ПЭП).

Кроме того, в состав СИСТЕМЫ введен переключатель каналов (ПК) УВУ с блоком контроля (БК) переключателя каналов, датчик внешнего воздействия (ДВВ), формирователь сигнала блокировки и энергонезависимое запоминающее устройство с санкционированным доступом (ЗУСД).

БСИ содержит последовательно соединенные регистры, входы которых являются входами блока, схемы развязки и схему связи, выход которой является выходом блока, подключенным к УВУ. Кроме того, в состав блока входит преобразователь «аналог-код», выходная токовая шина которого проходит через внешние датчики резисторного типа, в том числе датчики обратной связи, входящие в ИО, и возвращается в блок.

Преобразователь «аналог-код» содержит источник стабильного тока, вход и выход которого являются токовым входом и выходом токовой шины БСИ, обтекающей последовательно внешние датчики резисторного типа. Преобразователь включает также блок преобразования напряжения в частоту, подключенный входом к выходу преобразовательного мультиплексора, входы которого являются входами преобразователя и БСИ, подключенными к выходам внешних датчиков резисторного типа, а два дополнительных входа этого мультиплексора подключены к измерительным выходам шунта, включенного в разрыв токовой шины на выходе источника стабильного тока. Выход преобразователя подключен к входу схемы связи, установочные выходы которой подключены к управляющим входам преобразовательного мультиплексора. Введение замера вытекающего тока с помощью шунта и преобразователя «аналог-код» позволяет учесть при обработке в УВУ ошибки показаний резисторных датчиков, вызванные отклонениями тока обтекания от номинала. Эти отклонения, в свою очередь, вызываются изменением температуры окружающей среды и дозовыми эффектами в полупроводниковых структурах элементов источника стабильного тока. Учет отклонений позволяет обеспечить работоспособность преобразователя и БСИ в экстремальных условиях и полях радиоактивного излучения.

В состав БИНПС входит блок акселерометров (БАК), содержащий три акселерометра, оси чувствительности которых совпадают с исходящими из одной вершины гранями условного куба, диагональ которого, исходящая из той же вершины совпадает с основной конструктивной осью аппарата. Выходы БАК подключены к входам вычислительного устройства (ВУ) блока акселерометров (ВУАК).

Каждый акселерометр БАК содержит в качестве чувствительного элемента кварцевый задающий генератор (КЗГ), рабочий скол кварца которого является измерительной осью акселерометра. Выход КЗГ подключен к входу акселерометрического счетчика, выход которого является выходом акселерометра.

ВУАК содержит микропроцессор, вход-выход которого является входом-выходом ВУ, БАК и БИНПС, подключенным к БСИ. Выход микропроцессора подключен к входу первого блока микропрограммного управления (БМУ), входу первого синхронизатора и входу буферного регистра, выход которого подключен к входам N включенных последовательно и соединенных шинами переноса умножителей, подключенных выходами к входам первого сумматора. Выход сумматора подключен к входу первого блока связи, вход-выход которого объединен с входом-выходом микропроцессора.

Кроме того, в состав БИНПС входит блок датчиков угловой скорости (БДУС), подключенный выходами к ВУ датчиков угловой скорости (ВУДУС). Входом - выходом ВУ АК и ВУ ДУС подключены к БСИ.

БДУС содержит четыре сдвоенных датчика угловой скорости, оси чувствительности трех из которых распложены по трем смежным граням, исходящим из одной вершины условного куба, а ось четвертого совпадает с диагональю этого куба, исходящей из той же вершины. Каждый ДУС содержит расположенные на одной оси чувствительный элемент грубого отсчета (ЧЭГО), обеспечивающий замер больших угловых скоростей перемещения объекта управления и чувствительный элемент точного отсчета (ЧЭТО), обеспечивающий измерение малых угловых скоростей.

ВУДУС содержит первый и второй матричные нейровычислители, входы которых являются входами ВУ, подключенными к выходам ДУС. Нейровычислители подключены через внутреннюю магистраль к матричному запоминающему устройству и матричному блоку связи, вход-выход которого является входом-выходом ВУ и БИНПС, подключенным к БСИ. Выходы блока связи подключены к установочным входам второго блока микропрограммного управления и второго синхронизатора, выходы которых подключены к управляющим и синхронизирующим входам остальных компонентов ВУ. К внутренней магистрали подключен входами блок умножения, подключенный выходом к входу второго сумматора, выход которого подключен к входу матричного запоминающего устройства.

Каждый ЧЭ ДУС содержит генератор опорной частоты (ГОЧ), установочный вход которого является одноименным входом ЧЭ, а выход является частотным выходом ЧЭ и подключен к вычитающему входу дифференциального счетчика и входу передатчика оптического. Выход этого передатчика подключен к входу волокна оптического, намотанного в виде катушки, ось которой является измерительной осью ДУС. Выход волокна оптического подключен к входу приемника оптического, выход которого подключен к суммирующему входу дифференциального счетчика. Выход счетчика является выходом ЧЭ, подключенным к входу ВУАК, установочный выход которого подключен к установочным входам всех ГОЧ данного ДУС. Выход ВУАК является выходом блока акселерометров и выходом БИНПС.

Подсистема электропитания содержит первый и второй первичные источники энергии, подключенные выходами к входам первого коммутатора и первой группе входов блока контроля и управления (БКУ). Выходы этого коммутатора подключены к входам первого и второго аккумуляторов. Выходы аккумуляторов подключены к входам второго коммутатора и второй группе входов БКУ, вход которого является установочным входом подсистемы, подключенным к выходу переключателя каналов, а выходы БКУ подключены к управляющим входам коммутаторов. Установочный вход подсистемы является также установочным входом входящего в подсистему и подключенного к выходу второго коммутатора источника вторичного электропитания (ИВЭП), содержащего модуль постоянного питания (МПП) и модуль импульсного питания (МИП), три управляющих входа которого подключены к одноименным выходам входящего в состав источника формирователя синхроимпульсов (ФСИ), синхровыходы которого и выходы постоянного и импульсного питания подключены к соответствующим входам БКУ и остальных подсистем и компонентов системы.

Переключатель каналов содержит три полевых транзистора, истоки и стоки которых являются соответственно входами и выходами переключателя, а управляющие входы переключателя соединены с затворами этих транзисторов.

БК переключателя каналов содержит первый, второй и третий регистры, входы которых являются входами БК, подключенными, соответственно, к выходам первого, второго и третьего УВУ. Выход первого регистра подключен к первым входам первой и третьей схем совпадения, выход второго регистра подключен ко второму входу первой схемы совпадения и первому входу второй схемы совпадения, а выход третьего регистра подключен ко вторым входам второй и третьей схем совпадения. При этом выход каждой схемы совпадения первой, второй и третьей через свой, соответственно, первый, второй и третий буферный триггер подключен к входу логической схемы, выход которой является выходом БК, подключенным к управляющему входу ПК.

МИП содержит три ветви, объединенные с каждой из сторон, одна из которых является силовым входом модуля, вторая - выходом. В каждой из ветвей последовательно включены два полевых транзистора, а три входных управляющих сигнала разведены таким образом, что каждый из них подключен к затворам двух транзисторов, установленных в разных ветвях, образуя выборку «2 из 3».

МПП содержит три идентичных конвертора (три канала), силовой и установочный вход каждого из которых является одноименным входом модуля. Частотный выход каждого конвертора подключен к частотному входу блока управления и контроля (БУК), к контрольным входам которого подключены выходы конверторов, которые, кроме того, через блок отключения (БО) подключены к входам блока выравнивания (БВ), выход которого является выходом модуля и подключен к дополнительному контрольному входу БУК, выходы которого подключены к управляющим входам БО.

Конвертор содержит последовательно включенные фильтр, вход которого является силовым входом конвертора, трансформатор с включенным в первичную обмотку транзистором-прерывателем, выпрямительный диод во вторичной обмотке и выходной фильтр нижних частот, выход которого является выходом конвертора и подключен к входу блока преобразования напряжения в частоту, подключенного выходом к блоку развязки, выход которого является частотным выходом конвертора и подключен к входу частотно-импульсного модулятора (ЧИМ), установочный вход которого является установочным входом конвертора, а выход модулятора подключен к базе транзистора прерывателя.

ФСИ содержит первый второй и третий генераторы импульсов (ГИ), установочные входы которых являются установочным входом ФСИ, а выход каждого из генераторов подключен к входу соответствующего каждому генератору, соответственно, первому, второму и третьему блоку фазирования, фазирующий выход каждого из которых подключен к фазирующим входам двух других блоков и к фазирующим входам блока мажоритации, к синхронизирующим входам которого подключены синхронизирующие выходы блоков фазирования. Выходы блока мажоритации являются выходами трех управляющих сигналов, метки времени и синхроимпульсов ФСИ.

ГОЧ и ГИ выполнены идентично и каждый из них включает группу последовательно соединенных инверторов, подключенных выходами к входам первого мультиплексора, выход которого является выходом генератора и подключен к входу первого инвертора группы и входу первого счетчика частоты. Выходы этого счетчика подключены к первым входам первой схемы сравнения, ко вторым входам которой подключены выходы первого регистра кода частоты, а инкрементный и декрементный выходы этой схемы сравнения подключены к одноименным входам первого счетчика кода частоты, выходы которого подключены к управляющим входам первого мультиплексора. При этом установочный вход первого счетчика кода частоты и первого регистра кода частоты являются установочным входом генератора.

Блок фазирования содержит элемент И, первый вход которого является входом блока, подключенным к генератору импульсов, а выход элемента подключен к входу сдвигового регистра и входу реализованного на динамических триггерах динамического счетчика, выходы которого через дешифратор подключены к запускающему входу триггера останова, выход которого является фазирующим выходом блока и подключен ко второму входу элемента И и первому входу мажоритарного элемента, к двум другим входам которого подключены выходы триггеров привязки, стробирующий вход которых объединен с первым входом элемента И, а входы являются фазирующими входами блока. При этом выходы четных и нечетных разрядов сдвигового регистра являются соответственно запускающими и сбрасывающими входами f триггеров - формирователей, выходы которых являются синхронизирующими выходами блока.

ЧИМ содержит несколько (n) последовательно включенных инверторов, выходы которых подключены к входам второго мультиплексора. Выход мультиплексора подключен к входу первого инвертора и является выходом модулятора. Вход модулятора является входом второго счетчика частоты, подключенного выходами к первым входам второй схемы сравнения, ко вторым входам которой подключены выходы второго регистра кода частоты, а инкрементный и декрементный выходы этой схемы сравнения подключены к одноименным входам второго счетчика кода частоты. При этом установочные входы второго счетчика кода частоты и второго регистра частоты являются установочным входом модулятора.

Формирователь сигнала блокировки содержит кварцевый задающий генератор, подключенный выходом к входу интервального счетчика, выходы которого через интервальный дешифратор подключены к входу триггера запрета, выход которого подключен к входу логического элемента. Выход этого элемента является выходом формирователя, а его датчиковый вход объединен с запускающим входом интервального счетчика и является входом формирователя, подключенным к датчику внешнего воздействия. К разрешающему входу логического элемента подключен выход кодового дешифратора, к входам которого подключены выходы регистра санкционированного кода, вход которого является кодовым входом формирователя.

Запоминающее устройство с санкционированным доступом содержит первый и второй накопители, блокирующий вход которых является входом устройства, подключенным к выходу формирователя сигнала блокировки. К входам каждого из накопителей -первого и второго подключены выходами соответствующие каждому накопителю, первому и второму, соответственно, первый и второй сумматоры метки времени, входы которых являются входам метки времени запоминающего устройства. Вход-выход каждого из накопителей, первого и второго, подключен к входу-выходу, соответственно, первого и второго сумматоров массивов, которые вторыми входами-выходами подключены вместе с накопителями к двунаправленной шине, являющейся входом-выходом устройства.

Каждый из накопителей содержит энергонезависимый элемент памяти, включенный между шинами записи, параллельно которому установлен МОП транзистор со встроенным каналом, к затвору которого подключен внешний сигнал блокировки.

Датчик внешнего импульсного ионизирующего воздействия относятся к электронным устройствам, основное назначение которых заключается в обеспечении процесса взаимодействия потока ионизирующего излучения с физической средой детектора излучения, и в преобразовании актов взаимодействия в электрические сигналы, которые могут быть зарегистрированы соответствующей измерительной аппаратурой и реализован как блокинг-генератор, к базе транзистора которого подключен обратносмещенный диод.

Динамический триггер представляет собой транзисторный усилитель, к базе транзистора которого помимо резисторного делителя, задающего рабочую точку транзистора, подключена в качестве элемента памяти LC-цепь. Индуктивность L этой цепи имеет 2 обмотки - рабочую и намотанную поверх нее встречно-компенсационную, концы которой для подавления внешних помех закорочены.

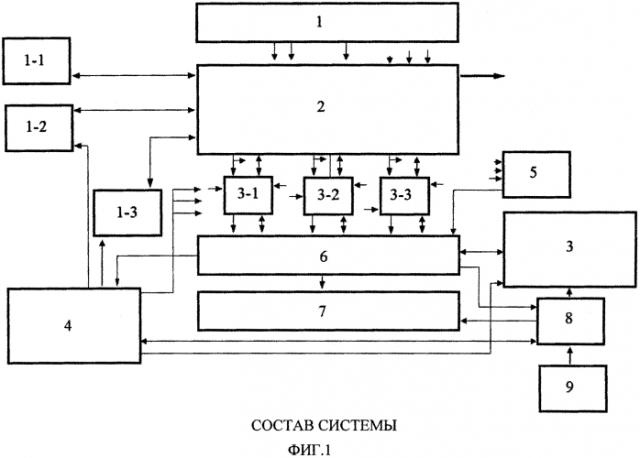

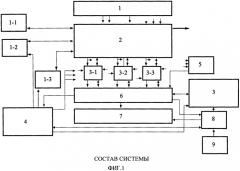

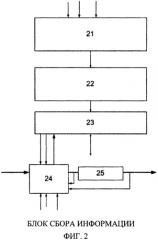

Состав СИСТЕМЫ и входящих в ее состав компонентов приведен на фигурах с 1-й по 11-ю.

На фигуре 1 приведен состав СИСТЕМЫ, где цифрой 1 обозначены датчики, цифрой 1-1 аппаратура спутниковой навигации, цифрой 1-2 - БИНПС и цифрой 1-3 -подсистема оптической коррекции, цифрой 2 обозначен БСИ, цифрами 3-1, 3-2 и 3-3 обозначены управляющие вычислительные устройства. Цифрой 3 обозначено ЗУСД, цифрой 4 обозначена ПЭП, цифрой 5 - блок контроля переключателя каналов, цифрой 6 обозначен переключатель каналов, цифрой 7 - исполнительные органы (ИО) объекта управления с датчиками обратной связи и цифрами 8 и 9 обозначены соответственно формирователь сигнала блокировки и ДВВ.

На фигуре 2 приведен состав блока сбора информации. Блок содержит приемные регистры 21 схемы развязки 22, схемы связи 23, преобразователь 24 и шунт 25.

На фигуре 2-1 приведена БИНПС, где цифрами 210-1 и 210-2 обозначены, соответственно, блок акселерометров и блок ДУС, а цифрами 211-1 и 211-2 обозначены их вычислительные устройства - ВУАК и ВУДУС, соответственно.

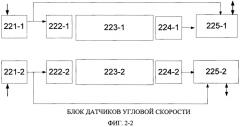

На фигуре 2-2 приведен ДУС, цифрами 221-1 и 221-2 обозначены ГОЧ грубого и точного отсчетов соответственно, цифрами 222-1 и 222-2 обозначены передатчики оптические грубого и точного отсчетов, соответственно, цифрами 223-1 и 223-2 обозначено волокно оптическое грубого и точного отсчетов, соответственно, цифрами 224-1 и 224-2 обозначены приемники оптические грубого и точного отсчетов и цифрами 225-1 и 225-2 обозначены реверсивные счетчики грубого и точного отсчетов, соответственно.

На фигурах 2-3.1 и 2-3.2 приведено расположение ДУС и ЧЭ АК, соответственно.

На фигуре 2-4 приведено ВУАК, где цифрами 240 обозначен микропроцессор, цифрами 241 первое запоминающее устройство, цифрами 242 обозначен буферный регистр, цифрами 243 обозначен первый БМУ, цифрами от 244-1 до 244-и обозначены умножители, цифрами 245 первый сумматор и цифрами 246 обозначен первый блок связи.

На фигуре 2-5 приведено ВУДУС, где цифрами 250 обозначен второй БМУ, цифрами 251-1, 251-2 и 251-3 обозначены соответственно первый, второй матричные нейровычислители и матричное запоминающее устройство, цифрами 252 обозначен второй сумматор, цифрами 253 второй блок связи и цифрами 254 обозначен второй синхронизатор.

На фигуре 3 приведено ЗУСД, где цифрами 31 и 32 обозначены первый и второй накопители, цифрами 33-1 и 33-2 обозначены первый и второй сумматоры метки времени и цифрами 34-1 и 34-2 обозначены первый и второй сумматоры массивов.

Накопитель приведен на фигуре 3-1, где цифрами 30 обозначен энергонезависимый элемент памяти.

ПЭП приведена на фигуре 4. Здесь цифрами 41-1 и 41-2 обозначены первый и второй первичные источники, цифрами 42 и 44 обозначены первый и второй коммутаторы, цифрами 43-1 и 43-2 обозначены первый и второй аккумуляторы, цифрами 45 - БКУ и цифрами 46 обозначен ИВЭП.

ИВЭП приведен на фигуре 4-1, где цифрами 411, 412 и 413 обозначены МПП, МИП и ФСИ, соответственно.

МПП приведен на фигуре 4-10. Здесь цифрами 410-1, 410-2 и 410-3 обозначены конверторы, цифрами 411 БО, цифрами 412 обозначен БВ и цифрами 414 обозначен БУК.

На фигурах 4-11 и 4-13 приведены соответственно МИП и фильтр.

Конвертор приведен на фигуре 4-12, где цифрами 412-1 и 412-2 обозначены фильтр и выходной фильтр, цифрами 413 обозначен трансформатор, цифрами 414 транзистор-прерыватель. Цифрами 415 обозначен элемент развязки, цифрами 416 - ЧИМ и цифрами 417 обозначен преобразователь напряжения в частоту.

БУК приведен на фигуре 4-14, где цифрами 40 и 41 обозначены контрольный преобразователь напряжения в частоту и контрольный мультиплексор, соответственно. Цифрами от 41-1, 41-2, 41-3 и 41-4 обозначены первый, второй, третий и четвертый частотные счетчики, соответственно. Цифрами 42-1, 42-2, 42-3 и 42-4 обозначены первый, второй, третий и четвертый сумматоры. Цифрами 43 и 44 обозначены регистр кода и регистр допуска соответственно. Цифрами 45-1, 45-2, 45-3 и 45-4 обозначены первая, вторая, третья и четвертая схемы совпадения соответственно. Цифрами 46-1, 46-2-46-3 и 46-4, обозначены первый, второй, третий и четвертый триггеры неисправности, соответственно, а цифрами 47 обозначена группа логических схем.

На фигурах 4-15 и 4-16 приведены БО и БВ, соответственно.

ЧИМ приведен на фигуре 4-17, где цифрами 4170 обозначены инверторы, цифрами 4171 второй мультиплексор, цифрами 4172 обозначен второй счетчик кода частоты, цифрами 4173 обозначен второй счетчик частоты, цифрами 4174 вторая схема сравнения и цифрами 4175 обозначен второй регистр кода частоты.

ФСИ приведен на фигуре 4-18, где цифрами 4181-1, 4181-2 и 4181-3 обозначены первый, второй и третий генераторы импульсов, соответственно. Цифрами 4182-1, 4182-2 и 4182-3 обозначены первый, второй и третий блоки фазирования, соответственно, и цифрами 4183 обозначен блок мажоритации.

На фигуре 4-20 приведен генератор импульсов, где цифрами 420 обозначены инверторы, цифрами 421 - первый мультиплексор, цифрами 422 обозначен первый счетчик частоты, цифрами 423 - первый счетчик кода частоты, цифрами 424 - первая схема сравнения и цифрами 425 обозначен первый регистр кода частоты.

Блок фазирования приведен на фигуре 4-21. Здесь цифрами 4211 обозначен элемент И, цифрами 4212 и 4213 обозначены динамический счетчик и сдвиговый регистр, соответственно. Цифрами 4214 обозначен дешифратор, цифрами 4215 и 4216 обозначены триггер останова и триггер пуска, соответственно, цифрами 4217 обозначен мажоритарный элемент, цифрами 4218 - триггеры привязки и цифрами от 4219-1 до 4219-f обозначены формирователи.

На фигуре 5 приведен блок контроля переключателя каналов, где цифрами 51-1,51-2 и 51-3 обозначены первый, второй и третий регистры, цифрами 52-1, 52-2 и 52-3 обозначены первое, второе и третье устройства сравнения и цифрами 53 обозначен логический элемент.

Переключатель каналов приведен на фигуре 6.

ПОК приведена на фигуре 7, где цифрами от 70-1 до 70-n обозначены оптические датчики, цифрами 71 обозначено ВУПОК.

ВУПОК приведено на фигуре 8, где цифрами 811 обозначен управляющий микропроцессор, цифрами 812 - обрабатывающее запоминающее устройство, цифрами от 813-1 до 813-k обозначены обрабатывающие микропроцессоры, цифрами 814 обозначен обрабатывающий БМУ и цифрами 815 обозначен обрабатывающий синхронизатор.

Формирователь сигнала блокировки приведен на фигуре 9, где цифрами 90 обозначен кварцевый задающий генератор, цифрами 91 - таймерный счетчик, цифрами 92 обозначен таймерный дешифратор, цифрами 93 - триггер запрета и цифрами 94, 95 и 96 обозначены регистр кода, дешифратор кода и логическая схема, соответственно.

На фигуре 10 приведен датчик внешнего воздействия и динамический триггер приведен на фигуре 11.

СИСТЕМА работает следующим образом:

После включения питания начинают работать генераторы импульсов ФСИ и через несколько периодов высокой частоты с выхода ФСИ в УВУ начинают поступать синхронно и синфазно метки времени на вход прерывания и синхроимпульсы на синхровходы УВУ и остальных компонентов системы, УВУ приступают к выполнению программ управления, опрашивая через блок сбора информации внешние датчики, БИНПС и корректирующие подсистемы АСН и ПОК.

Результаты вычислений выдаются через переключатель каналов на исполнительные органы объекта управления, выходная информация всех каналов УВУ поступает одновременно в блок контроля переключателя каналов, в который, кроме того, поступают сигналы неисправности, вырабатываемые встроенными в каждое УВУ аппаратурными средствами контроля, например, по mod 3. Можно обозначить сигналы от этих средств через Hi, где i - номер УВУ (1, 2 или 3). Для логики работы переключателя все УВУ расположены по кольцу: 1, 2, 3, 1. Таким образом, для УВУЗ(i) УВУ2 будет иметь индекс (i-1), а УВУ1 будет иметь индекс (i+1) и т.д. При обнаружении неисправности i-го УВУ переключатель подключает к выходу сигналы предыдущего по номеру, т.е. (i-1)-го вычислителя. В случае неисправности двух вычислителей к выходу будут подключены сигналы третьего исправного УВУ. Таким образом, после возникновения первого отказа к выходу подключены сигналы всегда одного вычислителя, что существенно снижает вероятность отказа системы после возникновения первой неисправности. В случае формирования сигналов неисправности трех вычислителей, что может быть следствием ограниченной достоверности работы встроенных средств контроля или схем сравнения, к выходу остается подключенным последний признанный исправным вычислитель, что исключает неопределенность в логике работы переключателя. Логику выработки сигналов неисправности УВУ, вырабатываемых БКУ, по которым происходит переключение каналов можно представить в виде логической формулы.

Обозначим:

Hi - неисправность i-го УВУ, нi - неисправность этого же вычислителя, сформированная внутренними средствами контроля,

Ci - неисправность этого же вычислителя, сформированная схемами сравнения.

Тогда Hi=CiVHi

Логику выработки сигнала неисправности, формируемого схемами сравнения можно записать следующим образом:

Ci=(ИiΛHi+1ΛJИi-1VИiΛИi-1ΛИi+1)V(JИiΛJИi+lΛИi-1VИiΛJИi+1ΛИi-1VJИiΛJИi-1ΛИi+1).

Система может быть реализована следующим образом:

УВУ и все ВУ реализуются на основе радиационно стойких БИС микропроцессоров серии 1825 и запоминающих устройств серии 1620, дополненных БИС на основе базовых матричных кристаллов (БМК) серии 537ХМ2, изготавливаемых в производстве АО «Ангстрем» (г. Москва. АСН используется типовая, созданная специально для космических аппаратов и изготавливаемая серийно в ФГУП «РНИИКП» (г. Москва). ПОК изготавливается на основе оптоэлектронных устройств (телескопов с ПЗС матрицами, изготавливаемых ФГУП « ЦКБ «Геофизика Космос»» (г. Москва) со вычислительным устройством, изготавливаемом в производстве ФГУП НПОА (г. Екатеринбург на основе БИС серий 1825 и 1620, дополненных специализированными БИС на основе БМК серии 537ХМ2.

ПЭП изготавливается в производстве ФГУП НПОА с использованием в качестве первичных источников энергии солнечных батарей, химических источников тока в виде водородных реакторов, ампульных батарей или перспективных, активно разрабатываемых в последние годы радио изотопных электротеплогенераторов (РИТЭГ). БИНПС может быть реализована следующим образом:

ЧЭ ДУС реализуется на основе перестраиваемого задающего генератора, выполненного в виде БИС на основе БМК сер. 537ХМ2, изготавливаемого в производстве АО «Ангстрем». В качестве передатчика оптического используется передатчик типа HFBR2522Z или его аналог.

Волокно оптическое можно использовать типа HFBR-RNS 003 и HFBR-RU 100 или их аналоги.

В качестве приемника оптического используется приемник HFBR-1522Z или его аналог.

ВУ реализуются в виде изготавливаемой в производстве НПОА многокристальной сборки специализированных БИС на основе БМК сер. 5516, 5517 и 537, изготавливаемых в производстве АО «Ангстрем».

ЧЭАК изготавливается на основе кварцевого задающего генератора, изготавливаемого в производстве НПОА и многокристальной сборки, изготавливаемой также в производстве НПОА с использованием специализированных БИС на основе БМК сер. 1556 и 1557 и БИС запоминающих устройств сер. 1620, изготавливаемых АО «Ангстрем».

Все преобразователи напряжения в частоту, входящие в состав преобразователя БСИ и компонентов ПЭП могут быть реализованы на основе микросхем типа 1108ПП1(г.Рига) или микросхемы ADFC32 фирмы Analog Devices или ее аналога.

ДВВ и динамический триггер изготавливаются в производстве НПОА из дискретных промышленных элементов (резисторы, конденсаторы, диоды и ферритовые кольца.). ЗУСД изготавливается в производстве НПОА с накопителями на основе цилиндрических тонких магнитных пленок (ЦТМП) с электроникой, выполненной в виде многокристальных микросборок с бескорпусными дискретными элементами (резисторы, конденсаторы, транзисторы и диоды.).

Таким образом, введение переключателя с блоком контроля и управления позволяет нейтрализовать, по крайней мере, две неисправности в вычислительных устройствах и сохраняет вероятность работоспособности системы при трех неисправностях УВУ. Наличие в ФСИ трех генераторов импульсов и трех взаимно фазируемых блоков фазирования обеспечивает нейтрализацию, как одной постоянной неисправности в ФСИ, так и нейтрализацию кратковременных отказов (сбоев) в формирователе, в которых реализована функция взаимного фазирования за 2-3 периода высокой частоты. После чего начинается формирование синхронных и синфазных меток реального времени и синхроимпульсов, обеспечивающих работу УВУ и системы в целом.

Введение перестройки частоты генераторов импульсов, входящих в состав ФСИ, позволяет на каждый интервал времени установить частоту синхронизации, соответствующую текущему быстродействию цифровых узлов, что позволяет не только повысить надежность работы системы путем снижения быстродействия, но и использовать возникающие запасы по быстродействию, для чего предусмотрено периодическое выполнение программ тестовых проверок УВУ, позволяющее оценить работоспособность при текущей или устанавливаемой частоте синхронизации.

Для нейтрализации параметрических уходов аналоговых узлов в конверторе и БКУ в качестве основного выбран преобразователь напряжения в частоту, обладающий тем несомненным достоинством, что зависимость точности и стабильности его работы определяется всего двумя элементами - резистором и конденсатором, выбором типов которых и предварительной их радиационной и термотренировкой можно обеспечить требуемую стабильность работы на продолжительном интервале времени. Нестабильность работы источника тока, необходимого для запитки внешних датчиков резистивного типа в предложенной системе нейтрализуется установкой в токовую цепь высокостабильного эталонного резистора (шунта), замеряя падение напряжения