Активация/деактивация адаптеров вычислительной среды

Иллюстрации

Показать всеИзобретение относится к средствам обработки ввода-вывода вычислительной среды, в частности к активации/деактивации адаптеров вычислительной среды. Технический результат заключается в обеспечении независимости процедуры активации/деактивации от конкретного аппаратного обеспечения. Активация включает назначение одного или более адресных пространств адаптеру, на основании запроса. Для каждого адресного пространства, назначенного адаптеру, назначается соответствующая запись таблицы устройств. Когда адаптер больше не нужен, он деактивируется и назначенная запись таблицы устройств становится доступной. 2 н. и 19 з.п. ф-лы, 19 ил.

Реферат

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Это изобретение в целом относится к обработке ввода-вывода вычислительной среды, и в частности - к активации/деактивации адаптеров вычислительной среды.

Сегодня вычислительные среды имеют различные конфигурации и используют различные типы устройств ввода/вывода (I/O). Для того чтобы использовать устройство ввода-вывода, оно активируется, а затем, когда его использование завершается, оно деактивируется. Способ, которым устройство ввода-вывода активируется/деактивируется, зависит от устройства.

В системе z/Architecture® и ее предшественниках, предлагаемых International Business Machines Corporation, активация и деактивация устройств ввода-вывода, как правило, выполняется на основании канального тракта, элемента управления и субканала.

Различные функции команды Channel Subsystem Call предоставляют интерфейсы, посредством которых операционные системы могут управлять различными ресурсами ввода-вывода.

Однако могут использоваться и другие типы устройств ввода-вывода, которые не включают каналов и субканалов. Например, адаптеры взаимодействия периферийных компонентов (PCI) используют парадигмы соединения и связи, которые отличаются от традиционных устройств ввода-вывода. Спецификация PCI доступна в World Wide Web по адресу www.pcisig.com/home.

Публикация США №2004/0117534 А1, опубликованная 17 июня 2004 (на имя Parry и др.) “Apparatus and Method for Dynamically Enabling and Disabling Interrupt Coalescing in Data Processing System” описывает устройство и способ для динамической активации и деактивации объединения прерываний в системе обработки данных. Настоящее изобретение согласованно включает отслеживание нагрузки ввода-вывода на IOP адаптера ввода-вывода. Встроенное программное обеспечение адаптера ввода-вывода может иметь глобальную переменную, которая хранит счетчики для регистров функции PCI. Каждый счетчик отслеживает число ожидающих выполнения вводов-выводов соответствующего регистра функции PCI. Счетчик увеличивается каждый раз, когда принимается новый ввод-вывод, и уменьшается после отправки сообщения о завершении назад операционной системе. Прерывание по таймеру генерируется периодически так, что может периодически выполняться ISR. В ISR анализируется максимальное хранящееся значение каждого счетчика, видимое после последнего прерывания по таймеру. Когда максимальное хранящееся значение больше предопределенного порогового значения, активируется объединение прерываний.

Публикация США №2010/0005234 А1, опубликованная 7 января 2010 (на имя Ganga и др.). Enabling Functional Dependency in a Multi-Function Device” описывает в одном варианте осуществления, настоящее изобретение включает способ для считывания конфигурационной информации из многофункционального устройства (MFD), создания дерева зависимостей функциональной зависимости функций, выполняемых MFD, на основании конфигурационной информации, которое указывает, что MFD способно выполнять по меньшей мере одну функцию, зависящую от другой функции, и загрузки программного обеспечения, связанного с функциями, в порядке, основанном, по меньшей мере частично, на указанной функциональной зависимости. Описаны и сформулированы и другие варианты осуществления.

Публикация США №2004/0199700 А1, опубликованная 7 октября 2004 (на имя Shawn Adam Clayton), “Virtual Peripheral Component Interconnect Multiple-Function Device”, описывает устройство взаимосвязи периферийных компонентов (PCI), содержащее интерфейс шины, подключенный к шине взаимосвязи компонентов, множество наборов регистров конфигурационного пространства и виртуальную многофункциональную логику. Каждый набор регистров конфигурационного пространства связан с функцией. Виртуальная многофункциональная логика подключена к интерфейсу шины и набору регистров конфигурационного пространства. Виртуальная многофункциональная логика обеспечивает доступ к множеству регистров конфигурационного пространства для множества функций. Виртуальная многофункциональная логика также дает возможность множеству функций разделять интерфейс шины и другую внутреннюю логику.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

В соответствии с изобретением предоставляется функциональная способность для активации/деактивации адаптеров, таких как адаптеры PCI. При этом эта функциональная способность, как она представляется операционной системе, является общей для всех адаптеров, и поэтому считается независимой от устройств.

Недостатки имеющегося уровня техники преодолеваются и преимущества обеспечиваются в способе активации адаптеров в вычислительной среде, характеризующемся тем, что в ответ на выполнение команды Call Logical Processor (CLP), выданной операционной системой, для активации адаптера, выбранного операционной системой, содержащей дескриптор функции, идентифицирующий адаптер и имеющий указатель неактивированного адаптера, команда CLP запрашивает число адресных пространств прямого доступа к памяти (DMA),которые должны быть назначены адаптеру, причем указанное выполнение активирует одно или более адресных пространств DMA и включает: а) активацию адаптера, включающую активацию регистрации для трансляции адреса и прерываний для поддержки прямых доступов к памяти и инициируемых сообщениями прерываний для адаптера, определение того, что запрошенное число адресных пространств DMA являются доступным, выполняемое путем проверки наличия записей таблицы устройств для запрошенного числа адресных пространств DMA, и назначение адаптеру числа записей таблицы устройств, соответствующего запрошенному числу адресных пространств DMA; и б) возврат дескриптора функции, имеющего указатель активированного адаптера.

Объектом изобретения является также компьютерная система для активации адаптеров в вычислительной среде, содержащая память, процессор, связанный с памятью, и элемент запросов, реагирующий на выполнение команды Call Logical Processor (CLP), выданной операционной системой, для активации адаптера, выбранного операционной системой, и содержащей дескриптор функции, идентифицирующий адаптер и имеющий указатель неактивированного адаптера, причем команда CLP запрашивает число адресных пространств прямого доступа к памяти (DMA),которые должны быть назначены адаптеру, а указанное выполнение активирует одно или более адресных пространств DMA и включает: а) активацию адаптера, включающую активацию регистрации для трансляции адреса и прерываний для поддержки прямых доступов к памяти и инициируемых сообщениями прерываний для адаптера, определение того, что запрошенное число адресных пространств DMA являются доступным, выполняемое путем проверки наличия записей таблицы устройств для запрошенного числа адресных пространств DMA, и назначение адаптеру числа записей таблицы устройств, соответствующего запрошенному числу адресных пространств DMA; и б) возврат дескриптора функции, имеющего указатель активированного адаптера.

Технический результат, достигаемый при осуществлении изобретения, заключается в обеспечении независимости процедуры активации, деактивации адаптеров от конкретного аппаратного обеспечения. Дополнительные признаки и преимущества реализуются посредством методик согласно настоящему изобретению. Другие варианты осуществления и признаки изобретения подробно описаны в настоящем изобретении и считаются частью заявленного изобретения.

Предпочтительный вариант осуществления настоящего изобретения теперь будет описан, исключительно в качестве примера, со ссылкой на соответствующие графические материалы, на которых:

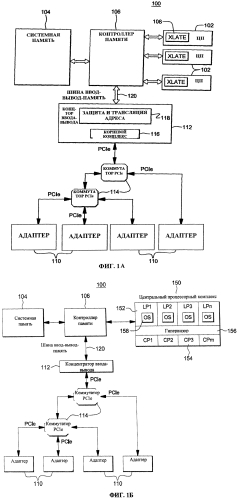

ФИГ.1А иллюстрирует один вариант осуществления вычислительной среды для включения и использования одной или нескольких особенностей настоящего изобретения;

ФИГ.1Б иллюстрирует другой вариант осуществления вычислительной среды, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

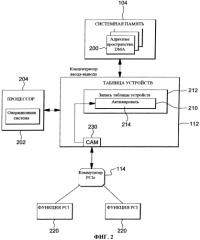

ФИГ.2 иллюстрирует один вариант осуществления дополнительных подробностей о системной памяти и концентраторе ввода-вывода, представленных на ФИГ.1А и 1Б, в соответствии с одной особенностью настоящего изобретения;

ФИГ.3А представляет собой один пример записи таблицы функций, используемой в соответствии с одной особенностью настоящего изобретения;

ФИГ.3Б представляет собой один вариант осуществления дескриптора функции, используемого в соответствии с одной особенностью настоящего изобретения;

ФИГ.4А один из вариантов осуществления команды Call Logical Processor, используемой согласно одной из особенностей настоящего изобретения;

ФИГ.4Б один из вариантов осуществления блока запроса, используемого командой Call Logical Processor, показанной на ФИГ.4А, в соответствии с одной особенностью настоящего изобретения;

ФИГ.4В иллюстрирует один вариант осуществления блока ответа, предоставляемого командой Call Logical Processor, представленной на ФИГ.4А, в соответствии с одной особенностью настоящего изобретения;

ФИГ.5 иллюстрирует один вариант осуществления логической схемы для активации функции PCI, в соответствии с одной особенностью настоящего изобретения;

ФИГ.6 иллюстрирует один вариант осуществления логической схемы для деактивации функции PCI, в соответствии с одной особенностью настоящего изобретения;

ФИГ.7 иллюстрирует один вариант осуществления компьютерного программного продукта, в котором содержится одна или несколько особенностей настоящего изобретения;

ФИГ.8 иллюстрирует один вариант осуществления хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.9 иллюстрирует дополнительный пример компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.10 иллюстрирует другой пример компьютерной системы, содержащей компьютерную сеть, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.11 иллюстрирует один вариант осуществления различных элементов компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.12А иллюстрирует один вариант осуществления исполнительного устройства компьютерной системы по ФИГ.11, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.12Б иллюстрирует один вариант осуществления блока перехода компьютерной системы, представленной на ФИГ.11, в которой содержится и используется одна или несколько особенностей настоящего изобретения;

ФИГ.12В иллюстрирует один вариант осуществления блока загрузки/сохранения компьютерной системы, представленной на ФИГ.11, в которой содержится и используется одна или несколько особенностей настоящего изобретения; и

ФИГ.13 иллюстрирует один вариант осуществления эмулированной хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ

В соответствии с одной особенностью настоящего изобретения предоставляется функциональная способность для активации/деактивации адаптеров вычислительной среды. С точки зрения операционной системы функциональная способность является независимой от устройств. То есть операционная система выполняет одну и ту же логику независимо от типа адаптера.

Как используется в данном документе, встроенное программное обеспечение включает, например, микрокод, миликод и макрокод процессора. Оно содержит, например, команды аппаратного уровня и/или структуры данных, используемые при реализации высокоуровневого машинного кода. В одном варианте осуществления изобретения оно содержит, например, собственный код, который, как правило, поставляют как микрокод, который содержит выверенное программное обеспечение, или микрокод, характерный для базового аппаратного обеспечения, и управляет доступом операционной системы к аппаратному обеспечению системы.

Также термин “адаптер” включает любой типа адаптера (например, адаптер запоминающего устройства, адаптер обработки, адаптер PCI, другой тип адаптеров ввода-вывода, и т.п.). Кроме того, в примерах, представленных в данном документе, адаптер используется взаимозаменяемо с функцией адаптера (например, функцией PCI). В одном из вариантов осуществления адаптер содержит одну функцию. Тем не менее, в других вариантах осуществления адаптер может содержать множество функций адаптера. В зависимости от того, содержит ли адаптер одну функцию или множество функций, применима одна или несколько особенностей настоящего изобретения. В одном варианте осуществления, если адаптер содержит множество функций адаптера, каждая функция может быть активирована/деактивирована в соответствии с особенностью настоящего изобретения.

Далее будет описан один из вариантов осуществления вычислительной среды, в которой содержится и используется одна или несколько особенностей настоящего изобретения согласно ФИГ.1А. В одном примере вычислительная среда 100 представляет собой сервер System z®, поставляемый International Business Machines Corporation. System z® основан на z/Architecture®, поставляемой International Business Machines Corporation. Подробности об z/Architecture® описаны в публикации IBM® под названием "z/Architecture Principles of Operation", публикация IBM №SA22-7832-07, февраль 2009. IBM®, System z® и z/Architecture® являются зарегистрированными товарными знаками International Business Machines Corporation, Армонк, Нью-Йорк. Другие названия, используемые в заявке, могут являться зарегистрированными товарными знаками, товарными знаками или названиями продуктов International Business Machines Corporation или других компаний.

В одном из примеров вычислительная среда 100 содержит один или несколько центральных процессоров (ЦП) 102, связанных с системной памятью 104 (иначе называемой основной памятью) посредством контроллера 106 памяти. Для доступа к системной памяти 104 центральный процессор 102 выдает запрос чтения или записи, в котором содержится адрес, используемый для доступа к системной памяти. Поскольку адрес, содержащийся в запросе, обычно не может непосредственно использоваться для доступа к системной памяти, он транслируется в адрес, который может непосредственно использоваться для доступа к системной памяти. Адрес транслируется посредством механизма 108 трансляции (XLATE). Например, адрес транслируется из виртуального адреса в действительный или абсолютный адрес с использованием, например, динамической трансляции адресов (DAT).

Запрос, содержащий транслированный адрес, принимается контроллером 106 памяти. В одном из примеров контроллер 106 памяти состоит из аппаратного обеспечения и используется для арбитража при доступе к системной памяти и для обеспечения непротиворечивости памяти. Этот арбитраж осуществляется применительно к запросам, принимаемым от ЦП 102, а также запросам, принимаемым от одного или нескольких адаптеров 110. Подобно центральным процессорам адаптеры выдают в системную память 104 запросы на получение доступа к системной памяти.

В одном примере адаптер 110 является адаптером взаимодействия периферийных компонентов (PCI) или PCI express (PCIe), содержащим одну или более функций. Функция PCI выдает запрос, который маршрутизируется в концентратор 112 ввода-вывода (например, концентратор PCI) посредством одного или нескольких коммутаторов (например, коммутаторов PCIe) 114. В одном примере, концентратор ввода-вывода состоит из аппаратного обеспечения, включая один или более конечных автоматов, и соединен с контроллером 106 памяти посредством шины 120 ввод-ввывод-память.

Концентратор ввода-вывода содержит, например, корневой комплекс 116, который принимает запрос от коммутатора. Запрос содержит адрес ввода-вывода, который подается на блок 118 защиты и трансляции адреса, который осуществляет доступ к информации, используемой для запроса. В качестве примеров, запрос может содержать адрес ввода-вывода, используемый для выполнения операции прямого доступа к памяти (DMA) или для запроса инициируемого сообщениями прерывания (MSI). Блок 118 защиты и трансляции адреса осуществляет доступ к информации, используемой для запроса DMA или MSI. В качестве конкретного примера, для операции DMA, информация может быть получена, чтобы транслировать адрес. Транслированный адрес затем направляется на контроллер памяти, чтобы осуществлять доступ к системной памяти.

В еще одном варианте осуществления вычислительной среды, в дополнение к одному или более ЦП 102 или вместо них, с контроллером памяти 106 соединяется процессорный комплекс, как показано на ФИГ.1Б. В этом примере центральный процессорный комплекс 150 содержит, например, один или более разделов или областей 152 (например, логические разделы LP1-LPn), один или более центральных процессоров (например, CP1-CPm) 154 и гипервизор 156 (например, менеджер логических разделов), каждый из которых описывается ниже.

Каждый логический раздел 152 способен функционировать как отдельная система. То есть, каждый логический раздел, если необходимо, может быть независимо перезагружен, изначально загружен операционной системой или гипервизором (таким как z/VM®, поставляемым International Business Machines Corporation, Армонк, Нью-Йорк) и работать с различными программами. Операционная система, гипервизор или прикладная программа, работающие в логическом разделе, как кажется, имеет доступ к системе целиком и полностью, но доступна лишь ее часть. Сочетание аппаратного обеспечения и лицензированного внутреннего кода (также называемого микрокодом или милликодом) удерживает программу в логическом разделе от пересечения с программой в другом логическом разделе. Это позволяет нескольким разным логическим разделам работать на одном или множестве физических процессоров в режиме квантования времени. В этом конкретном примере каждый логический раздел обладает резидентной операционной системой 158, которая может отличаться для одного или более логических разделов. В одном варианте осуществления операционная система 158 является операционной системой z/OS® или zLinux, поставляемой International Business Machines Corporation, Армонк, Нью-Йорк. z/OS® и z/VM® являются зарегистрированными товарными знаками International Business Machines Corporation, Армонк, Нью-Йорк.

Центральные процессоры 154 представляют собой физические процессорные ресурсы, которые выделены логическим разделам. Например, логический раздел 152 содержит один или более логических процессоров, каждый из которых представляет весь физический процессорный ресурс 154, выделенный разделу, или его долю. Лежащий в основе процессорный ресурс может или назначаться только этому разделу, или разделяться с другим разделом.

Управление логическими разделами 152 осуществляется гипервизором 156, реализуемым встроенным программным обеспечением, работающим на процессорах 154. Логические разделы 152 и гипервизор 156 каждый содержат одну или более программ, постоянно находящихся в соответствующих частях центрального запоминающего устройства, связанного с центральными процессорами. Одним примером гипервизора 156 является Менеджер процессорных ресурсов/систем (PR/SM), поставляемый Business Machines Corporation, Армонк, Нью-Йорк.

Хотя в этом примере описан центральный процессорный комплекс, имеющий логические разделы, одна или более особенностей настоящего изобретения могут включаться в и использоваться другими устройствами обработки, включая одно- или многопроцессорные устройства обработки, которые не разделяются на разделы, среди прочих. Центральный процессорный комплекс, описанный в данном документе, является лишь одним примером.

Дальнейшие подробности о системной памяти и концентраторе ввода-вывода описываются со ссылкой на ФИГ.2. В этом примере контроллер памяти не показан, но может использоваться. Концентратор ввода-вывода может быть соединен с системной памятью 104 и/или процессором 204 непосредственно или посредством контроллера памяти.

Обращаясь к ФИГ.2, в одном примере системная память 104 содержит одно или более адресных пространств 200. Адресное пространство - это конкретная часть системной памяти, которая была назначена для конкретного компонента вычислительной среды, такой как конкретный адаптер. В одном примере адресное пространство доступно путем прямого доступа к памяти (DMA), инициируемого адаптером, и поэтому адресное пространство в примерах данного документа называется адресным пространством DMA. Однако в других примерах для доступа к адресному пространству прямой доступ к памяти не используется.

В одном примере имеется операционная система 202, выполняющаяся в процессоре 204 (например, ЦП 102 или ЦП 154, выделенных LP 152), которая назначает адресное пространство DMA конкретному адаптеру. Это назначение выполняется посредством процесса регистрации, который вызывает инициализацию (например, посредством надежного программного обеспечения) записи 210 таблицы устройств для этого адаптера. Имеется одна запись таблицы устройств на каждое назначенное адресное пространство, и эта запись таблицы устройств связана с единственным адаптером. Эта запись таблицы устройств находится в таблице 212 устройств, расположенной в концентраторе 112 ввода-вывода. Например, таблица 212 устройств находится в блоке защиты и трансляции адреса концентратора ввода-вывода.

В одном примере запись 210 таблицы устройств содержит информацию, используемую для предоставления различных сервисов для адаптера. Например, запись таблицы устройств содержит указатель 214 активации, который указывает, активирована ли запись таблицы устройств для конкретного адаптера. Запись таблицы устройств может содержать больше или меньше информации, или другую информацию, для операций активации/деактивации, а также для других предоставляемых сервисов, таких как трансляция адреса, управление прерываниями и т.п.

В одном варианте осуществления запись таблицы устройств, которая должна использоваться конкретным адаптером, который подает запрос, определяется с помощью идентификатора реквестора (RID) (и/или части адреса), находящегося в запросе, поданном функцией PCI (220), связанной с адаптером. Реквестор (например, 16-битное значение, определяющее, например, номер шины, номер устройства и номер функции) включается в запрос, также как и адрес ввода-вывода, который необходимо использовать. Запрос, включая RID и адрес ввода-вывода, подается, например, на ассоциативное запоминающее устройство (САМ) 230 через, например, коммутатор 114, который используется, чтобы предоставлять индексное значение. Например, в САМ содержится множество записей, каждая из которых соответствует индексу в таблице устройств. Каждая запись в САМ содержит значение RID. Если, например, полученный RID соответствует значению, содержащемуся в записи в САМ, для определения положения записи таблицы устройств используется соответствующий индекс таблицы устройств. То есть, выход САМ используется для индексации в таблице 212 устройств, чтобы определять положение записи 210 таблицы устройств. Если соответствие отсутствует, принятый пакет отбрасывается (в других вариантах осуществления не требуется САМ или другое средство поиска, и RID используется в качестве индекса).

В дополнение к записи таблицы устройств, с адаптером также связывается другая структура данных, которая содержит информацию об адаптере. В конкретных примерах, описанных в данном документе, адаптер представляет собой функцию PCI, поэтому структура данных называется записью таблицы функций (FTE). Хотя примеры, описанные в данном документе, относятся к функциям PCI, в других вариантах осуществления могут активироваться/деактивироваться другие адаптерные функции или адаптеры, в соответствии с одной особенностью настоящего изобретения.

Как показано на ФИГ.3А, в одном примере запись 300 таблицы функций является записью в таблице 302 функций, хранящейся, например, в защищенной памяти. Каждая запись 300 таблицы функций содержит информацию, которая должна использоваться при обработке, связанной с ее адаптером. В одном примере запись 300 таблицы функций содержит номер 308 экземпляра, указывающий конкретный экземпляр функции адаптера, связанной с записью таблицы функций; один или более индексов 310 записей таблицы устройств, каждый из которых используется в качестве индекса в таблице устройств, чтобы определять положение его соответствующей записи таблицы устройств (функция PCI может иметь множество адресных пространств, приписанных к ней, поэтому и множество записей DTE); указатель 312 занятости, который указывает, занята ли функция PCI; указатель 314 состояния постоянной ошибки, который указывает, находится ли функция в состоянии постоянной ошибки; указатель 316 инициированного восстановления, который указывает, было ли инициировано восстановление для функции; указатель 318 разрешения, который указывает, имеет ли операционная система, пытающаяся активировать функцию PCI, полномочия на это; и указатель 320 активации, указывающий, активирована ли функция (например, 1=активирована, 0=деактивирована).

В одном примере указатель занятости, указатель состояния постоянной ошибки и указатель инициированного восстановления устанавливаются на основании текущего контроля, выполняемого встроенным программным обеспечением. Кроме того, указатель разрешения устанавливается, например, на основании политики. В других вариантах осуществления запись таблицы функций может содержать больше или меньше информации, или другую информацию.

В одном варианте осуществления для определения положения записи таблицы функций в таблице функций, которая содержит одну или более записей, используется идентификатор функции, такой как дескриптор функции. Например, один или несколько бит дескриптора функции используются в качестве индекса таблицы функции для размещения конкретной записи таблицы функции.

Со ссылкой на ФИГ.3Б описываются дополнительные подробности о дескрипторе функции. В одном примере дескриптор 350 функции включает указатель 352 активации, который указывает, активирован ли дескриптор функции PCI; номер 354 функции PCI, который идентифицирует функцию (это статический идентификатор) и, в одном варианте осуществления, - является индексом в таблице функций; и номер 356 экземпляра, который указывает конкретный экземпляр этого дескриптора функции. Например, каждый раз, когда функция активируется, номер экземпляра увеличивается, чтобы предоставлять новый номер экземпляра.

Чтобы использовать функцию PCI, ее необходимо активировать. Например, операционная система, которая хотела бы использовать функцию PCI, выполняет запрос, чтобы определить одну или более функций, которые она может использовать (на основании конфигурации ввода-вывода), и выбирает одну из этих функций для активации. В одном примере функция активируется с использованием команды установки функции PCI команды Call Logical Processor. Один вариант осуществления этой команды представлен на ФИГ.4А. Как показано, в одном примере команда 400 Call Logical Processor включает код 402 операции, указывающий, что это команда Call Logical Processor; и указание 404 для команды. В одном примере это указание является адресом блока запроса, описывающего команду, которую необходимо выполнить. Один вариант осуществления такого блока запроса представлен на ФИГ.4Б.

Как показано на ФИГ.4Б, в одном примере блок 420 запроса содержит ряд параметров, таких как, например, поле 422 длины, указывающее длину блока запроса; поле 424 команды, указывающее команду установки функции PCI; дескриптор 426 функции PCI, который является дескриптором, который необходимо передать функции активации или деактивации; код 428 операции, который используется для обозначения операции активации или деактивации; и число адресных пространств (DMAAS) 430, которое указывает запрошенное число адресных пространств, которое необходимо связывать с конкретной функцией PCI. В других вариантах осуществления может включаться больше или меньше информации, или другая информация.

Например, в виртуальной среде, в которой команда подается хостом или постраничным гостем режима сохранения, предоставляется обозначение гостя. Также возможны и другие варианты. В одном примере, в z/Architecture®, постраничный гость интерпретативно выполняется посредством команды Start Interpretive Execution (SIE), на 2 уровне интерпретации. Например, гипервизор логического разбиения (LPAR) выполняет команду SIE, чтобы начать логическое разбиение в физической постоянной памяти. Если в этом логическом разделе операционной системой является z/VM®, она подает команду SIE, чтобы выполнять свои гостевые (виртуальные) машины в своем V=V (виртуальном) запоминающем устройстве. Таким образом, гипервизор LPAR использует уровень - 1 SIE, а гипервизор z/VM® использует уровень - 2 SIE.

С учетом подачи и обработки команды Call Logical Processor, возвращается блок ответа, а информация, включаемая в блок ответа, зависит от операции, которую необходимо выполнить. Один вариант осуществления блока ответа представлен на ФИГ.4В. В одном примере блок 450 ответа включает поле 452 длины, указывающее длину блока ответа; код 454 ответа, указывающий состояние команды; и дескриптор 456 функции PCI, который определяет функцию PCI. С учетом команды активации дескриптор функции PCI является активированным дескриптором функции PCI. Кроме того, по завершении операции деактивации, дескриптор функции PCI является общим дескриптором, который может быть активирован функцией активации в будущем.

Один вариант осуществления логической схемы для активации функции PCI описывается со ссылкой на ФИГ.5. В одном примере эта логическая схема инициируется с учетом подачи команды Call Logical Processor, в которой устанавливается команда для команды установки функции PCI и устанавливается код операции для функции активации. Эта логическая схема выполняется, например, процессором с учетом операционной системы или драйвера устройства операционной системы, имеющих разрешение на выполнение этой логики, подающей команду. В других вариантах осуществления эта логическая схема может выполняться без использования команды Call Logical Processor.

Как показано на ФИГ.5, сначала на этапе 500 запроса осуществляется определение, является ли дескриптор, предоставленный в блоке запроса команды Call Logical Processor, достоверным дескриптором. То есть, указывает ли дескриптор на достоверную запись в таблице функций или же он находится за пределами диапазона достоверных записей (например, обозначает ли часть дескриптора с номером функции установленную функцию). Если дескриптор неизвестен, то предоставляется соответствующий код ответа, указывающий, что дескриптор не распознан. Однако если дескриптор известен, то на этапе 504 запроса осуществляется следующий запрос, активирован ли дескриптор. Это определение осуществляется проверкой указателя активации в дескрипторе функции PCI. Если указание, указывающее, что дескриптор активирован, установлено, то на этапе 506 возвращается код ответа, указывающий на это.

Однако если дескриптор известен и не активирован (т.е. действительный для активации), то на этапе 508 запроса осуществляется следующее определение, является ли запрошенное число адресных пространств, которые должны быть назначены функции PCI, большим, чем максимальное значение. Чтобы осуществить это определение, число адресных пространств DMA, как определено в блоке запроса, сравнивается с максимальным значением (предоставленным на основании политики, в одном примере). Если число адресных пространств больше, чем максимальное значение, то на этапе 510 предоставляется код ответа, указывающий на недостоверное значение для адресных пространств DMA. Иначе на этапе 512 осуществляется определение, доступно ли число запрошенных адресных пространств. Это определение осуществляется путем проверки, имеются ли записи таблицы устройств, доступные для запрошенного числа адресных пространств. Если число запрошенных адресных пространство недоступно, то на этапе 514 возвращается код ответа, указывающий, что ресурсов недостаточно. Иначе обработка продолжается, чтобы активировать функцию PCI.

Предоставленный дескриптор на этапе 516 используется для определения положения записи таблицы функций. Например, один или более указанных битов дескриптора используются в качестве индекса в таблице функций, чтобы определять положение конкретной записи таблицы функций. С учетом определения положения соответствующей записи таблицы функций, на этапе 518 запроса осуществляется определение, активирована ли функция. Это определение осуществляется путем проверки указателя активации в записи таблицы функций. Если функция уже активирована (т.е., указатель установлен в единицу), то на этапе 520 возвращается код ответа, указывающий, что функция PCI уже находится в запрошенном состоянии.

Если функция еще не активирована, то на этапе 522 запроса обработка продолжается определением, находится ли функция в состоянии постоянной ошибки. Если указатель состояния постоянной ошибки в записи таблицы функций указывает, что она находится в состоянии постоянной ошибки, то на этапе 524 возвращается код ответа, указывающий на это. Однако если функция не находится в состоянии постоянной ошибки, на этапе 526 запроса осуществляется следующее определение, было ли для функции инициировано восстановление после ошибки. Если указатель инициированного восстановления в записи таблицы функций установлен, то на этапе 528 предоставляется код ответа, указывающий, что восстановление было инициировано. Иначе на этапе 530 запроса осуществляется следующий запрос, занята ли функция PCI. И снова, если проверка указателя занятости в записи таблицы функций указывает, что функция PCI занята, то на этапе 532 предоставляется указание этого. Однако если функция PCI не находится в состоянии постоянной ошибки, восстановление не инициировано и она не занята, то на этапе 534 осуществляется следующий запрос, разрешается ли операционной системе активировать эту функцию PCI. Если это не разрешается на основании указателя разрешения записи таблицы функций, то на этапе 536 предоставляется код ответа, указывающий несанкционированное действие. Однако если все эти проверки успешно пройдены, то на этапе 538 запроса осуществляется следующее определение, имеются ли какие-либо записи DTE, доступные для этой функции PCI. В качестве примеров, определение доступных записей PCI может основываться на записях DTE, которые в текущее время не активированы в концентраторе ввода-вывода. Дополнительно для дальнейшего ограничения числа записей DTE, доступных для данной операционной системы или логического раздела, может применяться политика. Может быть назначена любая находящаяся в наличии DTE, доступная адаптеру. Если доступных записей DTE нет, то на этапе 540 возвращается код ответа, указывающий, что одна или более запрошенных записей DTE недоступны.

Если записи DTE доступны, то на этапе 542 ряд записей DTE, соответствующий запрошенному числу адресных пространств, назначается и активируется. В одном примере активация включает установку указателя активации в каждой DTE, подлежащей активации. Кроме того, активация включает, в этом примере, установку САМ, чтобы предоставлять индекс каждой DTE. Например, для каждой DTE, запись в САМ сохраняется с индексом.

Кроме того, на этапе 544 записи DTE связываются с записью таблицы функций. Это включает, например, включение каждого индекса DTE в запись таблицы функций. Функция затем на этапе 546 отмечается как активированная путем установки указателя активации в записи таблицы функций. Более того, на этапе 548 устанавливается бит активации в дескрипторе и обновляется номер экземпляра. Этот активированный дескриптор затем возвращается на этапе 550, позволяя использовать адаптер PCI. Например, с учетом активации функции, могут выполняться регистрация для трансляций адреса и прерываний, функцией PCI могут выполняться операции DMA; функцией могут запрашиваться прерывания; и/или функции могут подаваться команды загрузить, сохранить, сохранить блок и/или изменить управление функцией (например, PCI Load, PCI Store, PCI Store Block, Modify PCI Function Controls).

Один вариант осуществления логической схемы для деактивации функции PCI описывается со ссылкой на ФИГ.6. В этом примере команда установки функции PCI запрашивается посредством команды управления Call Logical Processor, в которой код операции установлен в состояние деактивировать; однако в других вариантах осуществления такая команда управления не используется. В одном примере эту логику выполняет операционная система или драйвер устройства операционной системы.

Как представлено на ФИГ.6, сначала на этапе 600 запроса осуществляется определение, является ли дескрипто