Сохранение/восстановление выбранных регистров при транзакционной обработке

Иллюстрации

Показать всеИзобретение относится к многопроцессорным вычислительным средам, а именно к транзакционной обработке внутри таких вычислительных сред. Техническим результатом является повышение скорости выполнения команды начать транзакцию благодаря сохранению содержимого только тех регистров, которые прямо указаны маской сохранения регистров общего назначения. Команда «начать транзакцию» начинает выполнение транзакции и включает маску сохранения регистров общего назначения, имеющую биты, которые если установлены, указывают регистры, которые необходимо сохранить в случае сброса транзакции. В начале транзакции содержимое регистров сохраняется в памяти, не доступной для программы, и если транзакция сбрасывается, сохраненное содержимое копируется в регистры. 2 н. и 12 з.п. ф-лы, 21 ил.

Реферат

Предпосылки создания изобретения

Один или более аспектов изобретения относится, в общем, к многопроцессорным вычислительным средам, и в частности, к транзакционной обработке внутри таких вычислительных сред.

Постоянной проблемой в многопроцессорном программировании являются обновления одной и той же ячейки памяти несколькими центральными процессорными устройствами (ЦП). Многие команды, обновляющие ячейки памяти, включая даже простые логические операции, такие как И (AND), производят это с множественным доступом к ячейке. Например, сначала считывается содержимое ячейки памяти, а потом обновленный результат возвращается обратно.

Для безопасного обновления одной и той же ячейки памяти несколькими процессорами, доступ к ячейке сделан сериализированным. Одна из команд, команда ПРОВЕРИТЬ И УСТАНОВИТЬ (TEST AND SET), введенная в архитектуре S/360, ранее предлагаемой корпорацией International Business Machines, обеспечивает взаимоблокированное обновление ячейки памяти. Взаимная блокировка обновления означает, что с точки зрения других процессоров и подсистемы ввода/вывода (I/O) (напр., подсистемы каналов), весь доступ к памяти для команды оказывается неделимым. Позже, в архитектуре S/370, предложенной корпорацией International Business Machines, были введены команды СРАВНИТЬ И ОБМЕНЯТЬ (COMPARE AND SWAP) и СРАВНИТЬ ДВАЖДЫ И ОБМЕНЯТЬ (COMPARE DOUBLE AND SWAP), предоставляющие более усложненные средства осуществления обновления с взаимоблокировкой, и делающие возможным реализацию того, что теперь известно как блокировочное слово (или семафор). Недавно введенные команды предоставили дополнительные возможности обновления с взаимоблокировкой, включая СРАВНИТЬ И ОБМЕНЯТЬ И ОЧИСТИТЬ (COMPARE AND SWAP AND PURGE) и СРАВНИТЬ И ОБМЕНЯТЬ И СОХРАНИТЬ (COMPARE AND SWAP AND STORE). Однако все эти команды обеспечивают взаимоблокировку только для единичной ячейки памяти.

Более сложные методы программирования могут потребовать взаимно блокированного обновления многих ячеек памяти, такие как добавление элемента к двусвязанному списку. При такой операции как прямой, так и обратный указатель должны выглядеть обновляемыми одновременно с точки зрения других процессоров и подсистемы ввода-вывода. Для того чтобы произвести такое обновление многих ячеек, программа вынуждена использовать отдельную, единичную точку сериализации, такую как блокировочное слово. Однако блокировочные слова могут предусматривать более грубый уровень сериализации, чем гарантированный; например, блокировочные слова могут перевести в последовательный режим целую очередь из миллионов элементов, хотя только два элемента обновляются. Программа может структурировать данные для использования более тонкой сериализации (напр., иерархии точек блокировки), но это вносит дополнительные трудности, такие как возможность тупиковой ситуации при нарушении иерархии, и проблемы с восстановлением, если программа сталкивается с ошибкой, удерживая одну или более блокировок, или блокировка не может быть запрошена.

В дополнение к вышесказанному, существует множество сценариев, в которых программа может выполнять последовательность команд, которые могут или не могут привести к ситуации исключения. Если ситуация исключения не наступает, программа продолжается; однако, если обнаружено исключение, программа может предпринять корректирующее действие для устранения ситуации исключения. Java, к примеру, может использовать такое выполнение для, например, упреждающего выполнения, частичного встраивания функции, и/или изменения последовательности проверки нуля указателя.

В средах классических операционных систем, таких как z/OS и ее предшественники, предложенные корпорацией International Business Machines, программа создает среду восстановления для перехвата любой ситуации программного исключения, которая может встретиться. Если программа не перехватывает исключение, операционная система обычно аварийно завершает программу для исключений, которые операционная система не готова обработать. Создание и использование такой среды затратно и сложно.

КРАТКОЕ ИЗЛОЖЕНИЕ

Недостатки уровня техники устраняются настоящим изобретением, которое может быть реализовано в виде машиночитаемого носителя информации как части компьютерного программного продукта для облегчения обработки транзакций внутри вычислительной среды. В носителе хранятся команды, считываемые и выполняемые обрабатывающим устройством во время обработки транзакций внутри вычислительной среды для выполнения способа, включающего: получение команды начать транзакцию, предназначенной для инициации транзакции и содержащей код операции, определяющий тип команды начать транзакцию, и поле, определяющее маску сохранения регистров общего назначения для явного указания одного или более регистров, которые могут быть выбраны из набора регистров и подлежат сохранению в начале транзакции на основе выполнения команды начать транзакцию, причем транзакция эффективно задерживает фиксацию транзакционных сохранений в главной памяти до тех пор, пока не завершится выбранная транзакция; и выполнение команды начать транзакцию, включающее сохранение содержимого только одного или более выбранных регистров, явно указанного(-ых) в маске сохранения регистров общего назначения команды начать транзакцию, и инициацию выполнения транзакции.

Объектом изобретения является также компьютерная система для облегчения обработки транзакций внутри вычислительной среды, содержащая память и процессор, сообщающийся с памятью, и настроенная для осуществления описанного выше способа. Технический результат, достигаемый при осуществлении изобретения, 4

заключается, в частности, в повышении скорости выполнения команды начать транзакцию благодаря сохранению содержимого только тех регистров, которые специально указаны.

КРАТКОЕ ОПИСАНИЕ НЕСКОЛЬКИХ ПРЕДСТАВЛЕНИЙ ЧЕРТЕЖЕЙ

Один или более аспектов выделены особо и явно объявлены как примеры в формуле изобретения в конце описания. Вышеуказанные и другие объекты, особенности и преимущества понятны из следующего подробного описания с помощью сопровождающих чертежей, в которых:

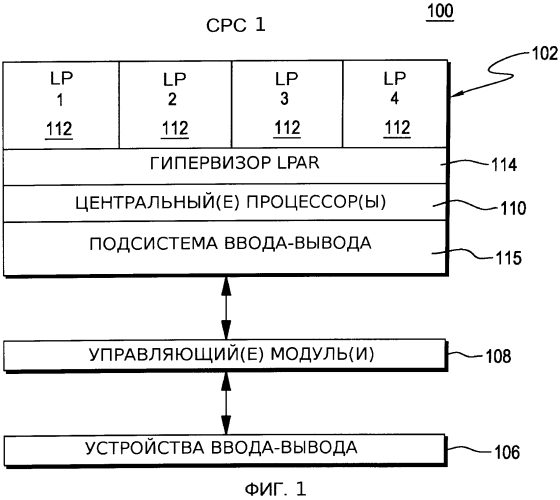

На Фиг. 1 изображен один из вариантов вычислительной среды;

На Фиг. 2А изображен один из примеров команды НАЧАТЬ ТРАНЗАКЦИЮ (TRANSACTION BEGIN) (TBEGIN);

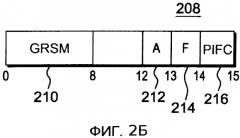

На Фиг. 2Б изображен в дальнейших подробностях один из вариантов поля команды TBEGIN согласно Фиг. 2А;

На Фиг. 3А изображен один из примеров команды НАЧАТЬ ТРАНЗАКЦИЮ ВЫНУЖДЕННО (TRANSACTION BEGIN CONSTRAINED) (TBEGINC);

На Фиг. 3Б изображен в дальнейших подробностях один из вариантов поля команды TBEGINC согласно Фиг. 3А;

На Фиг. 4 изображен один из примеров команды ЗАКОНЧИТЬ ТРАНЗАКЦИЮ (TRANSACTION END) (TEND);

На Фиг. 5 изображен один из примеров команды СБРОСИТЬ ТРАНЗАКЦИЮ (TRANSACTION ABORT) (TABORT);

На Фиг. 6 изображен один из примеров вложенных транзакций;

На Фиг. 7 изображен один из примеров команды НЕТРАНЗАКЦИОННОЕ СОХРАНЕНИЕ (NONTRANSACTIONAL STORE) (NTSTG);

На Фиг. 8 изображен один из примеров команды ИЗВЛЕЧЬ ГЛУБИНУ ВЛОЖЕНИЯ ТРАНЗАКЦИЙ (EXTRACT TRANSACTION NESTING DEPTH) (ETND);

На Фиг. 9 изображен один из примеров блока диагностики транзакций;

На Фиг. 10 изображены примеры причин сброса, вместе с соответствующими кодами сброса и кодами состояния;

На Фиг.11 изображен один из вариантов логики, связанный с выполнением команды TBEGINC;

На Фиг.12 изображен один из вариантов логики, связанный с выполнением команды TBEGIN;

На Фиг.13А-13Б изображены варианты воплощения логики, связанные с сохранением/восстановлением выбранных регистров при транзакционной обработке;

На Фиг.14А-14Б изображен пример вставки элемента очереди в двусвязанный список элементов очереди;

На Фиг.15 изображен один из вариантов компьютерного программного продукта;

На Фиг.16 изображен один из вариантов главной компьютерной системы;

На Фиг.17 изображен другой пример компьютерной системы;

На Фиг.18 изображен еще один пример компьютерной системы, содержащий компьютерную сеть;

На Фиг.19 изображен один из вариантов различных элементов компьютерной системы;

На Фиг.20А изображен один из вариантов исполнительного устройства компьютерной системы согласно Фиг.19;

На Фиг.20Б изображен один из вариантов устройства ветвления компьютерной системы согласно Фиг.19;

На Фиг.20B изображен один из вариантов устройства загрузки/сохранения компьютерной системы согласно Фиг.19; и

На Фиг.21 изображен один из вариантов эмулированной главной компьютерной системы.

ДЕТАЛЬНОЕ ОПИСАНИЕ

В соответствии с одним аспектом, предоставляется средство транзакционного выполнения (ТХ). Это средство обеспечивает транзакционную обработку команд, и в одном или более вариантов, предоставляет разные режимы выполнения, как описывается ниже, а также вложенные уровни транзакционной обработки.

Средство транзакционного выполнения вводит состояние процессора, называемое режимом транзакционного выполнения (ТХ). Сразу после перезагрузки процессора, процессор не находится в режиме ТХ. Процессор входит в режим ТХ по команде НАЧАТЬ ТРАНЗАКЦИЮ. Процессор выходит из режима ТХ или (а) по самой внешней команде ЗАКОНЧИТЬ ТРАНЗАКЦИЮ (подробности о внутреннем и внешнем следуют), или (б) если транзакция была сброшена. В режиме ТХ обращения процессора к памяти выглядят блочно-параллельными с точки зрения других процессоров и подсистемы ввода-вывода. Обращения к памяти или (а) фиксируются в памяти, если самая внешняя транзакция заканчивается без сброса (т.е., напр., обновления в кэше или буферах, локальных для процессора, распространяются и сохраняются в реальной памяти и видимы для других процессоров), или (б) отбрасываются, если транзакция сброшена.

Транзакции могут быть вложенными. То есть, пока процессор находится в режиме ТХ, он может выполнить другую команду НАЧАТЬ ТРАНЗАКЦИЮ. Команда, которая вызывает вход процессора в режим ТХ, называется самой внешней командой НАЧАТЬ ТРАНЗАКЦИЮ; аналогично говорят, что программа находится в самой внешней транзакции. Последующие выполнения команды НАЧАТЬ ТРАНЗАКЦИЮ называются внутренними командами; и программа выполняет внутреннюю транзакцию. Эта модель предусматривает минимальную глубину вложения и зависимую от модели максимальную глубину вложения. Команда ИЗВЛЕЧЬ ГЛУБИНУ ВЛОЖЕНИЯ ТРАНЗАКЦИЙ возвращает текущее значение глубины вложения, и, в последующем варианте, может возвращать максимальное значение глубины вложения. Эта методика использует модель, называемую "выровненное вложение", в которой состояние сброса при любой глубине вложения вызывает сброс всех уровней транзакции, и управление возвращается к команде, следующей за самой внешней НАЧАТЬ ТРАНЗАКЦИЮ.

Во время обработки транзакции считается, что транзакционное обращение, выполняемое одним процессором, конфликтует с (а) транзакционным или нетранзакционным обращением, выполняемым другим процессором, и (б) нетранзакционным обращением, выполняемым системой ввода-вывода, если оба обращения находятся в любом месте внутри одной строки кэша, и одно или оба обращения являются сохранением. Другими словами, для того чтобы транзакционное выполнение было продуктивным, не должно быть видно, что процессор совершает транзакционные обращения, пока они не зафиксируются. Эта модель программирования может быть очень эффективна в определенных средах; например, обновление двух точек в двусвязанном списке из миллиона элементов. Однако она может быть менее эффективна, если существует значительная конкуренция за позиции памяти, к которым производится транзакционное обращение.

В одной модели транзакционного выполнения (называемой здесь невынужденной транзакцией), когда транзакция сбрасывается, программа может или попытаться перезапустить транзакцию в надежде, что состояния сброса больше нет, или программа может "откатиться" на эквивалентный нетранзакционный путь. В другой модели транзакционного выполнения (называемой здесь вынужденной транзакцией), сброшенная транзакция автоматически перезапускается процессором; в отсутствие нарушения ограничений, вынужденная транзакция гарантированно завершается в итоге.

Запуская транзакцию, программа может задать различные проверки, такие как: (а) какие регистры общего назначения восстанавливают их изначальное содержимое в случае сброса транзакции, (б) разрешено ли транзакции изменять контекст регистров с плавающей точкой, включая, например, регистры с плавающей точкой и контрольный регистр с плавающей точкой, (в) разрешено ли транзакции изменять регистры доступа (AR), и (г) должны ли некоторые ситуации программного исключения быль блокированы от вызова прерывания. Если невынужденная транзакция сбрасывается, может быть предоставлена различная диагностическая информация. Например, самая внешняя команда TBEGIN, которая запускает невынужденную транзакцию, может задать программно-определяемый блок диагностики транзакции (TDB). Далее, TDB в префиксной зоне процессора или заданный описанием состояния хоста, также может использоваться, если транзакция сброшена из-за программного прерывания или состояния, которое вызывает завершение интерпретирующего выполнения, соответственно.

Выше указаны различные типы регистров. Далее они объясняются подробно. Регистры общего назначения могут использоваться как накопители в общих арифметических и логических операциях. В одном варианте каждый регистр содержит 64 двоичных разряда, и есть 16 регистров общего назначения. Регистры общего назначения идентифицируются по номерам 0-15 и обозначаются в команде четырехбитным полем R. Некоторые команды обеспечивают адресацию к нескольким регистрам общего назначения, имея несколько полей R. Для некоторых команд подразумевается использование особого регистра общего назначения вместо прямого указания в поле R команды.

Кроме использования в качестве накопителей в общих арифметических и логических операциях, 15 из 16 регистров общего назначения используются также как регистры базового адреса и индексные регистры для формирования адреса. В этих случаях регистры обозначаются в команде четырехбитным полем В или полем X. Нулевое значение в поле В или Х означает, что база или индекс не применяется, и таким образом, регистр общего назначения 0 не должен использоваться как содержащий базовый адрес или индекс.

Команды с плавающей точкой используют ряд регистров с плавающей точкой. Процессор имеет 16 регистров с плавающей точкой, в одном варианте. Регистры с плавающей точкой идентифицируются по номерам 0-15 и обозначаются в командах с плавающей точкой четырехбитным полем R. Каждый регистр с плавающей точкой является 64-битным и может содержать или короткий (32 бит) или длинный (64 бит) операнд с плавающей точкой.

Регистр управления плавающей точкой (FPC) - 32-битный регистр, который содержит биты маски, бит флага, код исключения данных и биты режима округления, и используется во время обработки операций с плавающей точкой.

Далее, в одном варианте, процессор имеет 16 управляющих регистров (CR), каждый из которых имеет 64 двоичных разряда. Двоичные разряды в регистрах закреплены за отдельными средствами в системе, такими как Запись Программных Событий (PER) (обсуждается ниже), и используются или для определения, какая операция может происходить, или для предоставления специальной информации, необходимой средству. В одном варианте для транзакционного средства используются CRO (биты 8 и 9) и CR2 (биты 61-63), как описано ниже.

Процессор имеет, например, 16 регистров доступа, пронумерованных 0-15. Регистр доступа состоит из 32 двоичных разрядов, содержащих косвенное определение элемента контроля пространства адресов (ASCE). Элемент контроля пространства адресов - параметр, используемый механизмом динамической трансляции адреса (DAT) для перевода ссылок в соответствующее пространство адресов. Когда процессор находится в режиме, называемом режимом регистра доступа (управляющимся битами в слове состояния программы (PSW)), поле В команды, использующееся для определения логического адреса для ссылки в операнде хранения, назначает регистр доступа, а элемент контроля пространства адресов, заданный регистром доступа, используется DAT для данной ссылки. Для некоторых команд используется поле R вместо поля В. Предоставляются команды для загрузки и сохранения содержимого регистров доступа и для перемещения содержимого одного регистра доступа в другой.

Каждый из регистров доступа 1-15 может определять любое пространство адресов. Регистр доступа 0 определяет первичное пространство команд. Когда один из регистров доступа 1-15 используется для определения пространства адресов, процессор выясняет, которое пространство адресов определяется, переводя содержимое регистра доступа. Когда регистр доступа 0 используется для определения пространства адресов, процессор рассматривает регистр доступа как определяющий первичное пространство команд, и не проверяет действительное содержание регистра доступа. Таким образом, 16 регистров доступа могут определять одновременно первичное пространство команд и максимум 15 других пространств.

В одном из вариантов существует несколько типов пространств адресов. Пространство адресов - непрерывная последовательность целых чисел (виртуальных адресов), вместе со специфическими параметрами трансляции, позволяющими связать каждое число с расположением байта в памяти. Последовательность начинается с нуля и продолжается слева направо.

В z/Architecture, например, когда виртуальный адрес используется процессором для обращения к главному запоминающему устройству (оно же главная память), он сперва превращается, с помощью динамической трансляции адреса (DAT), в реальный адрес, а затем, при помощи префиксации, в абсолютный адрес.DAT может использовать от одного до пяти уровней таблиц (страница, сегмент, регион третий, регион второй и регион первый) в качестве параметров трансляции. Определение (происхождение и длина) таблицы наивысшего уровня для отдельного пространства адресов называется элементом контроля пространства адресов, и находится для использования в DAT в управляющем регистре или определено регистром доступа. Иначе, элемент контроля пространства адресов для пространства адресов может быть обозначением реального пространства, которое указывает, что DAT должно транслировать виртуальный адрес, просто рассматривая его как реальный адрес без использования каких-либо таблиц.

DAT в разное время использует элементы контроля пространства адресов в разных управляющих регистрах или заданные регистрами доступа. Выбор определяется режимом трансляции, заданным в текущем PSW. Доступны четыре режима трансляции: режим первичного пространства, режим вторичного пространства, режим регистра доступа и режим домашнего пространства. Разные пространства адресов адресуются в зависимости от режима трансляции.

В любой момент, когда процессор находится в режиме первичного пространства или режиме вторичного пространства, процессор может транслировать виртуальные адреса, относящиеся к двум пространствам адресов - первичному пространству адресов и вторичному пространству адресов. В любой момент, когда процессор находится в режиме регистра доступа, он может транслировать виртуальные адреса вплоть до 16 пространств адресов - первичное пространство адресов и вплоть до 15 пространств адресов, заданных AR. В любой момент, когда процессор находится в режиме домашнего пространства, он может транслировать виртуальные адреса домашнего пространства адресов.

Первичное пространство адресов обозначается так, потому что оно состоит из первичных виртуальных адресов, которые транслируются с помощью первичного элемента контроля пространства адресов (ASCE). Аналогично, вторичное пространство адресов состоит из вторичных виртуальных адресов, транслирующихся с помощью вторичного ASCE; пространства адресов, заданные AR, состоят из виртуальных адресов, заданных AR, транслирующихся при помощи ASCE, заданных AR; и домашнее пространство адресов состоит из домашних виртуальных адресов, транслирующихся при помощи домашнего ASCE. Первичные и вторичные ASCE находятся в управляющих регистрах 1 и 7 соответственно. ASCE, заданные AR, находятся в пунктах второй таблицы НПА, которые находятся с помощью процесса, называемого трансляцией регистра доступа (ART) при помощи управляющего регистра 2, 5 и 8. Домашний ASCE находится в управляющем регистре 13.

Один из вариантов вычислительной среды, включающий и использующий один или более аспектов описываемого здесь транзакционного средства, описывается при помощи Фиг.1.

Согласно Фиг.1, в одном примере, вычислительная среда 100 основывается на архитектуре z/Architecture, предлагаемой корпорацией International Business Machines (IBM®), Армонк, штат Нью-Йорк. z/Architecture описана в публикации IBM, озаглавленной "z/Architecture - Principles of Operation," публикация № SA 22-7932-08, 9 издание, август 2010, которая включается сюда по ссылке во всей ее целостности.

Z/ARCHITECTURE, IBM, Z/OS и Z/VM (упоминаемые ниже) являются зарегистрированными торговыми марками корпорации International Business Machines, Армонк, штат Нью-Йорк. Другие названия, использованные здесь, могут быть зарегистрированными торговыми марками, торговыми марками или названиями изделий корпорации International Business Machines или других компаний.

В качестве примера, вычислительная среда 100 включает центральный процессорный комплекс (СРС) 102, соединенный с одним или более устройств ввода-вывода 106 через один или более управляющих модулей 108. Центральный процессорный комплекс 102 включает, например, один или более центральных процессоров 110, один или более разделов 112 (напр., логических разделов (LP)), гипервизор логических разделов 114 и подсистему ввода-вывода 115, каждый из которых описывается ниже.

Центральные процессоры 110 являются ресурсами физического процессора, выделенные логическим разделам. В частности, каждый логический раздел 112 имеет один или более логических процессоров, каждый из которых представляет собой весь или часть физического процессора 110, выделенную разделу. Логические процессоры отдельного раздела 112 могут быть или закреплены за разделом, так что лежащий в основе ресурс процессора 110 зарезервирован за этим разделом; или разделены с другим разделом, так что лежащий в основе ресурс процессора потенциально доступен для другого раздела.

Логический раздел функционирует как отдельная система и имеет одно или несколько приложений и, опционально, резидентную операционную систему внутри, которая может отличаться для каждого логического раздела. В одном варианте операционной системой является операционная система z/OS, операционная система z/VM, операционная система z/Linux или операционная система TPF, предлагаемая корпорацией International Business Machines, Армонк, штат Нью-Йорк. Логические разделы 112 управляются гипервизором 114 логических разделов, который реализуется микропрограммой, выполняющейся на процессорах 110. В данном контексте, микропрограмма включает, напр., микрокод и/или милликод процессора. Она включает, например, команды аппаратного уровня и/или структуры данных, используемые в реализации машинного кода высокого уровня. В одном варианте она включает, например, проприетарный код, который обычно поставляется как микрокод, который включает достоверное программное обеспечение или микрокод, специфичный для нижележащего аппаратного обеспечения, и управляет доступом операционной системы к системному аппаратному обеспечению.

Каждый из логических разделов и гипервизор логических разделов включают одну или более программ, постоянно находящихся в соответствующих разделах центрального запоминающего устройства, связанного с центральными процессорами. Одним из примеров гипервизора 114 логических разделов является Администратор Системы/Ресурсов Процессора (Processor Resource/System Manager (PR/SM)), предлагаемый корпорацией International Business Machines, Армонк, штат Нью-Йорк.

Подсистема 115 ввода-вывода направляет поток информации между устройствами 106 ввода-вывода и главным запоминающим устройством (оно же главная память). Она соединяется с центральным процессорным комплексом, в котором она может быть частью центрального процессорного комплекса, или отделена от него. Подсистема ввода-вывода облегчает центральным процессорам задачу прямой связи с устройствами ввода-вывода и позволяет производить обработку данных параллельно с обработкой ввода-вывода. Для обеспечения связи подсистема ввода-вывода использует адаптеры связи ввода-вывода. Существуют различные типы адаптеров связи, включая, например, каналы, адаптеры ввода-вывода, платы PCI, платы Ethernet, платы Интерфейса Малого Компьютерного Хранилища (SCSI) и т.д. В отдельном примере, описанном здесь, адаптерами связи ввода-вывода являются каналы, и, таким образом, подсистема ввода-вывода называется здесь канальной подсистемой. Однако это лишь один из примеров. Могут использоваться другие типы подсистем ввода-вывода.

Подсистема ввода-вывода использует один или более путей ввода-вывода в качестве линий связи, управляя потоком информации к устройствам 106 или от них. В этом отдельном примере эти пути называются канальными путями, так как адаптеры связи являются каналами.

Вычислительная среда, описанная выше, является лишь одним примером вычислительной среды, которая может использоваться. Могут использоваться другие среды, включая, но не ограничиваясь, неразделенные среды, другие разделенные среды и/или эмулированные среды; варианты не ограничиваются любой одной средой.

В соответствии с одним или более аспектами, средство транзакционного выполнения является усовершенствованием процессора, которое предоставляет средства, с помощью которых процессор может выполнить последовательность команд (известную как транзакция), которая может обращаться ко многим ячейкам памяти, включая обновление этих ячеек. С точки зрения других процессоров и подсистемы ввода-вывода, транзакция или (а) завершается во всей целостности как единичная атомарная операция, или (б) сбрасывается, потенциально не оставляя никаких свидетельств того, что она вообще выполнялась (за исключением некоторых ситуаций, описанных здесь). Таким образом, успешно завершенная транзакция может обновить множество ячеек памяти без какой-либо особой блокировки, которая нужна в классической многопроцессорной модели.

Средство транзакционного выполнения включает, например, одну или более директив; одну или более команд; обработку транзакций, включая вынужденное и невынужденное выполнение; и обработку сброса, каждая из которых далее описывается ниже.

В одном варианте воплощения изобретения, для управления средством транзакционного выполнения используются три директивы специального назначения, включая Слово Состояния Программы (PSW) сброса транзакции, адрес блока диагностики транзакций (TDB) и глубину вложения транзакций; пять бит управляющего регистра; и шесть общих команд, включая НАЧАТЬ ТРАНЗАКЦИЮ (вынужденную и невынужденную), ЗАКОНЧИТЬ ТРАНЗАКЦИЮ, ИЗВЛЕЧЬ ГЛУБИНУ ВЛОЖЕНИЯ ТРАНЗАКЦИЙ и НЕТРАНЗАКЦИОННОЕ СОХРАНЕНИЕ. Когда средство инсталлируется, оно инсталлируется, например, на все процессоры в конфигурации. Обозначение средства, бит 73 в одной реализации, будучи единицей, указывает, что установлено средство транзакционного выполнения.

Когда установлено средство транзакционного выполнения, конфигурация предоставляет средство невынужденного транзакционного выполнения и, опционально, средство вынужденного транзакционного выполнения, каждое из которых описывается ниже. Если обозначения средства 50 и 73, к примеру, оба равны единице, установлено средство вынужденного транзакционного выполнения. Оба обозначения средства хранятся в памяти в определенных позициях.

В данном контексте название команды НАЧАТЬ ТРАНЗАКЦИЮ относится к командам с сокращениями TBEGIN (Начать Транзакцию для невынужденной транзакции) и TBEGINC (Начать Транзакцию для вынужденной транзакции). Рассуждения, касающиеся специфических команд, обозначаются названием команды с последующим сокращением в скобках, или только сокращением.

Один из вариантов формата команды НАЧАТЬ ТРАНЗАКЦИЮ (TBEGIN) изображен на Фиг.2А-2Б. К примеру, команда TBEGIN 200 включает поле кода операции 202, которое включает код операции, определяющий невынужденную операцию начала транзакции; базовое поле (B1) 204; поле смещения (D1) 206; и непосредственное поле (12) 208. Если поле B1 не нуль, содержимое регистра общего назначения, определенного B1 204, складывается с D1 206 для получения адреса первого операнда.

Если поле B1 не нуль, применяется следующее:

- Если глубина вложения транзакции изначально нуль, адрес первого операнда определяет положение 256-байтного блока диагностики транзакций, называемого TDB, заданный TBEGIN (далее описан ниже), в котором может сохраняться различная диагностическая информация, если транзакция сбрасывается. Если процессор находится в режиме первичного пространства или в режиме регистра доступа, адрес первого операнда определяет позицию в первичном пространстве адресов. Если процессор находится в режиме вторичного пространства или в режиме домашнего пространства, адрес первого операнда определяет позицию во вторичном или домашнем пространстве адресов соответственно. Если DAT выключено, адрес блока диагностики транзакций (TDBA) определяет позицию в реальном запоминающем устройстве.

Определяется доступность памяти для первого операнда. Если доступно, логический адрес операнда помещается в адрес блока диагностики транзакций (TDBA), и TDBA действителен.

- Если процессор уже находится в режиме невынужденного транзакционного выполнения, TDBA не изменяется, и нельзя предсказать, проверен ли первый операнд на доступность.

Если поле B1 равно нулю, не обнаруживаются исключения доступа для первого операнда и, для самой внешней команды TBEGIN, TDBA недействителен.

Биты поля I2 определяются следующим образом, к примеру:

Маска сохранения регистров общего назначения (General Register Save Mask) (GRSM) 210 (Фиг.2Б): Биты 0-7 поля I2 содержат маску сохранения регистров общего назначения (GRSM). Каждый бит GRSM представляет четно-нечетную пару регистров общего назначения, где бит 0 представляет регистры 0 и 1, бит 1 представляет регистры 2 и 3 и так далее. Если бит в GRSM самой внешней команды TBEGIN равен нулю, соответствующая пара регистров не сохраняется. Если бит в GRSM самой внешней команды TBEGIN равен единице, соответствующая пара регистров сохраняется в зависящем от модели месте, которое недоступно программе напрямую.

Если транзакция сбрасывается, сохраненные пары регистров восстанавливают свое содержимое на момент, когда выполнялась самая внешняя команда TBEGIN. Содержимое всех других (несохраненных) регистров общего назначения не восстанавливается, если транзакция сбрасывается.

Маска сохранения регистров общего назначения игнорируется всеми TBEGIN, за исключением самой внешней.

Разрешить Изменение AR (Allow AR Modification) (A) 212: Директива А, бит 12 поля I2, контролирует, разрешено ли транзакции изменять регистр доступа. Эффективная директива разрешения изменения AR является логическим И (AND) директивы А в команде TBEGIN для текущего уровня вложения и для всех внешних уровней.

Если эффективная директива А равна нулю, транзакция будет сброшена с кодом сброса 11 (недопустимая команда), если будет сделана попытка изменить любой регистр доступа. Если эффективная директива А равна единице, транзакция не будет сброшена, если регистр доступа будет изменен (в отсутствие любых других причин сброса).

Разрешить Операцию с Плавающей Точкой (Allow Floating Point Operation) (F) 214: Директива F, бит 13 поля I2, контролирует, разрешено ли транзакции выполнять определенные команды с плавающей точкой. Эффективная директива разрешения операции с плавающей точкой является логическим И (AND) директивы F в команде TBEGIN для текущего уровня вложения и для всех внешних уровней.

Если эффективная директива F равна нулю, то (а) транзакция будет сброшена с кодом сброса 11 (недопустимая команда), если будет сделана попытка выполнить команду с плавающей точкой, и (б) код исключения данных (DXC) в байте 2 управляющего регистра с плавающей точкой (FPCR) не будет установлен никаким состоянием исключения программы исключения данных. Если эффективная директива F равна единице, то (а) транзакция не будет сброшена, если будет сделана попытка выполнить команду с плавающей точкой (в отсутствие любых других причин сброса), и (б) DXC в FPCR может быть установлен состоянием исключения программы исключения данных.

Директива Фильтрации Прерывания Программы (Program Interruption FilteRing Control) (PIFC) 216: Биты 14-15 поля I2 являются директивой фильтрации прерывания программы (PIFC). PIFC контролирует, вызывают ли прерывание некоторые классы ситуаций программного исключения (напр., исключение адресации, исключение данных, исключение операций, исключение защиты и т.д.), которые происходят, пока процессор находится в режимы транзакционного выполнения.

Эффективная PIFC является наивысшей величиной PIFC в команде TBEGIN для текущего уровня вложения и для всех внешних уровней. Если эффективная PIFC равна нулю, все ситуации программного исключения вызывают прерывание. Если эффективная PIFC равна единице, ситуации программного исключения, имеющие класс транзакционного выполнения 1 и 2, вызывают прерывание. (Каждой ситуации программного прерывания назначен как минимум один класс транзакционного выполнения, зависящий от серьезности исключения. Важность основывается на вероятности восстановления во время повторного выполнения транзакции, и нужно ли операционной системе видеть прерывание). Если эффективная PIFC равна двум, ситуации программного исключения, имеющие класс транзакционного выполнения 1, вызывают прерывание. PIFC, равный 3, зарезервирован.

Биты 8-11 поля I2 (биты 40-43 команды) зарезервированы и должны содержать нули; иначе, программа не сможет совместимо работать в будущем.

Один из вариантов формата инструкции НАЧАТЬ ТРАНЗАКЦИЮ ВЫНУЖДЕННО (TBEGINC) описан при помощи Фиг.3А-3Б. В одном примере команда TBEGINC 300 включает поле кода операции 302, которое включает код операции, определяющий вынужденную операцию начала транзакции; базовое поле (B1) 304; поле смещения (D1) 306; и непосредственное поле (I2) 308. Содержимое регистра общего назначения, определенного B1 304 складывается с D1 306 для получения адреса первого операнда. Однако при команде вынужденного начала транзакции адрес первого операнда не используется для обращения к памяти. Вместо этого поле В1 команды включает нули; иначе обнаруживается исключение определения.

В одном из вариантов поле I2 включает различные директивы, пример которых изображен на Фиг.3Б.

Биты поля I2 определяются следующим образом, к примеру:

Маска сохранения регистров общего назначения (General Register Save Mask) (GRSM) 310: Биты 0-7 поля I2 содержат маску сохранения регистров общего назначения (GRSM). Каждый бит GRSM представляет четно-нечетную пару регистров общего назначения, где бит 0 представляет регистры 0 и 1, бит 1 представляет регистры 2 и 3 и так далее. Если бит в GRSM равен нулю, соответствующая пара регистров не сохраняется. Если бит в GRSM равен единице, соответствующая пара регистров сохраняется в зависящем от модели месте, которое недоступно программе напрямую.

Если транзакция сбрасывается, сохраненные пары регистров восстанавливают свое содержимое на момент, когда выполнялась самая внешняя команда НАЧАТЬ ТРАНЗАКЦИЮ. Содержимое всех других (несохраненных) регистров общего назначения не восстанавливается, если вынужденная транзакция сбрасывается.

Если TBEGINC используется для продолжения выполнения в режиме выполнения невынужденной транзакции, маска сохранения регистров общего назначения игнорируется.

Разрешить Изменение AR (Allow AR Modification) (A) 312: Директива А, бит 12 поля I2, контролирует, разрешено ли транзакции изменять регистр доступа. Эффективная директива разрешения изменения AR является логическим И (AND) директивы А в команде TBEGINC для текущего уровня вложения и для любых внешних команд TBEGIN или TBEGINC.

Если эффективная директива А равна нулю, транзакция будет сброшена с кодом сброса 11 (недопустимая команда), если будет сделана попытка изменить любой регистр доступа. Если эффективная директива А равна единице, транзакция не будет сброшена, если регистр доступа б