Увеличение числа доступных для команд регистров общего назначения

Иллюстрации

Показать всеГруппа изобретений относится к компьютерной технике и может быть использована в процессорах компьютерной системы. Техническим результатом является реализация команд, согласующихся с существующей архитектурой, уменьшающих зависимость от ресурсов архитектуры и улучшение производительности версий программного обеспечения. В заявке описано применение в компьютере набора регистров общего назначения (РОН). Каждый РОН имеет множество частей. Программы, такие как операционная система и приложения, действующие в режиме больших РОН, имеют доступ ко всему РОН, а программы, такие как приложения, действующие в режиме малых РОН, единовременно имеют доступ только к его части. В режиме малых РОН коды команд могут определять часть, доступ к которому осуществляется. 3 н. и 8 з.п. ф-лы, 18 ил.

Реферат

Настоящее изобретение относится к компьютерным системам, точнее, к функциональным возможностям команд процессора компьютерной системы.

Товарные знаки: IBM® является зарегистрированным товарным знаком International Business Machines Corporation (Армонк, штат Нью-Йорк, США). S/390, Z900, z990 и z10, а также названия других продуктов, используемые в описании, могут являться зарегистрированными товарными знаками или названиями продуктов International Business Machines Corporation или других компаний.

Начиная с появившихся в 60-х годах машин, известных как IBM® System 360, и до настоящего времени усилиями множества высокоодаренных инженеров IBM была создана особая архитектура, которая получила известность как "мэйнфрейм" в силу своей неотъемлемой принадлежности к вычислительной системе и принципы работы которой определяют архитектуру машины путем описания команд, которые могут выполняться путем реализации в "мэйнфрейме" созданных изобретателями IBM команд, которые с учетом их существенной роли в течение многих лет включены в руководство IBM Principles of Operation. Восьмое издание руководства IBM® z/Architecture® Principles of Operation, опубликованное в феврале 2009 г., стало стандартным справочным материалом SA22-7832-07 и включено в описание серверов на основе мэйнфреймов IBM z10®, включая серверы корпоративного класса на основе системы IBM z10®.

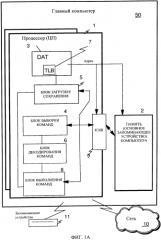

На фиг. 1А представлены характерные элементы известной из техники главной компьютерной системы 50. В компьютерной системе также могут применяться другие варианты размещения элементов, которые хорошо известны из техники. Характерный главный компьютер 50 содержит один или несколько ЦП 1, связанных с основным запоминающим устройством (памятью 2 компьютера), а также интерфейсы ввода-вывода для сопряжения с запоминающими устройствами 11 и подключения к сетям 10 для связи с другими компьютерами или SAN и т.п. ЦП 1 совместим с архитектурой, содержащей структурированную систему команд и структурированные функциональные возможности. ЦП 1 может осуществлять динамическую трансляцию 3 адреса (DAT) с целью преобразования адресов программ (виртуальных адресов) в действительный адрес памяти. DAT обычно содержит буфер 7 быстрого преобразования адреса (TLB) для кэширования преобразований, чтобы при последующих доступах к блоку памяти 2 компьютера не требовалась задержка трансляции адреса. Обычно между памятью 2 компьютера и процессором 1 используется кэш-память 9. Кэш-память 9 может являться иерархической и состоящей из кэша большой емкости, доступного для нескольких ЦП, и более быстродействующих кэшей (низкого уровня) меньшей емкости между кэшем большой емкости и каждым ЦП. В некоторых случаях реализации кэши низкого уровня разделены на отдельные кэши низкого уровня для выборки команд и доступа к данным. В одном из вариантов осуществления блок 4 выборки команд вызывает из памяти 2 команду посредством кэш-памяти 9. Команда декодируется в блоке 6 декодирования команд и отправляется (с другими командами в некоторых вариантах осуществления) в блоки 8 выполнения команд. Обычно используется несколько блоков 8 выполнения команд, например, блок выполнения арифметических команд, блок выполнения команд с плавающей точкой и блок выполнения команд перехода. Команда выполняется блоком, который в зависимости от необходимости осуществляет доступ к операндам из определяемых командами регистров или памяти. Если доступ (загрузка или сохранение) к операнду должен осуществляться из памяти 2, блок 5 загрузки/сохранения обычно обрабатывает процедуру доступа под управлением выполняемой команды. Команды могут выполняться в аппаратных схемах или во внутреннем микрокоде (аппаратно-программном обеспечении) или с использованием сочетания того и другого.

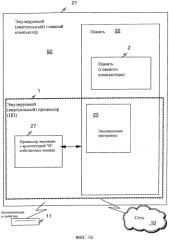

На фиг. 1Б проиллюстрирован один из примеров известной из техники главной компьютерной системы 21 эмуляции, которая эмулирует главную компьютерную систему 50, имеющую главную архитектуру. Главным центральным процессором (ЦП) 1 в главной компьютерной системе 21 эмуляции является главный процессор (или виртуальный главный процессор) эмуляции, представляющий собой процессор 27 эмуляции со структурой собственных команд, отличающейся от структуры команд процессора 1 главного компьютера 50. Главная компьютерная система 21 эмуляции имеет память 22, доступную для процессора 27 эмуляции. В примере осуществления память 22 разделена на память 2 главного компьютера и память 23 программ эмуляции. Память 2 главного компьютера доступна для программ главного компьютера 21 эмуляции в зависимости от архитектуры главного компьютера. Процессор 27 эмуляции выполняет собственные команды структурированной системы команд, структура которых отличается от структуры команд эмулируемого процессора 1 и которые извлекаются из памяти 23 программ эмуляции, и может осуществлять выборку главной команды для выполнения из программы в памяти 2 главного компьютера путем применения одной или нескольких команд из программы контроля последовательности и выборки/декодирования (Sequence & Access/Decode), которая может декодировать выбранную главную команду(-ы) и определять программу выполнения собственных команд с целью эмуляции функции выбранной главной команды. Другие средства, которые предусмотрены в архитектуре главной компьютерной системы 50, могут эмулироваться программами структурированных средств (Architected Facilities Routines), включая такие средства, как, например, регистры общего назначения, управляющие регистры, поддержка подсистемы динамической трансляции адреса и ввода-вывода и кэш-память процессора. Программы эмуляции также могут использовать функции, доступные в процессоре 27 эмуляции (такие как регистры общего назначения и динамическая трансляция виртуальных адресов) для повышения производительности программ эмуляции. Также может быть предусмотрено особое программное обеспечение и механизмы разгрузки, облегчающие процессору 27 эмуляцию функции главного компьютера 50.

В мэйнфрейме структурированные машинные команды используются программаторами, обычно современными программаторами на языке "С" посредством компилирующего приложения. Эти команды, хранящиеся в запоминающей среде, могут выполняться в собственной системе команд сервера IBM® на основе z/Architecture® или в качестве альтернативы в машинах на основе других архитектур. Они могут эмулироваться в существующих и будущих серверах на основе мэйнфреймов IBM® и в других машинах IBM® (например, серверах pSeries® и xSeries®). Они могут выполняться в операционной системе Linux разнообразными машинами, использующими аппаратное обеспечение производства IBM®, Intel, AMD™, Sun Microsystems и других компаний. Помимо выполнения этим аппаратным обеспечением на основе системы Z/Architecture®, может использоваться Linux, а также машины, использующие эмуляцию, как описано на сайтах http://www.turbohercules.com, http://www.hercules-390.org и http://www.funsoft.com. В режиме эмуляции эмулирующее программное обеспечение выполняется собственным процессором, эмулирующим архитектуру эмулируемого процессора.

Собственный процессор 27 обычно выполняет эмулирующее программное обеспечение 23, представляющее собой аппаратно-программное обеспечение или собственную операционную систему для эмуляции эмулируемого процессора. Эмулирующее программное обеспечение 23 отвечает за выборку и выполнение команд архитектуры эмулируемого процессора. Эмулирующее программное обеспечение 23 поддерживает счетчик эмулируемых команд для слежения за границами команд. Эмулирующее программное обеспечение 23 может осуществлять выборку одной или нескольких эмулируемых машинных команд за один раз и преобразование одной или нескольких эмулируемых машинных команд в соответствующую группу собственных машинных команд для выполнения собственным процессором 27. Эти преобразованные команды могут помещаться в кэш, что позволяет ускорять преобразование. Тем не менее, эмулирующее программное обеспечение должно поддерживать правила архитектуры эмулируемого процессора с тем, чтобы обеспечивать правильную работу операционных систем и приложений, написанных для эмулируемого процессора. Кроме того, эмулирующее программное обеспечение должно обеспечивать ресурсы, указанные архитектурой эмулируемого процессора 1, включая без ограничения управляющие регистры, регистры общего назначения, регистры с плавающей точкой, функцию динамической трансляции адреса, включая таблицы сегментов и таблицы страниц, например, механизмы прерывания, механизмы переключения контекста, часы истинного времени (TOD) и структурированные интерфейсы с подсистемами ввода-вывода с тем, чтобы операционная система или прикладная программа, рассчитанная на работу в эмулируемом процессоре, могла быть запущена в собственном процессоре, имеющем эмулирующее программное обеспечение.

Декодируется конкретная эмулируемая команда, и вызывается подпрограмма для выполнения функции отдельной команды. Функция 23 эмулирующего программного обеспечения, эмулирующая функцию эмулируемого процессора 1, реализуется, в подпрограмме или драйвере на языке "С" или каким-либо другим способом обеспечения драйвера для конкретного аппаратного обеспечения, доступным для специалистов в данной области техники, ознакомившихся в описанием предпочтительного варианта осуществления. В различных патентах, в которых предложена эмуляция программного и аппаратного обеспечения, включая без ограничения патент US 5551013 под названием "Multiprocessor for hardware emulation", выданный на имя Beausoleil и др., патент US 6009261 под названием "Preprocessing of stored target routines for emulating incompatible instructions on a target processor", выданный на имя Scalzi и др.; патент US 5574873 под названием "Decoding guest instruction to directly access emulation routines that emulate the guest instructions", выданный на имя Davidian и др.; патент US 6308255 под названием "Symmetrical multiprocessing bus and chipset used for coprocessor support allowing non-native code to run in a system", выданный на имя Gorishek и др.; патент US 6463582 под названием "Dynamic optimizing object code translator for architecture emulation and dynamic optimizing object code translation method", выданный на имя Lethin и др.; патент US 5790825 под названием "Method for emulating guest instructions on a host computer through dynamic recompilation of host instructions", выданный на имя Eric Traut, проиллюстрированы разнообразные известные способы эмуляции формата команд, структурированного для отличающейся машины, в целевой машине, доступные для специалистов в данной области техники, а также используемые ими промышленные средства программного обеспечения.

В публикации заявки US 2009/0249039 А1 от 1 октября 2009 г. (заявитель -Hook и др.) под названием" Providing Extended Precision in SIMD Vector Arithmetic Operations" предложена повышенная точность арифметических операций SIMD в процессоре, имеющем регистровый файл и аккумулятор. В первый и второй векторные регистры, соответственно, загружаются первый набор элементов данных и второй набор элементов данных. Каждый элемент данных содержит N разрядов. Затем из памяти вызывается команда арифметической операции. Команда арифметической операции декодируется. Затем из регистрового файла считываются первый векторный регистр и второй векторный регистр. В первом и втором векторных регистрах выполняется команда арифметической операции с соответствующими элементами данных. Затем полученный в результате выполнения элемент записывается в аккумулятор. После этого полученный элемент трансформируется в N-разрядный элемент и записывается в третий регистр для последующего оперирования или хранения в памяти. Трансформации полученного элемента может включать, например, округление, фиксацию и/или сдвиг элемента.

Существует потребность в командах с новыми функциональными возможностями, согласующимися с существующей архитектурой, уменьшающими зависимость от ресурсов архитектуры, таких как регистры общего назначения, и улучшающими функциональные возможности и производительность версий программного обеспечения, в которых применяется новая команда.

В руководстве International Business Machines Corporation под названием z/Architecture® Principles of Operation, SA22-7832-07, опубликованном в феврале 2009 г., описан порядок обработки сигналов с переключением между (24- или 31-разрядным) режимом архитектуры ESA/390 и (64-разрядным) режимом z/Architecture. Команда, оперирующая в режиме ESA/390 с двоичными разрядами 0-31 32-битового разряда, вместо этого оперирует в z/Architecture с двоичными разрядами 32-63 64-разрядного регистра. В режиме ESA/390 не используются разряды 0-31 64-разрядных регистров z/Architecture.

В заявке WO 98/12627 А1 описаны слова команды, имеющие поле разрядов исходного регистра с указанием исходного регистра множества 32-разрядных регистров, в которых хранится слово данных входных операндов. В слове команды также содержится разряд размера, указывающий, должны ли считываться все 32 разряда регистра или только 16 младших разрядов или 16 старших разрядов.

В соответствии с изобретением, на основе функции старшего слова (High-Word) в компьютере, имеющем первое число больших регистров общего назначения (РОН), увеличено эффективное число РОН, доступных для команд программы, при этом каждая команда содержит код операции и одно или несколько полей РОН для указания соответствующих РОН, каждый большой РОН содержит первую часть и вторую часть, упомянутые большие РОН содержат первые малые РОН, состоящие из первых частей, и вторые малые РОН, состоящие из вторых частей, компьютер имеет режим малых РОН, в котором в качестве основанных на РОН адресов операндов в основной памяти используются только операнды первых малых РОН, и режим больших РОН, в котором в качестве основанных на РОН адресов операндов в основной памяти используются операнды, перекрывающие как первые малые РОН, так и вторые малые РОН. При этом способ увеличения эффективного числа РОН, доступных для команд программы в компьютере, включает: (а) выполняемое на основании слова состояния программы определение того, находится ли компьютер в режиме малых РОН или в режиме больших РОН, причем в режиме малых РОН разрешается выполнение программ, написанных для компьютера с архитектурой малых РОН, в которой адреса памяти и регистровые операнды ограничены размером малого РОН, (б) выполняемое, если функция старшего слова на компьютере включена (разрешена), блокирование выполнения второго набора команд, причем в компьютере имеется поле, управляющее включением или отключением функции старшего слова, (в) выполняемое при нахождении компьютера в режиме малых РОН выполнение команд из первого набора команд, предназначенного для доступа к первым малым РОН, включающее генерирование адресов памяти для доступа к хранимым в памяти операндам на основании первых малых РОН или доступа к операндам первых малых РОН, состоящих из упомянутых первых частей, и выполняемое при включенной функции старшего слова выполнение команд из второго набора команд, предназначенного для доступа ко вторым малым РОН, включающее генерирование адресов памяти для доступа к хранимым в памяти операндам на основании вторых малых РОН или доступа к операндам вторых малых РОН, состоящих из упомянутых вторых частей, и (г) выполняемое при нахождении компьютера в режиме больших РОН выполнение команд из третьего набора команд, включающее генерирование адресов памяти для доступа к хранимым в памяти операндам на основании больших РОН или доступа к операндам больших РОН, содержащих упомянутые первые части и упомянутые вторые части.

В одном из вариантов осуществления, режим малых РОН предусматривает нахождение в режиме 24-разрядной адресации или режиме 31-разрядной адресации.

В одном из вариантов осуществления, первая часть содержит 32 разряда, вторая часть содержит 32 разряда, а третья часть содержит 64 разряда.

В одном из вариантов осуществления выполнение команды из второго набора команд включает в себя выполнение заданной соответствующим кодом операции функции на основании двух операндов и сохранение результата, при этом заданная соответствующим кодом операции функция состоит из функции сложения двух операндов или функции сравнения двух операндов.

В одном из вариантов осуществления выполнение команды из второго набора команд включает в себя выполнение заданной соответствующим кодом операции функции на основании двух операндов и сохранение результата, при этом заданной соответствующим кодом операции функцией является функция загрузки операнда из памяти или функция сохранения операнда в памяти.

В одном из вариантов осуществления выполнение команды из второго набора команд включает в себя выполнение заданной соответствующим кодом операции функции на основании двух операндов и сохранение результата, при этом заданной соответствующим кодом операции функцией является функция поворота с последующей вставкой выбранных разрядов (ROTATE THEN INSERT SELECTED BITS), включающая поворот исходного операнда на заданную командой величину и вставку выбранной части повернутого исходного операнда в выбранную часть целевого операнда.

В одном из вариантов осуществления поддерживается операционная система, действующая в режиме больших РОН, при этом большие РОН сохраняются и восстанавливаются при переключениях контекста приложений, действующих в режиме малых РОН.

В одном из вариантов осуществления операционная система действует в режиме больших РОН, при этом большие РОН сохраняются и восстанавливаются при переключениях контекста приложений, действующих в режиме малых РОН.

Перечисленные, а также дополнительные задачи, признаки и выгодные варианты осуществления станут ясны из следующего далее описания.

Далее лишь в качестве примера будут описаны варианты осуществления изобретения со ссылкой на сопровождающие чертежи, на которых:

на фиг. 1А показана блок-схема, иллюстрирующая один из примеров главной компьютерной системы,

на фиг. 1Б - блок-схема, иллюстрирующая один из примеров эмулирующей главной компьютерной системы,

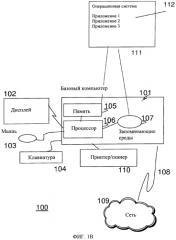

на фиг. 1В - блок-схема, иллюстрирующая один из примеров компьютерной системы,

на фиг. 2 - блок-схема, иллюстрирующая один из примеров компьютерной сети,

на фиг. 3 - блок-схема, иллюстрирующая элементы компьютерной системы,

на фиг. 4А-4В - подробные элементы компьютерной системы,

на фиг. 5А-5Е - формат машинных команд компьютерной системы,

на фиг. 6 - один из примеров большого РОН,

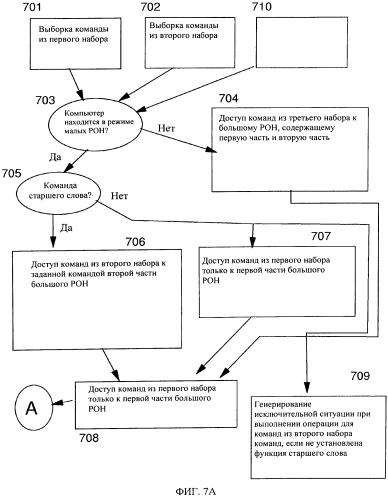

на фиг. 7А-7Б - один из примеров потока согласно варианту осуществления старшего слова, и

на фиг. 8 - один из примеров потока переключений контекста.

Варианты осуществления могут быть реализованы на практике посредством программного обеспечения (иногда называемого лицензионным внутренним кодом, аппаратно-программным обеспечением, микрокодом, милликодом, пикокодом и т.п., что во всех случаях согласуется с настоящим изобретением). Как показано на фиг. 1А, обычно процессор, также известный как ЦП (центральный процессор) 1 системы 50, получает доступ к программному коду системы программного обеспечения, в котором воплощено настоящее изобретение, посредством долговременных запоминающих сред 11, таких как ПЗУ на компакт-дисках, накопитель на магнитной ленте или накопитель на жестких дисках. Программный код системы программного обеспечения может быть воплощен в любой из разнообразных известных сред для применения с системой обработки данных, такой как дискета, накопитель на жестких дисках или ПЗУ на компакт-дисках. Код может распределяться в таких средах или может распределяться пользователям из памяти 2 компьютера или запоминающего устройства одной компьютерной системы по сети 10 другим компьютерным системам для применения пользователями таких других систем.

В качестве альтернативы, программный код может быть воплощен в памяти 2 с возможностью доступа к нему для процессора 1, использующего процессорную шину. В таком программном коде содержится операционная система, которая управляет функцией и взаимодействием различных узлов вычислительной машины и одной или нескольких прикладных программ. Обычно подкачка страниц программного кода осуществляется из плотных запоминающих сред 11 в быстродействующее запоминающее устройство 2, в котором он доступен для обработки процессором 1. Методы и способы воплощения программного кода системы программного обеспечения в памяти, в физических средах и/или распределения программного кода посредством сетей хорошо известны и не будут дополнительно рассматриваться в описании. Программный код, созданный и хранящийся в материальной среде (включая без ограничения такие машиночитаемые носители информации, как модули электронной памяти (ОЗУ), флэш-память, компакт-диски (CD), DVD, магнитную ленту и т.п.) часто именуется "компьютерным программным продуктом". Содержащая компьютерный программный продукт среда обычно может считываться устройством обработки данных предпочтительно в компьютерной системе для выполнения устройством обработки данных.

На фиг.1В проиллюстрирована характерная рабочая станция или аппаратная серверная система. В показанную на фиг.1В систему 100 входит характерная компьютерная система 101, такая как персональный компьютер, рабочая станция или сервер, включая необязательные периферийные устройства. Рабочая станция 101 имеет один или несколько процессоров 106 и шину для соединения процессора(-ов) 106 и других компонентов системы 101 и обеспечения связи между ними известными способами. Шина соединяет процессор 106 с памятью 105 и долговременным запоминающим устройством 107, которое может содержать накопитель на жестких дисках (например, включая любое из следующего: магнитный носитель, компакт-диск, цифровой многофункциональный диск и флэш-память) или, например, накопитель на магнитной ленте. В систему 101 также может входить адаптер пользовательского интерфейса, который посредством шины соединяет микропроцессор 106 с одним или несколькими устройствами сопряжения, такими как клавиатура 104, мышь 103, принтер/сканер 110 и/или другие устройства сопряжения, которыми могут являться любое пользовательское устройство сопряжения, такое как сенсорный экран, дополнительная цифровая клавиатура и т.д. Шина посредством дисплейного адаптера также соединяет дисплей 102, такой как ЖК-дисплей или монитор с микропроцессором 106.

Система 101 может поддерживать связь с другими компьютерами или компьютерными сетями посредством сетевого адаптера, способного поддерживать связь 108 с сетью 109. Примерами сетевых адаптеров являются каналы связи, кольцевая сеть с эстафетным доступом, сеть Ethernet или модемы. В качестве альтернативы, рабочая станция 101 может поддерживать связь с использованием беспроводного интерфейса, такого как карта CDPD (сотовой системы передачи пакетов цифровых данных). Рабочая станция 101 может быть связана с другими такими компьютерами в локальной вычислительной сети (ЛВС) или глобальной вычислительной сети (ГВС), или рабочей станцией 101 может являться клиент, связанный отношениями клиент-сервер с другим компьютером и т.д. Все эти конфигурации, а также соответствующее коммуникационное оборудование и программное обеспечение известны из техники.

На фиг.2 проиллюстрирована сеть 200 обработки данных, в которой может быть реализован на практике один из вариантов осуществления. В сеть 200 обработки данных может входить множество отдельных сетей, таких как беспроводная сеть и проводная сеть, в каждую из которых может входить множество отдельных рабочих станций 101, 201, 202, 203, 204. Кроме того, как известно специалистам в данной области техники, в нее может входить одна или несколько ЛВС, в которую может входить множество интеллектуальных рабочих станций, связанных с главным процессором.

Как также показано на фиг.2, в сети также могут входить мэйнфреймы или серверы, такие как шлюз (клиент-сервер 206) или сервер приложений (удаленный сервер 208, который может осуществлять доступ к хранилищу данных, а также может быть доступен непосредственно с рабочей станции 205). Шлюз 206 служит точкой входа в каждую сеть 207. Шлюз необходим при подсоединении одного сетевого протокола к другому. Шлюз 206 предпочтительно может быть связан с другой сетью (например, сетью Интернет 207) линией связи. Шлюз 206 также может быть непосредственно связан с одной или несколькими рабочими станциями 101, 201, 202, 203, 204 с использованием линии связи. Шлюз может быть реализован с использованием сервера IBM eServer™ zSeries® z10™ производства IBM Corp.

Доступ к программному коду системы программного обеспечения обычно осуществляет процессор 106 системы 101 посредством долговременных запоминающих сред 107, таких как ПЗУ на компакт-дисках, или накопитель на жестких дисках. Программный код системы программного обеспечения может быть воплощен в любой из разнообразных известных сред для применения с системой обработки данных, такой как дискета, накопитель на жестких дисках или ПЗУ на компакт-дисках. Код может распределяться в таких средах или может распределяться пользователям 210, 211 из памяти компьютера или запоминающего устройства одной компьютерной системы по сети другим компьютерным системам для применения пользователями таких других систем.

В качестве альтернативы, программный код 111 может быть воплощен в памяти 105 с возможностью доступа к нему для процессора 106 с использованием процессорной шины. В таком программном коде реализована операционная система, которая управляет функцией и взаимодействием различных узлов вычислительной машины и одной или нескольких прикладных программ 112. Обычно подкачка страниц программного кода осуществляется из плотных запоминающих сред 107 в быстродействующее запоминающее устройство 105, в котором он доступен для обработки процессором 106. Методы и способы воплощения программного кода системы программного обеспечения в памяти, в физических средах и/или распределения программного кода посредством сетей хорошо известны и не будут дополнительно рассматриваться в описании. Программный код, созданный и хранящийся в материальной среде (включая без ограничения модули электронной памяти (ОЗУ), флэш-память, компакт-диски, цифровые многофункциональные диски, магнитную ленту и т.п.) часто именуется "компьютерным программным продуктом". Содержащая компьютерный программный продукт среда обычно может считываться устройством обработки данных предпочтительно в компьютерной системе для выполнения устройством обработки данных.

Кэш, который является наиболее легкодоступным для процессора (обычно более быстродействующим и менее объемным, чем другие кэши процессора), представляет собой кэш низшего уровня (L1 или уровня 1), а основное запоминающее устройство (основная память) представляет собой кэш высшего уровня (L3 в случае 3 уровней). Кэш низшего уровня часто поделен кэш команд (I-кэш), в котором хранятся машинные команды для выполнения, и кэш данных (D-кэш), в котором хранятся операнды, хранимые в памяти.

На фиг.3 проиллюстрирован один из примеров осуществления процессора 106. Обычно с целью помещения в буфер блоков памяти и повышения производительности процессора используется один или несколько уровней кэша 303. Кэш 303 представляет собой высокоскоростной буфер, в котором в строках данных кэша хранятся данные в памяти, которые вероятно будут использоваться. Типичные строки данных кэша содержат 64, 128 или 256 байтов данных в памяти. Для кэширования команд и для кэширования данных часто используются раздельные кэши. Согласованность кэшей (синхронизация копий строк в памяти и в кэшах) часто обеспечивается различными алгоритмами слежения ("snoop"), хорошо известными из техники. Основное запоминающее устройство 105 процессорной системы часто называют кэшем. В процессорной системе, имеющей 4 уровня кэша 303, основное запоминающее устройство 105 иногда называют кэшем уровня 5 (L5), поскольку оно обычно является более быстродействующими и представляет собой лишь часть энергонезависимого запоминающего устройство (ЗУПД, ЗУ на ленте и т.д.), которое доступно для компьютерной системы. Основное запоминающее устройство 105 "кэширует" страницы данных, которые подкачиваются в основное запоминающее устройство 105 и откачиваются из него операционной системой.

Программный счетчик (счетчик команд) 311 отслеживает адрес текущей команды для выполнения. Счетчиком команд в процессоре на основе z/Architecture является 64-разрядным, при этом он может быть усечен до 31 или 24 разрядов с целью поддержки ранее существовавших ограничений адресации. Поскольку счетчик команд обычно воплощен в слове состояния программы (PSW) компьютера, оно сохраняется при переключении контекста.

Соответственно, выполняемая программа с показанием счетчика команд может прерываться, например, операционной системой (при переключении контекста из программной среды в среду операционной системы). PSW программы поддерживает показание счетчика команд, пока программа неактивна, а во время выполнения операционной системы используется счетчик команд (в PSW) операционной системы. Обычно показание счетчика команд приращивается на величину, равную числу байтов текущей команды. RISC-команды (на основе вычислений с сокращенным набором команд) обычно имеют фиксированную длину, тогда как CISC-команды (на основе вычислений с полным набором команд) обычно имеют переменную длину. Команды, используемые в системе IBM z/Architecture, являются CISC-командами, имеющими длину 2, 4 или 6 байтов. Показание счетчика 311 команд изменяется, например, в результате операции переключения контекста или операции выбранного перехода согласно команде перехода. При операции переключения контекста в слове состояния программы (PSW) сохраняется текущее показание счетчика команд вместе с другой информацией о состоянии выполняемой программы (такой как коды условий), и загружается новое показание счетчика команд, указывающее команду нового программного модуля для выполнения. Операция выбранного перехода выполняется, чтобы позволить программе принимать решения, или чтобы выполнять программный цикл путем загрузки в счетчик 311 команд результата команды перехода.

Обычно для выборки команд от имени процессора 106 применяется блок 305 выборки команд. Блок выборки осуществляет выборку "очередных последовательных команд", целевых команд из команд выбранного перехода или первых команд программы, следующей за переключением контекста. В современных блоках выборки команд часто применяют методы выборки с целью предварительной выборки команд по предположению, исходя из вероятности использования команд, предварительная выборка которых была осуществлена. Например, блок выборки может осуществлять выборку 16 байтов команды, содержащих очередную последовательную команду, и дополнительных байтов следующих далее команд.

Затем вызванные команды выполняются процессором 106. В одном из вариантов осуществления вызванная команда(-ы) передаются блоку 306 диспетчеризации блока выборки. Блок диспетчеризации декодирует команду(-ы) и пересылает информацию о декодированной команде(-ах) соответствующим блокам 307, 308, 310. Блок 307 выполнения обычно принимает информацию о декодированных арифметических командах от блока 305 выборки команд и выполняет арифметические операции с операндами в соответствии с содержащимся в команде кодом операции. Операнды предоставляются блоку 307 выполнения предпочтительно из памяти 105, структурированных регистров 309 или из непосредственного поля выполняемой команды. Сохраненные результаты выполнения хранятся в памяти 105, регистрах 309 или в другом машинном аппаратном обеспечении (таком как управляющие регистры, регистры PSW и т.п.).

Процессор 106 обычно имеет один или несколько блоков 307, 308, 310, выполнения функции команды. Как показано на фиг.4А, блок 307 выполнения посредством интерфейсной логической схемы 407 может поддерживать связь со структурированными регистрами 309 общего назначения, блоком 306 декодирования/диспетчеризации, блоком 310 загрузки/сохранения и другими процессорными блоками 401. В блоке 307 выполнения может применяться несколько регистровых схем 403, 404, 405 для хранения информации, с которой будет работать арифметическое логическое устройство (АЛУ) 402. АЛУ выполняет арифметические операции, такие как сложение, вычитание, умножение и деление, а также логические функции, такие как И, ИЛИ и исключающее ИЛИ, поворот и смещение. АЛУ предпочтительно поддерживает зависящие от конструкции специализированные операции. В других схемах могут обеспечиваться другие структурированные средства 408, включающие, например, коды условия и логическую схему поддержки восстановления. Обычно результат операции АЛУ хранится в схеме 406 выходного регистра, из которой он может пересылаться целому ряду других функций обработки. Хотя существует множество конструкций процессоров, настоящее описание имеет целью лишь обеспечить понимание одного из вариантов осуществления.

Например, команда сложения выполняется блоком 307 выполнения, обладающим арифметическими и логическими функциональными возможностями, а, например, команда с плавающей точкой выполняется блоком вычислений с плавающей точкой, обладающим специализированными возможностями работы с плавающей точкой. Блок выполнения предпочтительно работает с указанными командой операндами путем выполнения заданной кодом операции функции применительно к операндам. Например, команда сложения может выполняться блоком 307 выполнения применительно к операндам, обнаруженным в двух регистрах 309, указанных в регистровых полях команды.

Блок 307 выполнения выполняет арифметическое сложение двух операндов и сохраняет результат в третьем операнде, которым может являться третий регистр или один из двух исходных регистров. Блок выполнения предпочтительно использует арифметическое логическое устройство (АЛУ) 402, способное выполнять ряд логических функций, таких как смещение, поворот. И, ИЛИ и исключающее ИЛИ, а также ряд алгебраических функций, включая любые из следующих функций: сложение, вычитание, умножение, деление. Некоторые АЛУ 402 рассчитаны на скалярные операции, а некоторые - на операции с плавающей точкой. В зависимости от архитектуры данные могут иметь обратный порядок следования байтов (когда наименьший значимый байт соответствует старшему байтовому адресу) или прямой порядок следования байтов (когда наименьший значимый байт соответствует младшему байтовому адресу). В системе IBM z/Architecture используется обратный порядок следования байтов. В зависимости от архитектуры поля чисел со знаком могут быть представлены в виде прямого кода, дополнения до единицы или дополнения до двух. Число в форме дополнения до двух выгодно в том смысле, что АЛУ не требуется поддерживать возможность вычитания, поскольку при отрицательной или положительной величине дополнения до двух в АЛУ требуется только сложение. Числа обычно описаны в сокращенном виде, в котором 12-разрядное поле определяет адрес блока из 4096 байтов и обычно описано, например, в виде 4-килобайтового блока.

Трехрежимная адресация

Трехрежимная адресация означает способность переключения между режимами 24-разрядной, 31-разрядной и 64-разрядной адресации. Это переключение может осуществляться посредством:

старых команд перехода с сохранением и установки режима (BRANCH AND SAVE AND SET MODE) и перехода и установки режима (BRANCH AND SET MODE). Обе эти команды устанавливают режим 64-разрядной адресации, если разряд 63 регистра R2 общего назначения равен единице. Если разряд 63 равен нулю, команды устанавливают режим 24-разрядной или 31-разрядной адресации, если разряд 32 регистра равен нулю или единице, соответственно.

Новой команды установки режима адресации (SET ADDRESSING MODE) (SAM24, SAM31 и SAM64). Команда устанавливает режим 24-разрядной, 31-разрядной, или 64-разрядной адресации, заданный кодом операции кодом операции.

Трехрежимные команды

Влияние трехрежимной адресации на общие команды проявляется только в том, каким образом обрабатываются логические адреса запоминающих устройств, за исключением следующих случаев.

Команды перехода и возврата (BRANCH AND LINK), перехода с сохранением (BRANCH AND SAVE), перехода с сохранением и установки режима и относительного перехода с сохранением (BRANCH RELATIVE AND SAVE) помещают информацию в разряды 32-39 регистра R1 общего назначения как в ESA/390 в режиме 24-разрядной или 31-разрядной адресации или помещают разряды адреса в соответствующие разряды в режиме 64-разрядной адресации. Новая команда длительного относительного перехода с сохранением (BRANCH RELATIVE AND SAVE LONG) действует таким же образом.

В режиме 64-разрядной адресации команды перехода с сохранением и установки режима и перехода и установки режима помещают единицу в разряд 63 регистра R1 общего назначения. В режиме 24-разрядной или 31-разрядной адресации команда перехода с сохранение