Радиоприемное устройство с непрерывной автоматической регулировкой восприимчивости

Иллюстрации

Показать всеИзобретение относится к технике приема и обработки радиосигналов и может быть использовано для создания перспективных радиосредств с программируемой архитектурой с цифровой обработкой сигналов в условиях воздействия блокирующих сигналов с динамически изменяющимся уровнем и априорной неопределенностью параметров для обеспечения устойчивой радиосвязи в сложной помеховой обстановке. Технический результат - уменьшение вероятности неприема сигнала в условиях воздействия на радиоприемное устройство блокирующих помех с динамически меняющимся уровнем. Устройство содержит блок бланкирования импульсных помех (1), N полосовых фильтров (8.1-8.N), два сумматора (9, 16), аналого-цифровой преобразователь (10), два блока памяти (12, 15), блок задержки (18), два блока умножения (13, 19), блок быстрого преобразования Фурье (14), блок вычисления обратной величины (17), блок бланкирования узкополосной помехи (20); коррелятор (21), блок формирования опорного сигнала (22), пороговый блок (23) и блок регулировки усиления (2), включающий управляемый аттенюатор (3), амплитудный детектор (4), два компаратора (5, 6), счетчик (7) и блок задержки (11). 6 ил.

Реферат

Изобретение относится к технике приема и обработки радиосигналов и может быть использовано для создания перспективных радиосредств с программируемой архитектурой с цифровой обработкой сигналов в условиях воздействия блокирующих сигналов с динамически изменяющимся уровнем и априорной неопределенностью параметров для обеспечения устойчивой радиосвязи в сложной помеховой обстановке.

Такие приемники описаны, например, в книгах «Undersampling techniques simplify digital radio». Electronic Design, Vol.39, May 23, 1991, No. 10, pp. 67, 68, 70, 73-75, 78 авторов Richard Groshong и Stephen Ruscar, и «Software denned radio: enabling technologies», John Wiley & Sons, Chichester, UK, 2002. - p.p. 440 автора W. Tuttlebee, Ed.

Сущность таких устройств заключается в поддержании максимально возможного уровня сигнала на входе аналого-цифрового преобразователя (АЦП), не приводящего к ограничению путем перераспределения усиления аналого-цифрового тракта (АЦТ) между аналоговым и цифровым доменами при сохранении неизменным общего коэффициента передачи. В существующих аналогах процесс автоматической регулировки восприимчивости (АРВ) реализуется поблочно, вследствие необходимости накопления буфера отсчетов сигнала для вычисления быстрого преобразования Фурье (БПФ), что может привести к искажению сигнала по причине переполнения АЦП в условиях воздействия блокирующих сигналов с динамически изменяющимся уровнем.

Наиболее близким к заявляемому является устройство, описанное в авторском свидетельстве №1637026. Устройство корреляционной обработки широкополосных сигналов. - Маковий В.А, Каткова Т.П. МКИ Н04В 1/10, H04L 7/02 - 4 с. Регистрация 23.08.1988 - Опубл. 23.03.91 г., Бюл. №11, принятое за прототип [1].

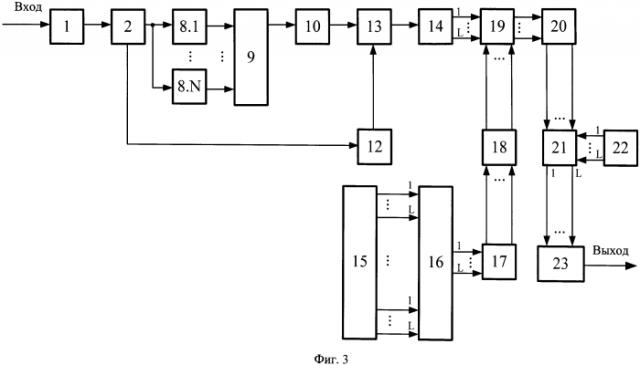

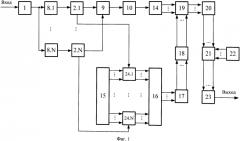

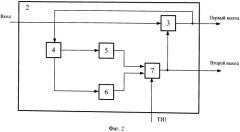

На фиг. 1 представлена функциональная схема устройства-прототипа; на фиг. 2 - функциональная схема блока регулировки усиления, где обозначено:

1 - блок бланкирования импульсных помех (БИЛ);

2.1-2.N - с первого по N-й блок регулировки усиления (РУ);

3 - управляемый аттенюатор;

4 - амплитудный детектор;

5 - первый компаратор;

6 - второй компаратор;

7 - счетчик;

8.1-8.N - с первого по N-й полосовые фильтры;

9 - первый сумматор;

10 - аналого-цифровой преобразователь (АЦП);

14 - блок быстрого преобразования Фурье (БПФ);

15 - блок памяти;

16 - второй сумматор;

17 - блок вычисления обратной величины (ВОВ);

18 - блок задержки;

19 - блок умножения;

20 - блок бланкирования узкополосной помехи (БУП);

21 - коррелятор;

22 - блок формирования опорного сигнала (ФОС);

23 - пороговый блок;

24.1-24.N - с первого по N-й умножитель.

Устройство-прототип содержит блок БИЛ 1, вход которого является входом устройства, а выход которого соединен с входами N полосовых фильтров 8.1…8.N, выходы которых соединены с соответствующими входами N идентичных блоков РУ 2.1…2.N. Вход каждого из блоков РУ 2.1…2.N соединен с сигнальным входом управляемого аттенюатора 3, выход которого является первым выходом блока РУ и соединен с соответствующим входом первого сумматора 9, а также соединен с входом амплитудного детектора 4, выходы которого соединены с соответствующими входами первого 5 и второго 6 компараторов, выходы которых соединены с соответствующими входами счетчика 7, тактовый вход которого является тактовым входом блока РУ 2, а выход счетчика 7 соединен с управляющим входом управляемого аттенюатора 3 и является вторым выходом блока РУ 2.1…2.N, который соединен с входом соответствующего умножителя 24.1…24.N. Первый сумматор 9 последовательно соединен с АЦП 10 и блоком БПФ 14, группа выходов которого соединена с первой группой входов блока умножения 19. Блок памяти 15, имеющий N групп выходов, соединен с группами входов соответствующих умножителей 24.1…24.N, группы выходов которых соединены с соответствующими N группами входов второго сумматора 16, который последовательно соединен с блоком ВОВ 17 и блоком задержки 18. Группа выходов блока задержки 18 соединена со второй группой входов блока умножения 19, который соединен последовательно с блоком БУП 20, и коррелятором 21, вторая группа входов которого соединена с группой выходов блока ФОС 22. Коррелятор 21 последовательно соединен с пороговым блоком 23, выход которого является информационным выходом радиоприемного устройства.

В блоках 10, 14-23 также имеются стандартные тактовые входы, на которые подаются сигналы, обеспечивающие синхронизацию работы устройства в целом.

Устройство-прототип работает следующим образом. Входной радиочастотный сигнал, представляющий собой аддитивную смесь сигнала, флуктуационных, импульсных и сосредоточенных помех, поступает на вход радиоприемного устройства и проходит через блок 1 БИП и поступает одновременно на N полосовых фильтров 8.1-8.N, которые разбивают диапазон частот входного сигнала на N поддиапазонов. Сигнал с выхода полосовых фильтров поступает на входы N блоков РУ 2.1-2.N (фиг. 2).

Коэффициент передачи каждого блока РУ определяется цифровым кодом, поступающим с выхода счетчика 7 на управляющий вход управляемого аттенюатора 3. С выхода управляемого аттенюатора 3 сигнал последовательно поступает на амплитудный детектор 4, на два компаратора 5 и 6, которые сравнивают величину входного сигнала с заранее установленными максимальным и минимальным значениями. Если амплитуда выходного сигнала амплитудного детектора 4 выше максимального значения, то с выхода первого компаратора 5 на первый разрешающий вход счетчика 7 поступает сигнал, разрешающий уменьшение коэффициента передачи, пока выходной сигнал не станет меньше установленного значения. Если амплитуда выходного сигнала детектора 4 ниже минимального значения, то с выхода второго компаратора 6 на второй разрешающий вход счетчика 7 поступает сигнал, разрешающий увеличение коэффициента передачи, пока выходной сигнал не станет выше установленного минимального значения. При этом на тактовый вход счетчика 7 поступают тактовые импульсы (ТИ1).

Блоки РУ 2.1-2.N устанавливают коэффициенты усиления таким образом, чтобы напряжение на их выходах находилось в заданных, заранее установленных пределах, одинаковых для всех блоков РУ. Сигналы управления, определяющие значения установившегося коэффициента усиления, поступают на первые входы соответствующих блоков умножения 24.1-24.N.

Выходные сигналы блоков РУ 2.1-2.N поступают на соответствующие входы первого сумматора 9. Результат суммирования через АЦП 10 поступает на вход блока 14 БПФ, в котором отсчеты сигнала преобразуются из временной в частотную область.

Выход блока 14 БПФ представляет собой группу величин спектральных составляющих сигнала, поступающих параллельно на первую группу входов блока 19 умножения. В блоке 19 умножения осуществляется умножение величин спектральных составляющих на соответствующие отсчеты обратного комплексного коэффициента передачи полосовых фильтров 8.1-8.N с учетом коэффициентов усиления в блоках РУ 2.1-2.N. Число отсчетов обратного комплексного коэффициента передачи совпадает с числом спектральных составляющих на выходе блока 14 БПФ. Формирование отсчетов обратного суммарного коэффициента передачи полосовых фильтров и блоков РУ происходит следующим образом.

В блоке 15 памяти находятся отсчеты комплексного коэффициента передачи каждого из N полосовых фильтров, которые параллельно поступают на вторые входы соответствующих блоков 24.1-24.N умножителей, где происходит умножение отсчетов коэффициентов передачи каждого фильтра на соответствующий коэффициент усиления в блоке РУ. Отсчеты с групп выходов блоков умножения 24.1-24.N поступают на соответствующие группы входов второго блока суммирования 16, в котором одновременно складываются соответствующие отсчеты коэффициентов передачи различных полосовых фильтров.

В блоке 17 BOB формируются отсчеты обратного суммарного коэффициента передачи полосовых фильтров 8.1-8.N с учетом коэффициентов усиления в блоках РУ 2.1-2.N. Отсчеты обратного суммарного коэффициента передачи через блок 18 задержки поступают на вторую группу входов блока 19 умножения.

Восстановленный таким образом сигнал поступает на вход блока 20 БУП, где подавляются спектральные составляющие этих помех. Сигнал с выхода блока 20 БУП поступает на первую группу входов коррелятора 21, на вторую группу входов которого поступает сигнал с выхода блока 22 ФОС.

Коррелятор 21 представляет собой последовательное соединение блока умножения, аналогичного блоку 19, и блока обратного быстрого преобразования Фурье, реализованного аналогично блоку 14 БПФ.

В корреляторе 21 определяется взаимно корреляционная функция опорного сигнала и сигнала с выхода блока БУП. Выборки с выхода коррелятора поступают на пороговый блок 23. Превышение порога означает обнаружение сигнала. Информация об обнаружении сигнала поступает на выход радиоприемного устройства.

Проблема обеспечения приема в условиях сложной помеховой обстановки при различных уровнях входного сигнала особенно остро стоит в приемниках с цифровой обработкой [2].

Недостатком устройства-прототипа является необходимость буферизации отсчетов сигнала для вычисления БПФ, вследствие чего частота f1 тактового сигнала ТИ1, которым тактируются блоки регулировки усиления 2.1-2.N и блок 19 умножения, должна быть меньше в L раз (где L - количество отсчетов буферизации), чем основная частота тактирования fосн блока АЦП 10, что может привести к искажению сигнала по причине переполнения АЦП в условиях воздействия блокирующих сигналов с динамически изменяющимся уровнем.

Задачей изобретения является реализация непрерывного, поточного процесса АРВ без буферизации, с единым тактовым сигналом частотой fосн для блока регулировки усиления и АЦП, для предотвращения переполнения АЦП помехой с быстро меняющимся уровнем при сохранении всех положительных свойств устройства-прототипа.

Достигаемый технический результат - уменьшение возможности искажения принимаемого сигнала блокирующими помехами с динамически изменяющимся уровнем и априорной неопределенностью параметров.

Для решения поставленной задачи в радиоприемное устройство, содержащее блок бланкирования импульсных помех (БИЛ), вход которого является входом устройства, N полосовых фильтров, блок регулировки усиления (РУ), первый блок памяти, последовательно соединенные первый сумматор и аналого-цифровой преобразователь (АЦП), который тактируется тактовым сигналом частотой fосн; последовательно соединенные блок быстрого преобразования Фурье (БПФ), первый блок умножения, блок бланкирования узкополосной помехи (БУП), коррелятор и пороговый блок, выход которого является информационным выходом устройства; последовательно соединенные второй сумматор, блок вычисления обратной величины (ВОВ) и первый блок задержки, группа выходов которого соединена со второй группой входов первого блока умножения, блок формирования опорного сигнала (ФОС), группа выходов которого соединена со второй группой входов коррелятора, причем блок РУ содержит управляемый аттенюатор (УА), выход которого, являющийся первым выходом блока РУ, соединен с входом амплитудного детектора, выходы которого соединены с входами соответствующих первого и второго компараторов, выходы которых соединены с соответствующими входами счетчика, выход которого соединен с управляющим входом УА, а тактовый вход счетчика является тактовым входом блока РУ; при этом первый блок памяти, второй сумматор, блок ВОВ, первый блок задержки, первый блок умножения, блок БУП, коррелятор, блок ФОС и пороговый блок тактируются тактовым сигналом с частотой f1=fосн/L, где L - количество отсчетов буферизации, согласно изобретению введены второй блок памяти и второй блок умножения, а в состав блока РУ дополнительно введен второй блок задержки, вход которого соединен с выходом счетчика, тактовый вход второго блока задержки соединен с тактовым входом счетчика, а выход второго блока задержки является вторым выходом блока РУ и соединен с управляющим входом второго блока памяти, выход которого соединен со вторым входом второго блока умножения, вход которого соединен с выходом АЦП, а выход второго блока умножения соединен с входом блока БПФ; выход блока БИЛ соединен с входом блока РУ, первый выход которого соединен с объединенными входами N полосовых фильтров, выходы которых соединены соответственно с N входами первого сумматора; N групп выходов первого блока памяти соединены соответственно с N группами входов второго сумматора; при этом блок РУ, второй блок памяти, второй блок умножения и блок БПФ тактируются тактовым сигналом частотой fосн.

Это позволяет непрерывно осуществлять АРВ без предварительной буферизации путем применения одного и того же тактового сигнала для АЦП и блока РУ, а последующие преобразования в частотной области, требующие поблочной обработки с меньшей частотой тактового сигнала, выполнять уже после компенсации уровня сигнала.

Функциональная схема заявляемого устройства представлена на фиг. 3, где обозначено:

1 - блок бланкирования импульсных помех (БИЛ);

2 - блок регулировки усиления (РУ);

3 - управляемый аттенюатор;

4 - амплитудный детектор;

5 - первый компаратор;

6 - второй компаратор;

7 - счетчик;

8.1-8.N - с первого по N-й полосовые фильтры;

9 - первый сумматор;

10 - аналого-цифровой преобразователь (АЦП);

11 - второй блок задержки;

12 - второй блок памяти;

13 - второй блок умножения;

14 - блок быстрого преобразования Фурье (БПФ);

15 - первый блок памяти;

16 - второй сумматор;

17 - блок вычисления обратной величины (ВОВ);

18 - первый блок задержки;

19 - первый блок умножения;

20 - блок бланкирования узкополосной помехи (БУП);

21 - коррелятор;

22 - блок формирования опорного сигнала (ФОС);

23 - пороговый блок.

Заявляемое устройство содержит последовательно соединенные блок бланкирования импульсных помех (БИЛ) 1, вход которого является входом устройства, и блок регулировки усиления (РУ) 2, первый выход которого соединен с объединенными входами N полосовых фильтров 8.1…8.N, выходы которых соединены с соответствующими входами первого сумматора 9, выход которого через аналого-цифровой преобразователь (АЦП) 10 соединен с первым входом второго умножителя 13.

Блок РУ 2 содержит управляемый аттенюатор (УА) 3, выход которого, являющийся первым выходом блока РУ 2, соединен с входом амплитудного детектора 4, первый и второй выходы которого соединены с входами соответствующих первого 5 и второго 6 компараторов, выходы которых соединены с соответствующими входами счетчика 7, тактовый вход которого является тактовым входом блока РУ 2 и соединен с тактовым входом второго блока задержки 11. Выход счетчика 7 соединен с управляющим входом УА 3 и входом второго блока задержки 11, выход которого является вторым выходом блока РУ 2, который соединен с управляющим входом второго блока памяти 12, выход которого соединен со вторым входом второго блока умножения 13, выход которого соединен с входом блока быстрого преобразования Фурье (БПФ) 14, группа выходов которого соединена с первой группой входов первого блока умножения 19.

Первый блок памяти 15 имеет N групп выходов, соединеных с соответствующими N группами входов второго сумматора 16, который последовательно соединен с блоком вычисления обратной величины (ВОВ) 17 и первым блоком задержки 18, группа выходов которого соединена со второй группой входов первого блока умножения 19, который соединен последовательно с блоком бланкирования узкополосной помехи (БУП) 20 и коррелятором 21, вторая группа входов которого соединена с группой выходов блока формирования опорного сигнала (ФОС) 22, а группа выходов коррелятора 21 соединена с группой входов порогового блока 23, выход которого является информационным выходом устройства.

В блоках 10, 12-23 также имеются стандартные тактовые входы (на чертеже не показано), на которые подаются сигналы, обеспечивающие синхронизацию работы устройства в целом. Блоки 2, 10, 12, 13 и 14 тактируются основным тактовым сигналом частотой fосн, а блоки 15-23 тактируются тактовым сигналом с частотой f1=fосн/L, где L - количество отсчетов буферизации.

Заявляемое устройство работает следующим образом.

Входной радиочастотный сигнал, представляющий собой аддитивную смесь сигнала, флуктуационных, импульсных и сосредоточенных помех, поступает на вход радиоприемного устройства и проходит через блок 1 БИЛ, в котором осуществляется бланкирование импульсных помех, результат которого подается на вход блока РУ 2, который устанавливает коэффициент усиления таким образом, чтобы напряжение на его выходе находилось в заданных, заранее установленных пределах.

Коэффициент передачи блока РУ 2 определяется цифровым кодом, формируемым на выходе счетчика 7, который подается на управляющий вход УА 3. Также с выхода счетчика 7 цифровой код подается на второй блок задержки 11, в котором он задерживается на количество тактов, эквивалентное задержке сигнала на распространение до второго блока умножения 13. Со второго выхода блока 2 РУ, цифровой код поступает на управляющий адресный вход второго блока памяти 12, в котором хранятся соответствующие каждому цифровому коду коэффициенты для цифровой компенсации сигнала. Соответствующий цифровому коду компенсирующий коэффициент из второго блока памяти 12 поступает на второй вход второго блока умножения 13.

С выхода управляемого аттенюатора 3 сигнал последовательно поступает на амплитудный детектор 4, а затем на первый 5 и второй 6 компараторы, которые сравнивают величину входного сигнала с заранее установленными максимальным и минимальным значениями. Если амплитуда выходного сигнала амплитудного детектора 4 выше максимального значения, то с выхода первого компаратора 5 на первый разрешающий вход счетчика 7 поступает сигнал, разрешающий уменьшение коэффициента передачи, пока выходной сигнал не станет меньше установленного значения. Если амплитуда выходного сигнала амплитудного детектора 4 ниже минимального значения, то с выхода второго компаратора 6 на второй разрешающий вход счетчика 7 поступает сигнал, разрешающий увеличение коэффициента передачи, пока выходной сигнал не станет выше установленного минимального значения. При этом на тактовый вход счетчика 7 поступают тактовые импульсы (ТИ) частотой fосн.

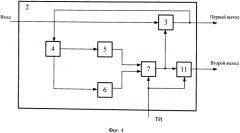

Сигнал с первого информационного выхода блока РУ 2 поступает одновременно на N полосовых фильтров 8.1-8.N, которые разбивают диапазон частот входного сигнала на N поддиапазонов. Сигналы, полученные после фильтрации, с выходов N полосовых фильтров 8.1-8.N поступают на соответствующие входы первого сумматора 9 (фиг. 4). Результаты суммирования через АЦП 10 поступают на первый вход второго блока умножения 13. После перемножения сигнала с компенсирующим коэффициентом из второго блока памяти 12 результат поступает в блок БПФ 14, в котором отсчеты сигнала преобразуются из временной в частотную область.

Группа выходов блока 14 БПФ представляет собой группу L отсчетов спектральных составляющих сигнала, поступающих параллельно на первую группу входов второго блока умножения 19, в котором осуществляется умножение величин спектральных составляющих на соответствующие отсчеты обратного комплексного коэффициента передачи полосовых фильтров 8.1-8.N. При этом число отсчетов обратного комплексного коэффициента передачи полосовых фильтров совпадает с числом спектральных составляющих L на выходе блока 14 БПФ.

Формирование отсчетов обратного коэффициента передачи полосовых фильтров происходит следующим образом. В блоке 15 памяти находятся отсчеты комплексного коэффициента передачи каждого из N полосовых фильтров, которые параллельно поступают на соответствующие группы входов второго блока суммирования 16, в котором одновременно складываются соответствующие отсчеты комплексных коэффициентов передачи различных полосовых фильтров.

В блоке 17 BOB формируются отсчеты обратного коэффициента передачи полосовых фильтров 8.1-8.N, которые через первый блок задержки 18 поступают на вторую группу входов первого блока умножения 19.

Полученные в результате перемножения отсчеты сигналов спектральных составляющих сигналов поступают в блок 20 БУП, где подавляются спектральные составляющие помех. Далее, отсчеты сигнала с L выходов блока 20 БУП поступают на первую группу входов коррелятора 21, на вторую группу входов которого поступают отсчеты опорного сигнала с выхода блока 22 ФОС.

Коррелятор 21 содержит последовательно соединенные блок умножения, аналогичный блоку 19, и блок обратного быстрого преобразования Фурье, реализованный аналогично блоку БПФ 14.

В корреляторе 21 определяется взаимно корреляционная функция опорного сигнала и сигнала с выхода блока БУП 20. Отсчеты сигнала с L выходов коррелятора 21 подаются в пороговый блок 23. Превышение порога означает обнаружение сигнала. Информация об обнаружении сигнала поступает на выход радиоприемного устройства.

Таким образом, в соответствии с поставленной задачей, было реализовано радиоприемное устройство, в котором применяется единый тактовый сигнал для АЦП и блока РУ, а буферизация и последующая обработка в частотной области выполняются уже после восстановления сигнала, что позволяет осуществлять непрерывный процесс АРВ.

К несомненным преимуществам такой реализации устройства относится возможность непрерывной поточной автоматической регулировки восприимчивости приемника для уменьшения возможности искажения принимаемого сигнала блокирующими помехами, независимо от динамики изменения их амплитуды. Динамический диапазон, для увеличения которого в прототипе использовались N блоков РУ, также не изменится, поскольку в предлагаемом устройстве перед блоком аналого-цифрового преобразователя уровень сигнала также поддерживается в заданных пределах, а восстановление сигнала осуществляется за счет умножения в цифровом формате на обратный коэффициент передачи блока регулировки усиления.

Реализация блоков 1-10, 14-23 заявляемого устройства аналогична блокам устройства-прототипа и может быть выполнена в соответствии с монографией Пауль Хоровиц и Уинфилд Хилл «Искусство схемотехники» в 2-х томах. Москва, Мир, 1986 г., причем реализация введенных блоков 11, 12 и 13 аналогична реализации блоков 18, 15 и 19 устройства-прототипа соответственно.

Приведем доказательство эффективности работы заявляемого устройства.

Рассмотрим временные диаграммы, отражающие уровень сигнала в нескольких точках устройства-прототипа (фиг. 5) и заявляемого устройства (фиг. 6). В частности, на выходе блока БИЛ 1 (фиг. 5а, фиг. 6а), на выходе АЦП 10 (фиг. 5б, фиг. 6б) и после компенсации и обратного быстрого преобразования Фурье в блоке 21 (фиг. 5в, фиг. 6в).

По оси абсцисс на временных диаграммах отложены периоды, соответствующие частоте тактовых сигналов ТИ, применяемых для автоматической регулировки усиления. На фиг. 5 по оси абсцисс цена деления соответствует периоду тактового сигнала ТИ1 частотой f1, а на фиг. 6 - периоду тактового сигнала ТИ частотой fосн.

Пусть на вход устройства-прототипа поступает некоторый сигнал Uсиг, и в момент времени t1 появляется блокирующая помеха, что представлено на фиг. 5а. На диаграмме также отмечены моменты времени, соответствующие периодам накопления отсчетов для вычисления БПФ и одновременно тактирования блоков РУ. Таким образом, в момент времени t2 сигнал с выхода одного или нескольких фильтров превышает порог компаратора 5, и счетчик 7 увеличивает свое значение на единицу. Управляемый аттенюатор 3 изменяет коэффициент передачи, и соответствующие сигналы для компенсации ослабления поступают на умножители 24.1-24.N. Описанный процесс представлен на фиг. 5б. Далее уровень блокирующей помехи продолжает расти, и в момент времени t3 происходит переполнение АЦП 10, и интервал времени 13-14 до следующего срабатывания порога является интервалом искажения приемного сигнала (фиг. 5в), что, несомненно, является существенным недостатком устройства-прототипа.

При введении в состав приемного устройства блоков 11-13 получим, что блок РУ 2 будет тактироваться тем же сигналом, что и АЦП 10. Рассмотрим тот же пример. Пусть на вход предлагаемого устройства поступает некоторый сигнал Uсиг, и в момент времени t1 появляется блокирующая помеха, что представлено на фиг. 6а. На диаграмме также отмечены моменты времени, соответствующие периодам накопления отсчетов для вычисления БПФ, а также тактирования АЦП и блока РУ. Таким образом, в момент времени t2 сигнал превысит порог компаратора 5, и счетчик 7 увеличивает свое значение на единицу. Управляемый аттенюатор 3 изменяет коэффициент передачи, и соответствующий сигнал для компенсации ослабления поступает через блоки задержки 11 и памяти 12 на второй блок умножения 13. Описанный процесс представлен на фиг. 6б. Далее уровень блокирующей помехи продолжает расти, и на последующих тактах в моменты времени t3 и t4 управляемый аттенюатор 3 продолжает ослаблять входной сигнал (фиг. 6б), а на выходе блока 13 сигнал компенсируется, как представлено на фиг. 6в.

Таким образом, поскольку управление аттенюатором при таком построении приемного устройства осуществляется непрерывно без буферизации, принимаемый сигнал не имеет интервалов неприема сигнала, что является положительным отличительным свойством заявляемого устройства.

Для вычисления БПФ обрабатываемого сигнала накапливается буфер из L отсчетов [3], причем в заявляемом радиоприемном устройстве интервал неприема сигнала будет равен периоду дискретизации, что в L раз меньше по сравнению с прототипом, при этом увеличение динамического диапазона сохраняется за счет механизма АРВ.

Это позволяет непрерывно осуществлять АРВ путем применения единого тактового сигнала для АЦП и блока РУ, а буферизация и последующая обработка в частотной области выполняются уже после восстановления сигнала.

Литература

1. Авторское свидетельство №1637026. Устройство корреляционной обработки широкополосных сигналов. - Маковий В.А., Каткова Т.П. МКИ Н04В 1/10, H04L 7/02 - 4 с., Регистрация 23.08.1988 - Опубл. 23.03.91 г., Бюл. №11.

2. Arthur G. Stephenson, "Digitizing Multiple RF Signals Requires an Optimum Sampling Rate", Electronics, Mar. 27, 1972. - pp. 106-110.

3. Цифровая обработка сигналов: Справочник / Л.М. Гольденберг, Б.Д. Матюшкин, М.Н. Поляк. - М.: Радио и связь, 1985. С. 14-20.

Радиоприемное устройство с непрерывной автоматической регулировкой восприимчивости, содержащее блок бланкирования импульсных помех (БИП), вход которого является входом устройства, N полосовых фильтров, блок регулировки усиления (РУ), первый блок памяти, последовательно соединенные первый сумматор и аналого-цифровой преобразователь (АЦП), который тактируется тактовым сигналом частотой fосн; последовательно соединенные блок быстрого преобразования Фурье (БПФ), первый блок умножения, блок бланкирования узкополосной помехи (БУП), коррелятор и пороговый блок, выход которого является информационным выходом устройства; последовательно соединенные второй сумматор, блок вычисления обратной величины (ВОВ) и первый блок задержки, группа выходов которого соединена со второй группой входов первого блока умножения, блок формирования опорного сигнала (ФОС), группа выходов которого соединена со второй группой входов коррелятора, причем блок РУ содержит управляемый аттенюатор (УА), выход которого, являющийся первым выходом блока РУ, соединен с входом амплитудного детектора, выходы которого соединены с входами соответствующих первого и второго компараторов, выходы которых соединены с соответствующими входами счетчика, выход которого соединен с управляющим входом УА, а тактовый вход счетчика является тактовым входом блока РУ; при этом первый блок памяти, второй сумматор, блок ВОВ, первый блок задержки, первый блок умножения, блок БУП, коррелятор, блок ФОС и пороговый блок тактируются тактовым сигналом с частотой f1=fосн/L, где L - количество отсчетов буферизации, отличающиеся тем, что введены второй блок памяти и второй блок умножения, а в состав блока РУ дополнительно введен второй блок задержки, вход которого соединен с выходом счетчика, тактовый вход второго блока задержки соединен с тактовым входом счетчика, а выход второго блока задержки является вторым выходом блока РУ и соединен с управляющим входом второго блока памяти, выход которого соединен со вторым входом второго блока умножения, вход которого соединен с выходом АЦП, а выход второго блока умножения соединен с входом блока БПФ; выход блока БИП соединен с входом блока РУ, первый выход которого соединен с объединенными входами N полосовых фильтров, выходы которых соединены соответственно с N входами первого сумматора; N групп выходов первого блока памяти соединены соответственно с N группами входов второго сумматора; при этом блок РУ, второй блок памяти, второй блок умножения и блок БПФ тактируются тактовым сигналом частотой fосн.