Способ двухтактного аналого-цифрового преобразования интегрирующего типа и устройство для его осуществления

Иллюстрации

Показать всеИзобретение относится к измерительной технике. Технический результат - уменьшение относительной погрешности аналого-цифрового преобразования с двухтактным интегрированием. Способ двухтактного аналого-цифрового преобразования интегрирующего типа основан на измерении искомого временного интервала с использованием конденсатора, параллельного операционному усилителю. Отличается тем, что во втором такте измерения разрядный ток конденсатора изменяют во времени согласно выражению Ic(t)=I0(kt)p при p>0. Устройство для реализации способа включает управляемый двухвходовый ключевой элемент, операционный усилитель, конденсатор, источник тока разряда, компаратор, источник уровня сравнения, блок управления, блок кодирования, выход которого является выходом аналого-цифрового преобразователя. Отличается тем, что источник тока разряда реализует функцию изменения тока разряда на входе операционного усилителя в соответствии с выражением Ic(t)=I0(kt)p, p>0, при этом источник тока разряда имеет управляющий вход, который соединен с выходом блока включения/выключения источника тока разряда, вход блока включения/выключения источника тока разряда соединен с одним из выходов блока управления. 2 н.п. ф-лы, 4 ил.

Реферат

Группа изобретений относится к измерительной и вычислительной технике, а именно к аналого-цифровому преобразованию (АЦП) с интегрированием, и может быть использована в информационно-измерительных системах повышенной точности.

Наиболее близким к предложенному является способ двухтактного аналого-цифрового преобразования интегрирующего типа [Аналого-цифровое преобразование, ред. Уолт Кестер, перевод с английского под ред. Е.Б. Володина, М: Техносфера, 2007, стр. 270-271, рис. 3.114], который в русскоязычном переводе назван «АЦП двойного наклона». В этом способе преобразование измеряемой электрической величины осуществляют временными циклами, каждый из которых разделен на два временных интервала или два такта. Физические процессы, происходящие при двухтактном аналого-цифровом преобразовании интегрирующего типа, хорошо известны и описаны, например, в книге [Г.И. Волович, Схемотехника аналоговых и аналого-цифровых электронных устройств, М: издательский дом «Додека-XXI», 2005, стр. 446-448]. За время первого такта входной ток интегрируют по времени в течение заданного интервала времени или первого такта с помощью интегратора в виде последовательно соединенных резистора и операционного усилителя, с которым параллельно соединен конденсатор. При этом через резистор и конденсатор протекает ток, что обеспечивает накопление на конденсаторе электрического заряда. В течение следующего интервала времени - длительности второго такта - к резистору интегратора вместо входного сигнала подводится постоянное опорное напряжение, в результате чего в интеграторе формируется постоянный ток разряда конденсатора, имеющий направление, противоположное направлению входного зарядного тока. В результате заряд на конденсаторе, накопленный к концу первого такта, начинает уменьшаться и на выходе операционного усилителя образуется напряжение, изменяющееся во времени в соответствии со следующим выражением:

где

U0 - напряжение на выходе операционного усилителя в начале второго такта преобразования [V],

Ic=const - ток разряда конденсатора, [A],

C - емкость конденсатора, [F],

t - текущее время, [sec], t=0 в начале второго такта преобразования.

Таким образом, к концу первого такта преобразования на выходе операционного усилителя образуется напряжение U0 пропорциональное входному току Iвх, а во втором такте из-за постоянства тока разряда конденсатора Ic происходит уменьшение напряжения на выходе операционного усилителя Uout(t) с постоянной скоростью. Разряд конденсатора во втором такте преобразования производится до момента достижения выходным напряжением операционного усилителя Uout(t) некоторого заранее выбранного постоянного напряжения, называемого уровнем сравнения, в качестве которого может быть выбрано нулевое напряжение. При этом формируется временной интервал tm, начало которого определяется моментом начала второго такта, а окончание - моментом достижения выходным напряжением операционного усилителя уровня сравнения. Величина временного интервала tm из-за постоянства тока разряда конденсатора Ic пропорциональна напряжению U0 (фиг. 1). Временной интервал tm измеряется путем подсчета количества импульсов, формируемых высокочастотным импульсным генератором за этот временной интервал. Цифровой код, образующийся на выходе счетчика к моменту окончания временного интервала tm и есть результат преобразования входного тока Iвх в цифровой код в каждом цикле преобразования. В прототипе цифровые коды, получающиеся в результате преобразования, в каждом цикле преобразования пропорциональны входному току Iвх.

В соответствии с выражением (1) временной интервал tm определяется следующим образом:

где

C - емкость конденсатора, [F];

Ic - ток разряда конденсатора, [A];

U0 - напряжение на выходе операционного усилителя в начале второго такта преобразования, [V];

Uout - напряжение на выходе операционного усилителя в момент сравнения с уровнем сравнения, [V].

Из уравнения погрешностей, которое составляется для выражения (2), следует, что относительная погрешность измерения интервала времени во втором такте δtm определяется следующим выражением

В выражении (3) относительная погрешность δk1 определяется нестабильностью элементов, обеспечивающих ток заряда-разряда конденсатора, относительная погрешность δU0 определяется действием аддитивных помех на входе преобразователя, а относительная погрешность δUout определяется нестабильностью уровня сравнения.

Действие аддитивных помех приводит к изменению результата интегрирования в первом такте. Механизм действия аддитивных помех может быть описан следующим образом. Низкочастотная помеха, действующая на входе преобразователя, так же как и входной сигнал, в течение первого такта преобразования интегрируется по времени и представляет собой ненулевой в общем случае уровень напряжения. Сумма напряжения, вызванного входным током и напряжения помехи с учетом его знака, обусловливает изменение величины электрического заряда, накопленного конденсатором интегратора к концу первого такта по отношению к случаю, когда помеха отсутствует. Ошибка (±ΔU, фиг. 1), в зависимости от ее знака, увеличивает или уменьшает величину электрического заряда, накопленного конденсатором к концу первого такта. Это приводит к тому, что выходное напряжение операционного усилителя, линейно изменяющееся во времени во втором такте, смещается на величину, пропорциональную изменению интеграла от входного сигнала из-за действия аддитивной помехи. Это вызывает во втором такте преобразования смещение момента сравнения выходного напряжения операционного усилителя с заданным уровнем сравнения на величину Δt1 (фиг. 1), пропорциональную смещению ΔU (фиг. 1) напряжения U0. По отношению к высокочастотной аддитивной помехе конденсатор обладает малым сопротивлением. В этом случае операционный усилитель становится усилителем, охваченным глубокой обратной связью, и текущая величина помехи суммируется с сигналом на выходе операционного усилителя, также влияя на величину ±ΔU, что также смещает момент сравнения выходного напряжения операционного усилителя с заданным уровнем сравнения, обеспечивая свой вклад в величину Δt1 и, соответственно, δU0. Таким образом, величина рассматриваемого смещения в широкой полосе частот зависит от уровня аддитивной помехи и вносит вклад в относительную погрешность преобразования.

Недостатком рассмотренного способа-прототипа аналого-цифрового преобразования является большая относительная погрешность преобразования при действии аддитивных помех, поскольку измеряемый временной интервал во втором такте преобразования линейно зависит от напряжения на выходе операционного усилителя к моменту окончания первого такта преобразования, и погрешность измерения временного интервала линейно связана с погрешностью выходного напряжения интегратора к моменту окончания первого такта преобразования.

Известно устройство, реализующее двухтактное аналого-цифровое преобразование интегрирующего типа, приведенное в патенте США №3316547 (опубликовано 25.04.1967). Вход этого устройства через последовательно соединенные управляемый двухвходовый ключевой элемент и резистор соединен со входом операционного усилителя, параллельно операционному усилителю включены конденсатор и разрядный ключ, этот же вход операционного усилителя также соединен с источником постоянного опорного напряжения через указанные последовательно соединенные резистор и управляемый двухвходовый ключевой элемент. Выход операционного усилителя соединен с одним из входов компаратора, выход компаратора соединен с одним входом логической схемы «И», второй вход которой соединен с генератором высокочастотных импульсов, выход логической схемы «И» соединен со счетным входом счетчика импульсов, управляющий вход счетчика импульсов соединен с одним из выходов устройства управления стартом и сбросом. Выходы устройства управления стартом и сбросом соединены со входами двух триггеров. Выход первого триггера соединен с управляющим входом разрядного ключа. Первый вход второго триггера соединен с управляющим выходом счетчика импульсов, выход этого триггера соединен с управляющим входом управляемого двухвходового ключевого элемента. Основной выход счетчика импульсов является выходом устройства, на этом выходе счетчика импульсов действует искомый цифровой код.

Недостатком данного устройства по патенту США №3316547 является большая относительная погрешность преобразования при действии аддитивных помех, которая получается вследствие линейной связи напряжения на выходе операционного усилителя к моменту окончания второго такта преобразования, с цифровым кодом на выходе устройства в этом же цикле преобразования.

Наиболее близким к предложенному является двухтактный аналого-цифровой преобразователь интегрирующего типа [Аналого-цифровое преобразование, ред. Уолт Кестер, перевод с английского под ред. Е.Б. Володина, М: Техносфера, 2007, стр. 271, рис. 3.113], вход которого через последовательно соединенные управляемый двухвходовый ключевой элемент и резистор соединен с инвертирующим входом операционного усилителя, параллельно которому включен конденсатор, этот же вход операционного усилителя также соединен с выходом источника постоянного опорного напряжения через указанные последовательно соединенные резистор и управляемый двухвходовый ключевой элемент, неинвертирующий вход операционного усилителя соединен с шиной, имеющей нулевой потенциал, выход операционного усилителя соединен с первым входом компаратора, второй вход компаратора соединен с источником уровня сравнения в виде шины, имеющей нулевой потенциал, выход компаратора соединен со входом блока тактирования и управления, выходы которого соединены с управляющим входом управляемого двухвходового ключевого элемента и со входом блока кодирования, который состоит из последовательно соединенных осциллятора, логической схемы «И» и счетчика, выход счетчика является выходом блока кодирования и выходом аналого-цифрового преобразователя.

В указанных в качестве прототипов способе и устройстве аналого-цифрового преобразования входная электрическая величина в форме электрического тока имеет промежуточное преобразование во временной интервал, который затем преобразуется в цифровой код.

Недостатком аналого-цифрового преобразователя - прототипа, реализующего описанный выше способ преобразования по прототипу, также является большая относительная погрешность преобразования при действии аддитивных помех, что обусловлено линейной связью напряжения на выходе операционного усилителя к моменту окончания первого такта преобразования, с цифровым кодом на выходе преобразователя в этом же цикле преобразования.

Задачей группы изобретений является создание способа и устройства, обеспечивающих уменьшение относительной погрешности преобразования при действии аддитивных помех.

Для решения указанной задачи способ двухтактного аналого-цифрового преобразования интегрирующего типа, при котором измеряемый электрический сигнал в форме входного зарядного тока интегрируют по времени в течение первого такта с помощью последовательно соединенных резистора и операционного усилителя, параллельно которому подключен конденсатор, в результате чего на конденсаторе накапливают электрический заряд, во втором такте формируют разрядный ток путем подачи, вместо измеряемого электрического сигнала, опорного напряжения, образующего разрядный ток, который имеет направление, противоположное направлению входного зарядного тока, при этом накопленный в первом такте на конденсаторе электрический заряд уменьшают до момента сравнения выходного напряжения операционного усилителя с заранее определенным уровнем сравнения, в качестве результата измерения используют временной интервал от начала второго такта до момента сравнения, который преобразуется в цифровой отсчет,

отличается тем, что

во втором такте разрядный ток изменяют во времени в соответствии с выражением

где

I0=const - выбираемое значение тока, которое определяет выбор номинала емкости конденсатора, включенного параллельно операционному усилителю, уровень напряжения на выходе операционного усилителя в конце первого такта, длительность времени второго такта, [A];

- масштабный коэффициент, имеющий размерность [sec-1]

R - сопротивление резистора, [Ω];

p - положительное действительное число.

Для решения той же задачи двухтактный аналого-цифровой преобразователь интегрирующего типа, вход которого соединен с первым входом управляемого двухвходового ключевого элемента, выход которого через резистор соединен с инвертирующим входом операционного усилителя, параллельно которому включен конденсатор, второй вход управляемого двухвходового ключевого элемента соединен с выходом источника тока разряда, неинвертирующий вход операционного усилителя соединен с шиной, имеющей нулевой потенциал, выход операционного усилителя соединен с первым входом компаратора, второй вход компаратора соединен с источником уровня сравнения, выход компаратора соединен со входом блока управления, один выход которого соединен с управляющим входом управляемого двухвходового ключевого элемента, а второй выход соединен со входом блока кодирования, выход которого является выходом аналого-цифрового преобразователя,

отличается тем, что

источник тока разряда реализует функцию изменения тока разряда на входе операционного усилителя в соответствии с выражением

где

I0=const - выбираемое значение тока, которое определяет выбор номинала емкости конденсатора, включенного параллельно операционному усилителю, уровень напряжения на выходе операционного усилителя в конце первого такта, длительность времени второго такта, [A];

- масштабный коэффициент, имеющий размерность [sec-1],

R - сопротивление резистора,

p - положительное действительное число,

при этом источник тока разряда имеет управляющий вход, который соединен с выходом блока включения/выключения источника тока разряда, вход блока включения/выключения источника тока разряда соединен с одним из выходов блока управления.

Технический результат, заключающийся в уменьшении относительной погрешности преобразования при действии аддитивных помех, достигается введением в способ и устройство по прототипу изменения тока разряда на входе операционного усилителя во втором такте преобразования «аналог-код» в соответствии с выражением (4).

При изменении тока разряда во втором такте преобразования «аналог-код», описываемом для предложенных способа и устройства указанным выше выражением (4), напряжение на выходе операционного усилителя изменяется во времени следующим образом:

где

U(t) - напряжение на выходе операционного усилителя, [V];

t - текущее время, t=0 в начале второго такта преобразования, [sec];

U0 - напряжение на выходе операционного усилителя в начале второго такта преобразования, [V];

C - емкость конденсатора, [F].

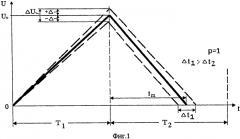

Повышение точности преобразования при действии аддитивных помех в предложенных способе и устройстве обусловлено тем, что при нелинейном разряде конденсатора током, который описывается выражением (4) с показателем степени p>0, скорость изменения напряжения на выходе операционного усилителя с течением времени возрастает. На фиг. 2 показано, что в этом случае из-за нелинейности изменения выходного напряжения операционного усилителя модуль крутизны этого изменения возрастает во времени, что уменьшает абсолютную погрешность при действии аддитивных помех по сравнению с линейным изменением (Δt2<Δt1).

Реально по отношению к прототипу относительная погрешность преобразования при действии аддитивных помех и, например, линейном изменении тока разряда конденсатора (p=1), уменьшается в 2 раза во всем диапазоне преобразования при любом уровне аддитивных помех, не приводящих к появлению однократных «выбросов» значений выходного кода как при изменении тока разряда конденсатора, так и при его постоянном значении.

Единство технического результата способа и устройства обеспечивается тем, что в способе и устройстве формируется ток разряда, изменяющийся в течение второго такта преобразования в соответствии с выражением (4) при p>0, что обеспечивает нелинейное изменение напряжения на конденсаторе во время второго такта (разряда конденсатора), и, соответственно, нелинейное изменение напряжения на выходе операционного усилителя производится в соответствии с выражением (5).

Приведем математическое обоснование достигнутого технического результата.

Как указано, напряжение на конденсаторе и, соответственно, на выходе операционного усилителя, при любом изменении тока разряда конденсатора в течение второго такта преобразования изменяется нелинейно во времени. Это приводит к тому, что приращение напряжения на одном и том же интервале времени, во втором такте преобразования зависит от самого параметра времени, то есть

При p>0

В случае линейного разряда конденсатора это не так, то-есть,

Длительность искомого временного интервала tm, в течение которого конденсатор разряжается и напряжение на выходе операционного усилителя становится равным уровню сравнения U1, выраженная в цифровом виде, и является выходным параметром для предлагаемых способа и устройства. Величину искомого временного интервала tm можно определить из выражения (5). Оно нелинейно зависит от U0, которое является результатом интегрирования входного тока преобразователя к началу второго такта преобразования. При заранее заданном уровне сравнения U1 нелинейная зависимость длительности искомого временного интервала tm от напряжения U0 можно выразить следующим образом:

где

tm - искомый временной интервал, [sec],

величины p, C, I0 пояснены выше.

Выражение (9) может быть представлено как степенная функция следующего вида

где

X=(U0-U1), k=α, n - действительное число.

Проведем анализ суммарной относительной погрешности измерения входной величины X.

Совокупность внешних и внутренних воздействующих факторов, а также технологический разброс параметров компонентов и их нестабильность приводят к искажению выходных данных. Уравнение, описывающее измерение входных величин с учетом возможных абсолютных погрешностей, имеет вид:

где

Δy, ΔX, Δk, Δn - абсолютные погрешности измерения, входной величины, масштабного коэффициента и показателя степени, соответственно.

Погрешность входной величины определяется действием аддитивных помех, погрешность масштабного коэффициента определяется нестабильностью параметров электрической схемы при реализации преобразователя, в том числе нестабильностью уровня сравнения, погрешность показателя степени определяется погрешностью формирования заданной формы изменения разрядного тока.

Из (11) следует уравнение для суммарной относительной погрешности измерения:

где

δy, δk, δX, δn - относительные значения суммарной погрешности измерения, масштабного коэффициента, погрешности входной величины и показателя степени, соответственно.

Из (12) следует, что δy существенно зависит от показателя степени n. Дальнейший анализ показывает, что если n<1, то суммарная относительная погрешность δy для любых значений входного параметра X при прочих равных условиях, то-есть, для одних и тех же значений δk, δХ, δn, будет всегда меньше, чем при n≥1. Из анализа (12) следует, что при наличии аддитивных помех во входном измеряемом сигнале и действии факторов, приводящих к нестабильности параметров схемы устройства при его аппаратной реализации, суммарная относительная погрешность нелинейного преобразования с уменьшением показателя степени n уменьшается.

Таким образом, всегда верно следующее неравенство:

Из выражения (9) следует, что

и суммарная относительная погрешность измерения монотонно уменьшается при увеличении показателя степени p.

Исходя из вышеприведенного анализа, в применении к заявляемому способу можно сформулировать следующий вывод: нелинейное возрастание во времени тока разряда конденсатора во втором такте интегрирования, описываемое выражением (4), при p>0 обеспечивает повышенную крутизну выходного сигнала операционного усилителя вблизи точки сравнения с постоянным уровнем сравнения и, соответственно, меньшую суммарную относительную погрешность измерения входных сигналов в аддитивных шумах.

Вышеприведенные рассуждения справедливы как для общего случая произвольного представления выходного параметра измерения y, так и частного случая представления этого параметра в виде цифрового кода, когда выходной параметр измерения может быть

представлен в виде:

(15),

где

a i - i-ая цифра кода, γ - основание системы счисления.

Выражения (9) и (10) с точностью до обозначения yD при этом не изменяются.

Краткое описание чертежей:

фиг. 1 - временные зависимости сигналов на выходе операционного усилителя в схеме прототипа при наличии и отсутствии аддитивных помех во входном сигнале;

фиг. 2 - временные зависимости сигналов на выходе операционного усилителя в предложенном устройстве при наличии и отсутствии аддитивных помех при нелинейном изменении напряжения на выходе операционного усилителя, описываемом уравнением (4) при p>0;

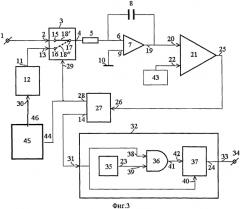

фиг. 3 - структурная схема преобразователя, реализующего предложенный способ двухтактного аналого-цифрового преобразования интегрирующего типа;

фиг. 4 - временные зависимости сигналов на выходах блоков структурной схемы предложенного аналого-цифрового преобразователя, номера выходов блоков указаны на осях ординат.

Предложенный способ реализуется двухтактным аналого-цифровым преобразователем интегрирующего типа (фиг. 3), вход 1 которого соединен с первым входом 2 управляемого двухвходового ключевого элемента 3. Выход 4 ключевого элемента 3 через резистор 5 соединен с инвертирующим входом 6 операционного усилителя 7, параллельно которому включен конденсатор 8. Операционный усилитель 7 с параллельно включенным конденсатором 8 реализует интегрирование входного тока по параметру времени. Вход 9 операционного усилителя 7 соединен с шиной 10, имеющей нулевой потенциал. Выход 11 источника тока разряда 12 соединен со вторым входом 13 двухвходового ключевого элемента 3.

Первый вход 2 управляемого двухвходового ключевого элемента 3 соединен внутри элемента 3 с контактом 15 элемента 3, а второй вход 13 элемента 3 соединен внутри элемента 3 с контактом 16 элемента 3. Выход 4 элемента 3 соединен внутри элемента 3 с контактом 17 этого элемента. Перемычка 18′ внутри элемента 3 в первом такте работы устройства соединяет контакт 17 или с контактом 15 (изображена непрерывной линией), или (во втором такте работы) - с контактом 16 (положение перемычки 18′′ изображено пунктиром).

Выход 19 операционного усилителя 7 соединен с первым входом 20 компаратора 21, второй вход 22 компаратора 21 соединен с выходом источника уровня сравнения 43, а выход 25 компаратора 21 соединен со входом 26 блока управления 27. Выход 28 блока управления 27 соединен с управляющим входом 29 управляемого двухвходового ключевого элемента 3 и со входом 44 блока включения/выключения 45, выход которого 46 соединен с управляющим входом 30 источника тока разряда 12. Выход 14 блока управления 27 соединен со входом 31 блока кодирования 32, выход 33 которого соединен с выходом 34 аналого-цифрового преобразователя.

Блок кодирования 32 (фиг. 3) включает осциллятор 35, являющийся источником счетных импульсов, логический элемент «И» 36 и счетчик импульсов 37, при этом вход 31 блока кодирования 32 соединен со входом 38 логического элемента «И» 36 и входом 40 счетчика 37 (вход управления счетчиком 37). Второй вход 39 логического элемента «И» 36 соединен с выходом 23 осциллятора 35. Выход 41 логического элемента «И» 36 соединен со счетным входом 42 счетчика 37, а цифровой выход 24 счетчика 37 является выходом 33 блока кодирования 32 и цифровым выходом 34 аналого-цифрового преобразователя.

При разработке схемы двухтактного аналого-цифрового преобразователя интегрирующего типа выбирают значение тока I0=const, которое определяет выбор номинала емкости конденсатора 8, включенного параллельно операционному усилителю 7, уровень напряжения на выходе операционного усилителя 7 в конце первого такта, длительность времени второго такта. Например, при I0=1,5 mA и уровне напряжения на выходе операционного усилителя 7 в конце первого такта U0 равном 5 V, номинал емкости конденсатора 8, включенного параллельно операционному усилителю 7, равен 1 nF, длительность времени второго такта T2 составляет 3 ms. Такие параметры имеют место при аналого-цифровом преобразовании слаботочных сигналов.

Предложенный двухтактный аналого-цифровой преобразователь интегрирующего типа, представленный на фиг. 3, работает следующим образом. Временные диаграммы напряжений в нескольких точках преобразователя, поясняющие его работу, представлены на фиг. 4.

Процесс преобразования электрических параметров осуществляется в два этапа (временных такта): в течение первого такта происходит накопление заряда конденсатором 8, при этом уровень напряжения на выходе операционного усилителя 7 (интегратора) пропорционален интегралу от входного электрического тока. В течение второго такта происходит разряд конденсатора 8 до момента сравнения напряжения на выходе 19 операционного усилителя 7 с уровнем напряжения источника уровня сравнения 43, которое производится амплитудным компаратором 21. Последовательность и длительность этапов работы устройства определяется блоком управления 27. В первом такте блок управления 27 устанавливает ключевой элемент 3 в положение 18′, соединяя вход 1 преобразователя с резистором 5, при этом конденсатор 8 начинает заряжаться, и заряд, накопленный конденсатором 8, зависит от тока, действующего на входе 1. При этом обеспечивается пропорциональность выходного напряжения операционного усилителя 7 интегралу от входного тока.

Во втором такте блок управления 27 устанавливает ключевой элемент 3 в положение 18″, подключая к резистору 5 источник тока разряда 12, и запускает блок включения/выключения 45, который, в соответствии с выходным сигналом блока управления 27, определяет моменты начала и окончания генерации источником 12 разрядного тока, который изменяется во времени в соответствии с выражением (5) и обеспечивает изменение напряжения на конденсаторе 8. В результате этого на выходе операционного усилителя 7 напряжение в течение второго такта уменьшается нелинейно согласно выражению (4). Вид нелинейности определяется изменением разрядного тока источника тока разряда 12, и, в соответствии с выражением (4), положительный эффект достигается, если ток с течением времени увеличивается. В момент равенства выходного напряжения операционного усилителя 7 уровню напряжения источника уровня сравнения 43, амплитудный компаратор 21 формирует импульсный сигнал, который поступает на вход 26 блока управления 27. В результате на выходе 14 блока управления 27 формируется импульсный сигнал, передний фронт которого совпадает с моментом начала второго такта интегрирования, а задний фронт совпадает с моментом начала импульсного сигнала на выходе 25 амплитудного компаратора 21. Этот импульсный сигнал поступает на вход 31 блока кодирования 32. В блоке кодирования 32 на выходе 23 осциллятора 35 непрерывно формируется последовательность импульсных сигналов, которые, поступая на вход 39 логического элемента «И» 36, проходят на его выход 41 при появлении на втором входе 38 логического элемента «И» 36 импульсного сигнала со входа 31 блока кодирования 32. В результате на входе 42 счетчика 37 появляются импульсные сигналы осциллятора 35, число которых определяется длительностью импульсного сигнала на входе 31 блока кодирования 32 и определяет состояние счетчика 37 на выходе 33 блока кодирования 32 по окончании импульсного сигнала на его входе 31. На выходе 28 блока управления 27 после появления импульсного сигнала на выходе 25 амплитудного компаратора 21 формируется импульсный сигнал, который переключает ключевой элемент 3 в положение 18′, и разрешает блоку включения/выключения 45 остановить генерацию тока разряда источником 12 и привести источник тока разряда 12 в исходное положение. После этого цикл преобразования измеряемой электрической величины на входе 1 в кодовое число на выходе 34 устройства заканчивается. Момент начала нового цикла измерения определяется блоком управления 27.

1. Способ двухтактного аналого-цифрового преобразования интегрирующего типа, при котором измеряемый электрический сигнал в форме входного зарядного тока интегрируют по времени в течение первого такта с помощью последовательно соединенных резистора и операционного усилителя, параллельно которому подключен конденсатор, в результате чего на конденсаторе накапливают электрический заряд, во втором такте формируют разрядный ток путем подачи, вместо измеряемого электрического сигнала, опорного напряжения, образующего разрядный ток, который имеет направление, противоположное направлению входного зарядного тока, при этом накопленный в первом такте на конденсаторе электрический заряд уменьшают до момента сравнения выходного напряжения операционного усилителя с заранее определенным уровнем сравнения, в качестве результата измерения используют временной интервал от начала второго такта до момента сравнения, который преобразуется в цифровой отсчет,отличающийся тем, чтово втором такте разрядный ток изменяют во времени в соответствии с выражениемIc(t)=I0(kt)p,гдеI0=const - выбираемое значение тока, которое определяет выбор номинала емкости конденсатора, включенного параллельно операционному усилителю, уровень напряжения на выходе операционного усилителя в конце первого такта, длительность времени второго такта, [A]; - масштабный коэффициент, имеющий размерность [sec-1],R - сопротивление резистора, [Ω];p - положительное действительное число.

2. Двухтактный аналого-цифровой преобразователь интегрирующего типа, вход которого соединен с первым входом управляемого двухвходового ключевого элемента, выход которого через резистор соединен с инвертирующим входом операционного усилителя, параллельно которому включен конденсатор, второй вход управляемого двухвходового ключевого элемента соединен с выходом источника тока разряда, неинвертирующий вход операционного усилителя соединен с шиной, имеющей нулевой потенциал, выход операционного усилителя соединен с первым входом компаратора, второй вход компаратора соединен с источником уровня сравнения, выход компаратора соединен со входом блока управления, один выход которого соединен с управляющим входом управляемого двухвходового ключевого элемента, а второй выход соединен со входом блока кодирования, выход которого является выходом аналого-цифрового преобразователя,отличающийся тем, чтоисточник тока разряда реализует функцию изменения тока разряда на входе операционного усилителя в соответствии с выражениемIc(t)=I0(kt)p,гдеI0=const - выбираемое значение тока, которое определяет выбор номинала емкости конденсатора, включенного параллельно операционному усилителю, уровень напряжения на выходе операционного усилителя в конце первого такта, длительность времени второго такта, [A]; - масштабный коэффициент, имеющий размерность [sec-1],R - сопротивление резистора, [Ω];p - положительное действительное число,при этом источник тока разряда имеет управляющий вход, который соединен с выходом блока включения/выключения источника тока разряда, вход блока включения/выключения источника тока разряда соединен с одним из выходов блока управления.