Устройство фазовой автоподстройки частоты

Иллюстрации

Показать всеИзобретение относится к устройствам стабилизации параметров автогенераторов и может быть использовано в технике связи и управления, радиоавтоматике, системах авторегулирования. Достигаемый технический результат - повышение устойчивости, определяющей полосу захвата частоты, при сохранении высокой точности фазовой синхронизации. Устройство фазовой автоподстройки частоты содержит знакомодульный логический фазовый дискриминатор (ЗМЛФД), управляемый генератор, три сумматора напряжений, интегратор, пропорциональное звено, два формирователя напряжения, два обнуляемых интегратора и делитель частоты. 2 ил.

Реферат

Изобретение предназначено для стабилизации параметров автогенераторов, применяемых в радиотехнических и измерительных устройствах.

Известны устройства (системы) фазовой автоподстройки частоты (ФАПЧ) [1-3], обеспечивающие высокую точность синхронизации, проявляющуюся в высокой стабильности полезного колебания, формируемого на основе опорного колебания. Системы ФАПЧ с фильтрующими цепями астатического типа [1] реализуют фазовую синхронизацию формируемого колебания относительно опорного с точностью, определяемой параметрами фазового детектора (дискриминатора).

Использование в составе астатических систем ФАПЧ фазовых дискриминаторов цифрового типа (логических фазовых дискриминаторов) [4, 5, 7] позволяет выполнять подстройку формируемого колебания относительно опорного колебания с разностью фаз Δφ→0. Это подтверждается выкладками, опубликованными в [9, 10].

Наивысшая точность синхронизации при достаточной устойчивости структуры обеспечивается в астатической системе ФАПЧ [6]. В ней для повышения устойчивости используется блок формирования напряжений, содержащий совокупность обнуляемых интеграторов с положительными обратными связями, позволяющими реализовывать нелинейный закон формирования управляющих напряжений. Указанная система ФАПЧ выбрана в качестве прототипа.

Использование такой структуры в случае, когда знак разности фаз в процессе подстройки частоты меняется с периодом, значительно превышающим период частоты опорного колебания, позволяет получать на выходе формирователя напряжение большого уровня. Это напряжение, воздействуя на управляемый (подстраиваемый) генератор, способствует интенсификации процесса захвата в системе. В то же время, когда разность фаз находится в диапазоне вблизи нуля, смена знака разности фаз на выходе фазового дискриминатора осуществляется периодически с периодом опорного колебания. За указанное время напряжение на выходе формирователя напряжения нарастает незначительно. Последнее уменьшает интенсивность воздействия на управляемый генератор и соответственно уменьшает уровень флуктуации разности фаз в режиме синхронизации.

Недостатком прототипа является то, что стремление уменьшить уровень флуктуации разности фаз в установившемся режиме приводит к уменьшению ее устойчивости, проявляющемся в уменьшении полосы захвата системы. Это иллюстрируется аналитическими выкладками, представленными в [8]. Здесь показано, что при обеспечении установившейся фазовой ошибки (флуктуации разности фаз в установившемся режиме работы ФАПЧ) Δφmin=2,3π·10-4, в системе автоподстройки частоты при отношении постоянных времени Тп прямой и обратной Тo цепей обнуляемых интеграторов, равной 1000, обеспечивается полоса захвата Ωz≤0,1Ωу, где Ωу - полоса удержания системы ФАПЧ. Такая полоса захвата является недостаточной.

Расширение полосы захвата возможно за счет введения в контур регулирования ФАПЧ фазового дискриминатора знакомодульного типа [5, 7] и образования дополнительного канала подстройки частоты, использующего информацию, формируемую на модульных (пропорциональных) выходах дискриминатора.

Целью изобретения является повышение устойчивости при сохранении высокой точности фазовой синхронизации. Указанная цель достигается усовершенствованием изобретения по авторскому свидетельству №1415441 [6]. Сущность изобретения состоит в замене логического фазового дискриминатора знакового типа, используемого в прототипе, логическим дискриминатором знакомодульного типа (заявка №2013157154/08(089096) от 23.12.2013 г., положительное решение о выдаче патента от 27.10.2014 г.), в котором обеспечивается раздельная работа знаковых и модульных выходов, и введении в структуру прототипа дополнительного канала подстройки частоты, содержащего дополнительные формирователь напряжения, сумматор напряжений и делитель частоты.

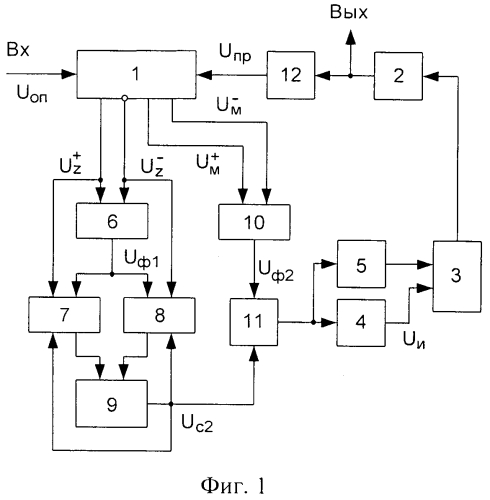

Рассмотрим структуру и принцип функционирования предлагаемого устройства. На фиг. 1 приведена структурная схема предлагаемого устройства ФАПЧ, а на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство ФАПЧ, показанное на фиг. 1, содержит знакомодульный логический фазовый дискриминатор (ЗМЛФД) 1, управляемый генератор 2, первый сумматор напряжений 3, интегратор 4, пропорциональное звено 5, первый формирователь напряжения 6, обнуляемые интеграторы 7 и 8, второй сумматор 9, второй формирователь напряжения 10, третий сумматор напряжений 11 и делитель частоты 12.

Предлагаемое устройство ФАПЧ работает следующим образом. На первый вход ЗМЛФД 1 поступает напряжение опорного колебания Uоп, имеющее уровни цифровой логики, а на второй его вход - напряжение Uпр подстраиваемого колебания, полученного на основе выходного колебания управляемого генератора (УГ) 2, путем деления его частоты с помощью делителя частоты 12. Включение в структуру ФАПЧ делителя частоты вызвано тем, что знакомодульный логический дискриминатор обеспечивает свои свойства в случае, когда сравниваемые им частоты имеют близкие значения. Когда частота, формируемая УГ кратна опорной fуг=nfоп, где n - коэффициент кратности, для их уравнивания между выходом УГ и входом ЗМЛФД следует включить делитель частоты с коэффициентом деления n. Когда сравниваемые частоты близки, необходимость применения в структуре делителя частоты отпадает.

Знаковые выходы дискриминатора управляют первым формирователем напряжения 6 и обнулением интеграторов 7 и 8. Обнуляемые интеграторы 7 и 8 работают следующим образом. Когда знак разности фаз сравниваемых дискриминатором колебаний положителен ( U z + = 0, U z − = 1 ) , первый формирователь напряжения 6 вырабатывает отрицательное напряжение, которое интегрируется интегратором 7 (интегратор 8 в это время поддерживается в обнуленном состоянии сигналом U z − = 1 ). Кода знак разности фаз отрицателен ( U z + = 1, U z − = 0 ) формирователь 6 вырабатывает положительное напряжение, при этом работает интегратор 8, а интегратор 7 обнулен. Суммируемые вторым сумматором 9 напряжения по цепям обратных связей подаются на вторые входы обнуляемых интеграторов 7 и 8. Поскольку связи со стороны сумматора 9 являются положительными, это обеспечивает на выходе интеграторов, и, следовательно, на выходе сумматора 9, формирование напряжения, изменяющегося по закону экспоненты.

В случае, когда время существования разности фаз одного знака значительно (имеет место в режиме захвата фазы), на выходе сумматора 9 напряжение может достигать значительных величин. В то же время при частой смене разности фаз (имеет место в режиме биений и режиме синхронизма), анализируемых дискриминатором колебаний, за счет сброса напряжений обнуляемых интеграторов напряжение на выходе сумматора 9 изменяется незначительно.

В применяемом в предлагаемом устройстве логическом дискриминаторе знакомодульного типа запрещается одновременная работа знаковых и модульных выходов. Так в режимах биений и захвата за счет того, что разность фаз анализируемых колебаний имеет значительные величины, разрешается работа только модульных (пропорциональных) выходов дискриминатора. При уменьшении разности фаз до значений, определяемых зоной нечувствительности модульного канала дискриминатора, работа модульных выходов запрещается, а разрешается работа знаковых выходов. Незначительное изменение разности фаз, обеспечиваемое кольцом автоподстройки, реализуется в режиме синхронизма и обеспечивается воздействием на управляемый генератор сигналов, формируемых под действием напряжений знаковых выходов дискриминатора.

Напряжения, вырабатываемые на модульных выходах дискриминатора, несут информацию о величине разности фаз между анализируемыми колебаниями. Под их воздействием во втором формирователе напряжения 10 создаются импульсные напряжения разных знаков, длительность которых определяется длительностями импульсных сигналов U м + , U м − на модульных выходах дискриминатора. Причем длительности импульсных сигналов, формируемых на пропорциональных выходах дискриминатора, уменьшены на величину, определяемую зоной нечувствительности Δtзн модульного канала ЗМЛФД. Напряжения с выходов второго сумматора 9 и второго формирователя 10 суммируются третьим сумматором напряжений 11 и подаются на входы пропорционального звена 5 и интегратора 4.

Для обеспечения широкой полосы захвата воздействие со стороны формирователя 10 делается более интенсивным, чем со стороны второго сумматора 9. Это обеспечивается тем, что уровень амплитуд напряжений на выходе формирователя 10 устанавливается большим, чем амплитуды напряжений на выходе формирователя 6.

Поступающее на управляющий вход УГ 2 напряжение со стороны первого сумматора 3, формируемое путем суммирования напряжений интегратора 4 и пропорционального звена 5, вызывает изменение частоты подстраиваемого колебания. Астатическое звено, состоящее из интегратора 4 и пропорционального звена 5, обеспечивает астатизм устройства ФАПЧ, способствующий полной отработке фазовой ошибки.

Поскольку в режиме захвата существенное влияние на процесс подстройки частоты оказывает контур регулирования, основанный на использовании сигналов с модульных выходов дискриминатора, а влияние кольца подстройки частоты, использующего сигналы со знаковых выходов дискриминатора, незначительно, то в данном режиме работы предлагаемая система уподобляется автономной системе ФАПЧ с фильтром первого порядка, выполненным в виде астатического звена. В [1, стр. 179] показано, что в такой системе ФАПЧ обеспечивается полоса захвата, равная полосе удержания.

Включение в контур регулирования делителя частоты 12 может привести к появлению дополнительного статического фазового сдвига между опорным и подстраиваемым колебаниями. Однако использование синхронных схем делителей частоты может уменьшить величину этого сдвига. Причем сдвиг будет стабильным и иметь значение, во временном выражении определяемое скоростью переключения одного триггера счетчика. При использовании современных логических схем величина этого сдвига во временном выражении может не превышать единиц наносекунд. Для невилирования возникающей задержки при одновременном использовании подстраиваемого и опорного колебаний, с целью исключения статического фазового сдвига сигнал опорного колебания, подаваемый на вход предлагаемого устройства, перед его использованием в других схемах следует пропустить через дополнительную логическую схему (например, через цепочку из последовательно включенных логических вентилей). Следует только подобрать тип логических вентилей, имеющий задержку, равную времени переключения триггера счетчика.

Когда частоты опорного и подстраиваемого колебаний близки (коэффициент кратности равен 1), необходимость в делителе частоты отпадает и никакой постоянной фазовой ошибки между опорным и подстраиваемым колебаниями не возникает.

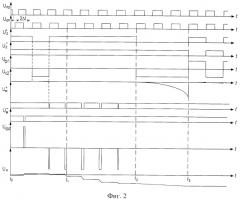

Эпюры напряжений, показанные на фиг.2, отражают процессы, существующие в предлагаемом устройстве. На интервале t0-t1 иллюстрируется поведение предлагаемого устройства в режиме биений. Причем здесь рассматриваются случаи, когда разность фаз между опорным Uоп и подстраиваемым Uпр колебаниями находится как за пределами зоны нечувствительности модульного канала ЗМЛФД (в это время управляющее напряжение Uф2 формируется только на выходе второго формирователя напряжения (Uф1=0, Uф2≠0)), так и в зоне нечувствительности (в это время управляющее напряжение Uc2 формируется только на выходе второго сумматора (Uф1≠0, Uф2=0)), размах которой определяется как 2Δtзн (|-Δtзн|=|+Δtзн|). Напряжения, формируемые на выходе второго формирователя напряжения, имеют длительность, определяемую сигналами на модульных выходах логического дискриминатора. Их длительности по сравнению с реальными задержками фронтов анализируемых колебаний Uоп и Uпр уменьшены на величину Δtзн. Последнее определяется логикой работы ЗМЛФД.

На интервале t1-t2 иллюстрируется поведение предлагаемого устройства в режиме захвата фазы. При этом разность фаз находится за пределами зоны нечувствительности модульного канала дискриминатора. В этом случае управление обеспечивается только воздействиями Uф2 со стороны второго формирователя напряжения.

На интервале от t2 и далее иллюстрируется поведение предлагаемого устройства в режиме удержания фазы, когда разность фаз не превышает значения зоны нечувствительности модульного канала ЗМЛФД. Здесь работает только канал подстройки, управляемый знаковыми выходами дискриминатора. Если разность фаз значительна, то ее отработка производится в течение нескольких периодов опорного колебания (на интервале t2-t3). При этом напряжение Uc2 на выходе второго сумматора изменяется значительно, что способствует удержанию разности фаз в пределах зоны нечувствительности и повышению оперативности ее отработки. После t3 иллюстрируется случай, когда разность фаз изменяется периодически с периодом опорного колебания. При этом воздействие на процесс подстройки частоты со стороны второго сумматора напряжений незначительно. Это обеспечивает малую величину флуктуации разности фаз в установившемся режиме работы предлагаемого устройства.

Процесс подстройки также иллюстрируется поведением напряжения Uи на выходе интегратора астатического звена.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Системы фазовой синхронизации с элементами дискритизации. 2-е изд., доп. и перераб. / В.В. Шахгильльдян, А.А. Ляховкин, В.Л. Корякин и др.; под ред. В.В. Шахгильдяна. - М.: Радио и связь, 1989. - 320 с.

2. Принципы фазовой синхронизации в измерительной технике. - Томск: Радио и связь, 1989. - 384 с.

3. Цифровые системы фазовой синхронизации / Под ред. М.И. Жодзишского. - М.: Сов. Радио, 1980. - 208 с.

4. А.с. 1248026 СССР, МКИ Н03D 13/00, G01R 25/00. Фазовый дискриминатор/В.Ф. Одиноков. №3669946/24-09; заявлено 25.11.83; опубл. 30.07.86 в БИ №28.

5. А.с.1432724 СССР, МКИ Н03D 13/00, G01R 25/00. Фазовый дискриминатор / В.Ф. Одиноков, С.И. Холопов. №4212180/24-09; заявлено 19.03.87; опубл. 23.10.88 в БИ №39.

6. А.с. 1415441 СССР, МКИ Н03L 7/00. Устройство фазовой автоподстройки частоты / В.Ф. Одиноков, С.И. Холопов, М.В. Петров. №4162161/24-09; заявлено 11.12.86; опубл. 07.08.88. Бюл. №29.

7. А.с. 1568207 СССР, МКИ Н03D 13/00. Фазовый дискриминатор / В.Ф. Одиноков, С.И. Холопов. №4374505; заявлено 05.02.88; опубл. 30.05.90 в БИ №20.

8. Холопов С.И. Расширение полосы захвата релейной астатической системы фазовой синхронизации // Вестник Рязанского государственного радиотехнического университета. 2013. №3 (выпуск 45). С. 49-53.

9. Холопов С.И., Одиноков В.Ф. Сдвиг нуля дискриминационной характеристики логического фазового дискриминатора // Депонированные рукописи. №1135-св 87. ВИНИТИ, 1987. №12.

10. Холопов С.И. Анализ релейной системы ФАПЧ с обнуляемыми интеграторами // Вестник РГРТУ. 2011. №4 (выпуск 38). - С. 50-54.

Устройство фазовой автоподстройки частоты, содержащее управляемый генератор, выход которого является выходом устройства, а вход соединен с выходом первого сумматора напряжений, входы которого подключены к выходам пропорционального звена и интегратора, входы пропорционального звена и интегратора объединены; формирователь напряжения, имеющий два раздельных входа, первый из которых подключен к входу сброса первого обнуляемого интегратора, а второй вход соединен с входом обнуления второго обнуляемого интегратора, объединенные первые входы обнуляемых интеграторов подключены к выходу формирователя напряжения, выходы первого и второго обнуляемых интеграторов раздельно подключены к входам второго сумматора напряжений, выход которого подключен ко вторым входам обнуляемых интеграторов, отличающееся тем, что в него введен знакомодульный логический фазовый дискриминатор с зоной нечувствительности по модульному каналу, первый вход которого является входом устройства, а второй вход через дополнительно введенный делитель частоты соединен с выходом управляемого генератора, знаковые выходы дискриминатора раздельно подключены к входам формирователя, также введен дополнительный формирователь напряжения, входы которого раздельно подключены к модульным выходам дискриминатора, выход дополнительного формирователя подключен к первому входу дополнительного сумматора напряжений, второй вход которого подключен к выходу второго сумматора напряжений, а выход дополнительного сумматора соединен с объединенными входами интегратора и пропорционального звена.