Устройство для определения параметров стратегии технического обслуживания средств системы

Иллюстрации

Показать всеТехническое решение относится к устройствам контроля, в которых требуется определять стратегию технического обслуживания средств системы, обеспечивающую требуемую их готовность к применению по назначению. Технический результат заключается в повышении точности за счет учета разности значений интенсивности отказов средств при изменении режима их функционирования. Устройство содержит: первый блок памяти 1, в который поступают с 1-7 входы устройства исходные данные, второй блок памяти 27, где сохраняется оптимальное значение периода технического обслуживания наиболее сложного средства системы, сдвиговый регистр 2, элементы задержки 3, 17, 18, 25, 35, вентили 4, 6, 19, ждущий мультивибратор 7, схемы ИЛИ 8, 12, накапливающие сумматоры 9, 11, блоки нелинейностей 10, 14, 20, 22, триггер 13, блоки умножения 15, 16, 24, 28, 37, блоки деления 34, 36, интеграторы 9, 11, вычитатели 21, 23, компаратор 26, интеграторы 30, 32, сумматоры 5, 31, 33 и счетчик 29. 2 ил.

Реферат

Изобретение относится к вычислительной технике, в частности к устройствам контроля. Оно может быть использовано в научных исследованиях и практике эксплуатации технических систем для определения периодов обслуживания, обеспечивающих требуемую готовность средств системы к применению и ритмичность их технического обслуживания.

Существуют устройства [3, 4], позволяющие определять оптимальные периоды технического обслуживания средств систем. Область их применения ограничена системами непрерывного применения. Известны устройства [5, 6], обеспечивающие определение оптимальных периодов контроля и управления техническим состоянием изделий с переменным режимом их использования. Область применения указанных устройств ограничена изделиями, не входящими непосредственно в состав сложных комплексов.

Наиболее близким по технической сущности к заявляемому изобретению является устройство [6], содержащее блок памяти, шесть вентилей, два накапливающих сумматора, четыре блока нелинейностей, два интегратора, пять сумматоров, два вычитателя, четыре блока умножения, блок деления, схему ИЛИ, мультивибратор, четыре элемента задержки, два триггера, компаратор и четыре элемента памяти. Как уже отмечено, область применения данного устройства ограничена функционально обособленными изделиями.

Целью заявляемого технического решения является расширение функциональных возможностей и области применения устройства. Цель достигается путем введения в схему прототипа ряда функциональных элементов, обеспечивающих определение периодов обслуживания средств системы, позволяющих формировать рациональную временную программу технического обслуживания системы в целом.

Система, как известно, включает в себя совокупность средств с номерами i=1, …, n, находящихся в отношениях и связях друг с другом, образующих определенную целостность, единство. Количественные показатели надежности и ремонтопригодности средств системы различны, поэтому и оптимальные сроки их обслуживания разные.

Каждое средство непрерывно расходует свой надежностный потенциал, причем скорость расходования зависит от режима использования средства [1]. Изменение режима проявляется в изменении интенсивности отказов. Это необходимо учитывать при определении оптимальных сроков технического обслуживания средств.

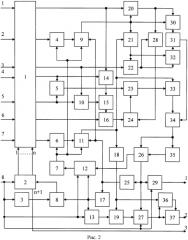

Процесс применения различных систем имеет циклический характер. Каждый цикл может включать в себя работу средств в номинальном режиме, в облегченном режиме, а также в режиме отдыха. На рисунке 1 представлена обобщенная диаграмма процесса эксплуатации средств системы. Каждому средству соответствует длительность цикла τ применения, в течение которого t1 - длительность применения средства в номинальном режиме с коэффициентом нагрузки kн=1. При этом интенсивность отказов средства имеет значение λ1i, где i - номер средства. На интервале t2=τ-t1 различные системы, в зависимости от технологии их применения и реальной нагрузки, могут находиться в одном из следующих режимов:

а) облегченный режим в связи с уменьшением нагрузки (например, средства энергосистем непрерывного использования);

б) отдых после применения (например, технические средства предприятий, работающих в одну или две смены).

В связи с этим на интервале времени t2 интенсивность отказов λ2i будет иметь разные значения λ2i=λ1ikн соответственно изменению коэффициента нагрузки kн. Отметим, что согласно [2] в случае облегченного режима работы средств kн<1, а в режиме отдыха согласно [1] 0<kн<<1.

Для поддержания системы в работоспособном состоянии периодически проводится техническое обслуживание каждого из ее средств и затрачивается время τобсi. При этом выполняется углубленный контроль состояния в течение времени τк1i, проведение профилактических работ и восстановление работоспособности в случае обнаружения отказов, на что расходуется время τвi, а по окончании этих работ проводится контрольная проверка состояния средства в течение времени τк2i. Отметим, что контроль технического состояния выполняется в условиях номинального режима работы. Поэтому на интервалах времени τк1i и τк2i интенсивность отказов будет равной λ1i. Для проведения профилактических и ремонтно-восстановительных работ средства переводятся в режим отдыха, что соответствует интенсивности отказов λ2i. В связи с этим общая продолжительность профилактических работ каждого средства выражается так:

или

где - вероятность безотказной работы i-го средства системы на соответствующем интервале времени.

Длительность периода обслуживания Ti включает в себя множество циклов применения длительностью τj, j=1, …, m каждый, то есть

где

Продолжительность Tцi цикла обслуживания i-го средства составляет

Вероятность безотказной работы средства на интервале времени Ti выражается так

Для многих систем справедливо утверждение, что в них преобладают внезапные отказы, и каждому средству соответствует экспоненциальный закон распределения времени возникновения отказов. При этом имеет место следующее:

Время работоспособного состояния средства системы Τфi на интервале времени Ti определяется по формуле

Комплексным показателем качества функционирования средств является коэффициент технического использования (аналог коэффициента готовности). Его значение выражается следующим соотношением

Анализ функции Kг(Т) показывает, что при Τ→0 и при Τ→∞ функция Kг(Т)→0. Существует период технического обслуживания Т*, при котором коэффициент готовности имеет максимальное значение K* г. Каждому из средств системы соответствует индивидуальный оптимальный период T* i технического обслуживания. Множество значений Τ* i, соответствующее множеству средств системы, образует во времени такую совокупность циклов обслуживания, что практическая ее реализация окажется нерациональной, либо невозможной. Поэтому возникает необходимость упорядочивания этой совокупности путем нахождения компромиссных, близких к оптимальным значений периодов обслуживания для каждого средства системы. Конструктивным вариантом упорядочивания является обеспечение кратности периодов обслуживания средств и выполнение условия

где T* min - оптимальный период технического обслуживания, обеспечивающий max Kг(Т) наименее надежного средства системы;

Начало каждого интервала времени qiT* min будет соответствовать началу цикла обслуживания одного или нескольких близких по надежности средств системы. Отдельное средство будет обслуживаться с периодом, близким к оптимальному. Поскольку периоды обслуживания отдельных средств находятся из условия кратности, то этим обеспечивается рациональное в организационном плане обслуживание средств системы в целом.

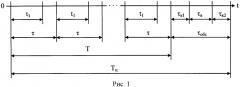

Предложенная модель может быть реализована аппаратурно с помощью предлагаемого устройства, схема которого представлена на рисунке 2.

Устройство содержит: первый блок памяти 1, в который поступают с 1-7 входы устройства исходные данные, сдвиговый регистр 2, элементы задержки 3, 17, 18, 25, 35, вентили 4, 6, 19, ждущий мультивибратор 7, схемы ИЛИ 8, 12, накапливающие сумматоры 9, 11, блоки нелинейностей 10, 14, 20, 22, триггер 13, блоки умножения 15, 16, 24, 28, 37, блоки деления 34, 36, интеграторы 9, 11, вычитатели 21, 23, компаратор 26, второй блок памяти 27, интеграторы 30, 32, сумматоры 5, 31, 33 и счетчик 29.

Перед началом работы устройства исходные данные (значения вводных величин): λ1i, t1i, λ2i, (τк1i+τк2i), τвi, (τк2i+τвi), τ заносятся в первый блок памяти 1 через его входы 1-7 соответственно. Отметим, что блок памяти 1 разделен на n зон по возможному количеству средств системы.

Устройство работает следующим образом.

По сигналу «Пуск», поступающему с восьмого входа устройства, сдвиговый регистр 2 обнуляется. Этот же сигнал, задержанный первым элементом задержки 3, пройдя через первую схему ИЛИ 8, устанавливает единицу в первом разряде сдвигового регистра 2, обеспечивая считывание значений входных величин, соответствующих первому (наиболее сложному и наименее надежному) средству системы, из первого блока памяти 1 на сопряженные с ним функциональные элементы устройства. Кроме того, сигнал «Пуск» устанавливает триггер 13 в единичное состояние, второй блок памяти 27 и счетчик 29 обнуляются, а, пройдя через вторую схему ИЛИ 12, поступает на вход мультивибратора 7. По сигналу сдвигового регистра 2 считываются значения входных величин, соответствующие первому средству системы, из первого блока памяти 1 на сопряженные с ним функциональные элементы устройства. По выходному (единичному) сигналу мультивибратора 7 открываются первый 4 и второй 6 вентили. Это обеспечивает однократное поступление значений параметра t1 со второго выхода блока памяти 1 в первый накапливающий сумматор 9, а значения параметра τ - с седьмого выхода блока памяти 1 во второй накапливающий сумматор 11. Одиночный сигнал мультивибратора 7 поступает также на управляющие входы первого 9 и второго 11 накапливающих сумматоров, обеспечивая реализацию ими процесса накопления и передачи результирующих данных в сопряженные с ними элементы схемы устройства (схема и порядок работы накапливающего сумматора показаны в патенте №2233482, 2004 г., G07C 3/08).

Выходной сигнал первого накапливающего сумматора 9 передается на вторые входы третьего блока нелинейности 20, первого интегратора 30 и первого вычитателя 21. Выходной сигнал второго накапливающего сумматора 11 поступает на вход третьего элемента задержки 18, а также на первые входы первого вычитателя 21 и третьего сумматора 33. В вычитателе 21 реализуется разность t2=τ-t1 и передается на вторые входы четвертого блока нелинейности 22 и второго интегратора 32. С первого выхода первого блока памяти 1 на первые входы второго 14 и третьего 20 блоков нелинейностей передается значение λ1 интенсивности отказов, а с третьего выхода блока памяти 1 на первый вход четвертого блока нелинейности 22 и на второй вход первого блока нелинейности 10 поступает значение интенсивности отказов λ2. В третьем блоке нелинейности 20 формируется в соответствии с (6) сигнал P1(t1) и передается на первые входы четвертого блока умножения 28 и первого интегратора 30. В четвертом блоке нелинейности 22 в соответствии с (7) формируется сигнал P2(t2) и передается на первый вход второго интегратора 32 и на второй вход четвертого блока умножения 28. В первом интеграторе 30 вычисляется время работоспособного состояния tф1(t1), а во втором интеграторе 32 - время работоспособного состояния tф2(t2). Выходные сигналы интеграторов 30 и 32 поступают соответственно на первый и второй входы второго сумматора 31. Суммарное значение tф(τ), полученное в соответствии с (10), с выхода второго сумматора 31 передается на второй вход первого блока деления 34.

Одновременно с изложенным происходит вычисление величины τобс. При этом с четвертого выхода блока памяти 1 на второй вход второго блока нелинейности 14 и на первый вход первого сумматора 5 поступает значение τк1+τк2. С пятого выхода блока памяти 1 значение величины τв передается на второй вход первого сумматора 5 и на первый вход первого блока нелинейности 10. Выходной сигнал сумматора 5, соответствующий сумме τк1+τк2+τв, поступает на первый вход второго вычитателя 23. В блоках нелинейностей 10 и 14 формируются значения величин Ρ(τв) и Ρ(τк1+τк2) соответственно. Выходные сигналы этих блоков нелинейности поступают на входы первого блока умножения 15. Результат перемножения Ρ(τв)Ρ(τк1+τк2) из блока 15 передается на второй вход второго блока умножения 16, на первый вход которого с шестого входа первого блока памяти 1 поступает значение суммы τв+τк2. Выходной сигнал блока 16 передается на второй вход третьего блока умножения 24, на первый вход которого от четвертого блока умножения 28 приходит сигнал, соответствующий согласно (5) величине Ρ(τ)=P1(t1)P2(t2). В третьем блоке умножения 24 реализуется произведение его входных величин и передается на второй вход второго вычитателя 23. В вычитателе 23 формируется значение величины τобс, отображаемой соотношением (1), и передается на второй вход третьего сумматора 33. Сигнал, соответствующий сумме τ+τобс, из сумматора 33 поступает в первый блок деления 34 через его первый вход. Результат деления, соответствующий вычисленному согласно (11) коэффициенту готовности Kг, с выхода блока делений 34 поступает непосредственно на первый вход, а через пятый элемент задержки 35 на второй вход компаратора 26. В начале работы устройства всегда выполняется неравенство Κrj(τ)>Krj-1(τ). Поэтому управляющий сигнал появится на первом выходе компаратора 26 и через вторую схему ИЛИ 12 поступит в мультивибратор 7. Одиночный выходной импульс мультивибратора 7 откроет первый 4 и второй 6 вентили. В результате этого значения выходных величин первого 9 и второго 11 накапливающих сумматоров увеличатся на t1 и τ соответственно. Далее процесс вычисления коэффициента готовности Krj(T) и сравнения его с Krj-1(T) повторится, но при обновленных в соответствии с (10), (2), (1) значениях величин Τфi, Ti, τобсi. Как только в компараторе 26 окажется, что очередное значение коэффициента готовности меньше предыдущего, управляющий сигнал возникнет на втором выходе компаратора 26 и поступит на вход четвертого элемента задержки 25, на второй (разрешающий) вход второго блока памяти 27 и на вход счетчика 29. В то же время выходной сигнал третьего элемента задержки 18, соответствующий оптимальному значению периода обслуживания средства, поступит непосредственно на первый (информационный) вход блока деления 36, а через третий вентиль 19 - во второй блок памяти 27. Выходной сигнал блока 27 поступает в блок деления 36 и блок умножения 37. На данном этапе работы устройства значения входных сигналов блока деления 36 равнозначны, поэтому с его выхода на первый вход пятого блока умножения 37 поступит сигнал, соответствующий единице. В результате на выход блока умножения 37, являющийся вторым выходом устройства, поступит оптимальное значение периода обслуживания первого устройства системы. На выходе счетчика 29, являющемся первым выходом устройства, будет сигнал, соответствующий первому средству системы.

Одновременно с изложенным сигнал компаратора 26 с его второго выхода через четвертый элемент задержки 25 поступит на вход второго элемента задержки 17, а также на входы «сброс в ноль» первого 9 и второго 11 накапливающих сумматоров, подготавливая их к работе по очередному средству системы. Выходной сигнал элемента задержки 17 переключает триггер 13 в нулевое состояние, а, пройдя через схему ИЛИ 8, переводит сдвиговый регистр 2 на считывание исходных данных из блока памяти 1, соответствующих следующему средству системы. Кроме того, выходной сигнал элемента задержки 17 через схему ИЛИ 12 передается на вход мультивибратора 7, в результате чего с его выхода управляющий сигнал поступит на управляющие входы первого 4 и второго 6 вентилей, а также первого 9 и второго 11 накапливающих сумматоров. Далее процесс определения оптимального периода технического обслуживания данного средства аналогичен рассмотренному выше.

С появлением сигнала на втором выходе компаратора 26 значение выходного сигнала счетчика 29 увеличивается на единицу, оптимальное значение периода обслуживания первого средства системы из второго блока памяти 27 поступит на вторые входы блока деления 36 и блока умножения 37. Оптимальное значение периода обслуживания данного средства с выхода элемента задержки 18 передается в блок деления 36 через его первый вход. Результат деления нацело, полученный в соответствии с (13), с выхода блока 36 передается на первый вход блока умножения 37. Вычисленное значение периода обслуживания Тi=qiT* min с выхода блока 37 поступит на второй выход устройства.

Аналогично изложенному будут определены значения выходных величин всех средств системы. После завершения последнего цикла работы устройства управляющий сигнал появится в n+1 разряде регистра 2, который обеспечит индикацию конца работы. Выход этого разряда является третьим выходом устройства.

На этом работа устройства заканчивается.

Положительный эффект, который может быть получен от использования предлагаемого технического решения, состоит в том, что устройство позволяет на основе принципа кратности определять периоды технического обслуживания средств сложной системы, вычисленных с учетом переменного режима их использования. Практическая реализация предложенного решения является рациональной с точки зрения организации обслуживания и расходования материального и временного ресурсов на техническое обслуживание системы, а также использования надежностных ресурсов средств, составляющих систему. Вычисленные значения периодов обслуживания позволяют обоснованно планировать применение и техническую эксплуатацию системы.

Источники информации

1. Седякин Н.М. Об одном физическом принципе теории надежности. - Известия АН СССР, ОТН, Техническая кибернетика, 1966, №3.

2. Половко А.М. Основы теории надежности. - М.: Наука, 1964.

3. Гришин В.Д., Соколов Б.В., Петрова И.А. Патент РФ №2429542. МПК G07C 3/08, G05B 23/02, 2011.

4. Гришин В.Д., Соколов Б.В., Иконникова А.В. Патент РФ №2429543. МПК G07C 3/08, G06F 11/30, G06F 17/00, 2011.

5. Соколов Б.В., Гришин В.Д., Зеленцов В.А., Цивирко Е.Г. Патент РФ №2476934. МПК G07C 3/08, 2013.

6. Соколов Б.В., Гришин В.Д., Зеленцов В.А., Майданович О.В. Патент РФ №2479041. МПК G07C 3/08, 2013.

7. Тетельбаум И.М., Шрейдер Ю.Р. 400 схем для ABM. - М.: Энергия, 1978.

Устройство для определения параметров стратегии технического обслуживания средств системы, содержащее первый и второй элементы задержки, третий вентиль, первый блок памяти, информационные входы которого с 1 по 7 являются соответствующими входами устройства, а первый выход соединен с первыми входами второго блока нелинейности и третьего блока нелинейности, выход которого подключен к первым входам четвертого блока умножения и первого интегратора, выход которого связан с первым входом второго сумматора, а второй вход - со вторыми входами третьего блока нелинейности и первого вычитателя, а также с выходом первого накапливающего сумматора, первый вход которого соединен с выходом первого вентиля, первый вход которого подключен ко второму выходу первого блока памяти, а второй вход, вместе со вторым входом первого накапливающего сумматора, к выходу мультивибратора и ко вторым входам второго накапливающего сумматора и второго вентиля, первый вход которого соединен с седьмым выходом первого блока памяти, а выход связан с первым входом второго накапливающего сумматора, выход которого подключен к входу третьего элемента задержки и к первому входу первого вычитателя, выход которого соединен со вторыми входами второго интегратора и четвертого блока нелинейности, первый вход которого соединен с третьим выходом первого блока памяти и со вторым входом первого блока нелинейности, а выход со вторым входом четвертого блока умножения и с первым входом второго интегратора, выход которого подключен ко второму входу второго сумматора, выход которого соединен со вторым входом первого блока деления, первый вход которого подключен к выходу третьего сумматора, а выход ко входу пятого элемента задержки и к первому входу компаратора, первый вход которого соединен со вторым входом второй схемы ИЛИ, выход которой связан с входом мультивибратора, а первый вход с первым входом триггера и с восьмым входом устройства, пятый выход первого блока памяти соединен со вторым входом первого сумматора и с первым входом первого блока нелинейности, выход которого подключен к первому входу первого блока умножения, второй вход которого соединен с выходом второго блока нелинейности, а выход со вторым входом второго блока умножения, выход которого связан со вторым входом третьего блока умножения, первый вход которого подключен к выходу четвертого блока умножения, а выход ко второму входу второго вычитателя, первый вход которого соединен с выходом первого сумматора, а выход со вторым входом третьего сумматора, отличающееся тем, что в него введены сдвиговый регистр, первая схема ИЛИ, четвертый элемент задержки, суммирующий счетчик, второй блок деления, второй блок памяти, пятый блок умножения, при этом восьмой вход устройства соединен с входом первого элемента задержки, с первым входом суммирующего счетчика, с входом «сброс в ноль» второго блока памяти и с первым входом сдвигового регистра, второй вход которого подключен к выходу первой схемы ИЛИ, первый вход которой связан с выходом первого элемента задержки, а второй вход соединен с третьим входом второй схемы ИЛИ, со вторым входом триггера и с выходом второго элемента задержки, вход которого подключен к входам «сброс в ноль» первого и второго накапливающих сумматоров, а также к выходу четвертого элемента задержки, вход которого соединен со вторым выходом компаратора, со вторыми входами второго блока памяти и суммирующего счетчика, выход которого является первым выходом устройства, вторым выходом которого является выход пятого блока умножения, второй вход которого соединен с выходом второго блока памяти и со вторым входом второго блока деления, а первый вход с выходом второго блока деления, первый вход которого подключен к выходу третьего элемента задержки и к информационному входу третьего вентиля, управляющий вход которого соединен с выходом триггера, а выход с первым входом второго блока памяти, третьим выходом устройства является n+1 выход сдвигового регистра, с 1 по n выходы которого соединены с соответствующими им управляющими входами первого блока памяти, четвертый выход которого подключен ко второму входу второго блока нелинейности и к первому входу первого сумматора, а шестой выход к первому входу второго блока умножения, выход второго накапливающего сумматора соединен с первым входом третьего сумматора, а выход пятого элемента задержки со вторым входом компаратора.