Цифровой вычислительный синтезатор частотно-модулированных сигналов

Иллюстрации

Показать всеИзобретение относится к электронно-вычислительной технике и радиотехнике, предназначено для синтеза сложных частотно-модулированных сигналов и может быть использовано в радиолокации и системах связи. Достигаемый технический результат - повышение быстродействия и возможность оперативного управления начальной частотой синтезируемого частотно-модулированного сигнала. Цифровой вычислительный синтезатор (ЦВС) частотно-модулированных сигналов содержит эталонный генератор, блок формирования и задержки, ждущий мультивибратор, первый и второй регистры памяти, мультиплексор, первый и второй цифровые накопители, функциональный преобразователь код-синус, цифроаналоговый преобразователь, фильтр нижних частот, третий регистр памяти и делитель с переменным коэффициентом деления. 2 ил.

Реферат

Изобретение относится к электронно-вычислительной технике и радиотехнике, предназначено для синтеза сложных частотно-модулированных сигналов и может быть использовано в радиолокации и системах связи.

Известны цифровые синтезаторы частот, содержащие эталонный генератор, блок формирования и задержки, два регистра памяти, два счетчика с предварительной установкой, умножитель кодов, цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот, третий регистр памяти, делитель с переменным коэффициентом деления [1].

Наиболее близким техническим решением (прототипом) является цифровой синтезатор фазомодулированных сигналов, содержащий эталонный генератор и блок задержки, ждущий мультивибратор, три регистра памяти, два цифровых накопителя, преобразователь кодов, сумматор, два цифроаналоговых преобразователя, два фильтра нижних частот, делитель с переменным коэффициентом деления [2].

Однако известные цифровые синтезаторы не позволяют оперативно управлять начальной частотой синтезированного сигнала.

Положительный технический результат - повышение быстродействия и возможность оперативного управления начальной частотой синтезируемого частотно-модулированного сигнала - достигается за счет того, что в цифровой вычислительный синтезатор частотно-модулированных сигналов, содержащий последовательно соединенные эталонный генератор и блок формирования и задержки; первый и второй регистры памяти; последовательно соединенные первый и второй цифровые накопители, функциональный преобразователь код-синус, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является аналоговым выходом цифрового вычислительного синтезатора; последовательно соединенные третий регистр памяти, делитель с переменным коэффициентом деления и вход последовательного переноса первого цифрового накопителя; ждущий мультивибратор, вход которого является входом запуска цифрового вычислительного синтезатора, а его выход подключен к входам установки первого и второго цифровых накопителей и делителя с переменным коэффициентом деления; информационными цифровыми входами цифрового вычислительного синтезатора являются входы первого, второго и третьего регистров памяти, выходы блока формирования и задержки подключены к тактовым входам первого и второго цифровых накопителей, делителя с переменным коэффициентом деления и цифроаналогового преобразователя, согласно изобретению введен мультиплексор, выход которого подключен к входу первого цифрового накопителя; выходы первого и второго регистров памяти подключены к первому и второму входам мультиплексора соответственно; вход переключения мультиплексора является управляющим входом цифрового вычислительного синтезатора.

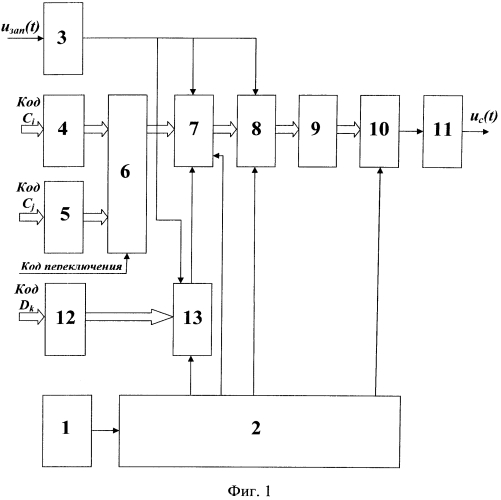

Цифровой вычислительный синтезатор частотно-модулированных сигналов содержит (фиг.1) эталонный генератор 1 и блок формирования и задержки 2, ждущий мультивибратор 3; первый и второй регистры памяти 4,5; мультиплексор 6; первый и второй цифровые накопители 7 и 8; функциональный преобразователь код-синус 9; цифроаналоговый преобразователь (ЦАП) 10; фильтр нижних частот (ФНЧ) 11; третий регистр памяти 12; делитель с переменным коэффициентом деления 13.

Цифровой вычислительный синтезатор частотно-модулированных сигналов содержит (фиг.1) последовательно соединенные эталонный генератор 1 и блок формирования и задержки 2, ждущий мультивибратор 3, вход которого является входом запуска ЦВС; первый и второй регистры памяти 4, 5, выходы которых подключены к первому и второму входам мультиплексора 6 соответственно; последовательно соединенные мультиплексор 6, первый и второй цифровые накопители 7 и 8, функциональный преобразователь код-синус 9, цифроаналоговый преобразователь (ЦАП) 10 и фильтр нижних частот (ФНЧ) 11; последовательно соединенные третий регистр памяти 12, делитель с переменным коэффициентом деления 13 и вход последовательного переноса первого цифрового накопителя 7; выход ждущего мультивибратора 3 подсоединен к входам установки первого и второго цифровых накопителей 7, 8 и делителя с переменным коэффициентом деления 13; выходы блока формирования и задержки 2 подключены к тактовым входам первого и второго цифровых накопителей 7, 8, цифроаналогового преобразователя 10 и делителя с переменным коэффициентом деления 13; цифровыми входами ЦВС являются входы первого, второго и третьего регистров памяти 4, 5 и 12, а его управляющим входом - вход переключения мультиплексора 6, аналоговым выходом цифрового вычислительного синтезатора является выход фильтра нижних частот 11.

Цифровой синтезатор работает следующим образом:

На информационные входы первого, второго, третьего регистров памяти 4, 5, 12 поступают коды Ci, Cj, Dk, которые соответственно будут определять начальную частоту и скорость изменения частоты синтезируемого сигнала. На управляющий вход мультиплексора 6 поступает код переключения К.

Эталонный генератор 1 вырабатывает синусоидальный сигнал опорной частоты, из которого в блоке формирования и задержки 2 формируются тактовые импульсы прямоугольной формы, разнесенные во времени и служащие для синхронизации работы узлов цифрового вычислительного синтезатора: делителя с переменным коэффициентом деления 13, первого и второго цифровых накопителей 7, 8 и цифроаналогового преобразователя 10.

Пусть код переключения К=0, тогда код Сi с выхода первого регистра памяти 4 поступит на выход мультиплексора 6.

В момент времени t1 (фиг.2) на вход ждущего мультивибратора 3 приходит импульс запуска uзап(t), из которого формируется импульс установки, который поступает на установочные входы первого и второго цифровых накопителей 7, 8 и делителя с переменным коэффициентом деления 13. При этом код Ci из первого регистра памяти 4 через мультиплексор 6 записывается в первый цифровой накопитель 7, а код Dk из третьего регистра памяти 12 - в делитель с переменным коэффициентом деления 13.

Затем с каждым последующим тактовым импульсом в моменты времени t2, t3 t4 и т.д. на выходе цифрового накопителя 7 код суммы А будет изменяться по формуле:

где Ci - код начальной частоты синтезируемого сигнала, Dk - код, определяющий коэффициент деления делителя с переменным коэффициентом деления: T=Δt - номер тактового импульса.

Код суммы А с выхода первого цифрового накопителя 7 поступает на вход второго цифрового накопителя 8, результат суммирования В в котором можно описать выражением:

В функциональном преобразователе 9 коду В ставится в соответствие код sin(B), который поступает на информационный вход цифроаналогового преобразователя (ЦАП) 10, где формируется ступенчатый частотно-модулированный сигнал «синусоидальной» формы.

Сигнал с выхода ЦАП 10 поступает на фильтр нижних частот 11, который служит для подавления побочных высокочастотных спектральных составляющих в спектре синтезируемого сигнала. Фильтр нижних частот 11 имеет частоту среза, равную половине тактовой частоты fcp=0,5fm.

Если принять, что 2πf0=Ci - начальная частота; πf'=1/Dk - скорость изменения частоты синтезируемого сигнала, Δt=Т - период следования тактовых импульсов, то сигнал на выходе цифрового вычислительного синтезатора можно описать следующим выражением:

где U0 - амплитуда сигнала.

Далее, если в момент времени tn на вход ждущего мультивибратора 3 придет следующий импульс запуска, а перед этим установить код переключения мультиплексора 6 на К=1, то на выход мультиплексора 6 пройдет код Cj из второго регистра памяти 5. По импульсу установки произойдет запись кода Cj в первый цифровой накопитель 7, и это приведет к изменению начальной частоты синтезируемого сигнала (фиг.2).

Если обозначить, что 2πf1=Cj - начальная частота синтезируемого сигнала, то сигнал на выходе цифрового вычислительного синтезатора в моменты времени tn, tn+j, fn+2 и т.д. можно описать выражением:

Таким образом, в данном цифровом вычислительном синтезаторе появилась возможность оперативно управлять начальной частотой синтезируемого сигнала, подавая на управляющий вход мультиплексора 6 соответствующий код переключения К.

Время переключения с одной начальной частоты на другую в основном будет определяться задержкой переключения в мультиплексоре 6, так как коды начальных частот предварительно записаны в первый и второй регистры памяти 4 и 5. Скорость изменения частоты синтезируемого частотно-модулированного сигнала можно изменять, задавая код Dk в третьем регистре памяти 12. Чем больше значение Dk, тем меньше скорость изменения частоты синтезируемого частотно-модулированного сигнала.

Литература

1. Патент РФ №2491710, МПК Н03В 19/00, H03L 7/18. Цифровой вычислительный синтезатор с быстрой перестройкой частоты / Рябов И.В., Дедов А.Н., Петухов И.В. Заявл. 03.07.2012. Опубл. 27.08.2013. Бюл. №24. - 5 с.

2. Патент №2490789 Российской Федерации, МПК H03L 7/00. Цифровой синтезатор фазомодулированных сигналов / Рябов И.В., Дедов А.Н., Толмачев С.В. Заявл. 06.07.2012. Опубл. 27.08.2013. Бюл. №23. - 7 с. (прототип).

Цифровой вычислительный синтезатор частотно-модулированных сигналов, содержащий последовательно соединенные эталонный генератор и блок формирования и задержки; первый и второй регистры памяти; последовательно соединенные первый и второй цифровые накопители, функциональный преобразователь код-синус, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является аналоговым выходом цифрового вычислительного синтезатора; последовательно соединенные третий регистр памяти, делитель с переменным коэффициентом деления и вход последовательного переноса первого цифрового накопителя; ждущий мультивибратор, вход которого является входом запуска цифрового вычислительного синтезатора, а его выход подключен к входам установки первого и второго цифровых накопителей и делителя с переменным коэффициентом деления; информационными цифровыми входами цифрового вычислительного синтезатора являются входы первого, второго и третьего регистров памяти, выходы блока формирования и задержки подключены к тактовым входам первого и второго цифровых накопителей, делителя с переменным коэффициентом деления и цифроаналогового преобразователя, отличающийся тем, что введен мультиплексор, выход которого подключен к входу первого цифрового накопителя; выходы первого и второго регистров памяти подключены к первому и второму входам мультиплексора соответственно; вход переключения мультиплексора является управляющим входом цифрового вычислительного синтезатора.