Мультидифференциальный операционный усилитель с малым напряжением смещения нуля

Иллюстрации

Показать всеИзобретение относится к прецизионным устройствам усиления сигналов различных сенсоров. Технический результат заключается в уменьшении абсолютного значения Uсм, а также его температурных и радиационных изменений, обусловленных дрейфом β транзисторов. Мультидифференциальный операционный усилитель с малым напряжением смещения нуля содержит транзисторы, масштабирующий резистор, высокоимпедансный узел 4, третий 5 и четвертый 6 входные транзисторы, токовое зеркало 8, согласованное с первой 9 шиной источника питания, вспомогательный транзистор 18, эмиттером связанный со второй 12 шиной источника питания через четвертый 19 вспомогательный токостабилизирующий двухполюсник, а коллектор соединен с эмиттером четвертого 6 входного транзистора, причем базы третьего 16 и четвертого 18 вспомогательных транзисторов подключены к источнику напряжения смещения 20. Базы первого 11 и второго 14 вспомогательных транзисторов соединены с эмиттером третьего 16 вспомогательного транзистора. 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в измерительной технике в качестве прецизионного устройства усиления сигналов различных сенсоров.

В современной радиоэлектронной аппаратуре находят применение мультидифференциальные операционные усилители (МОУ) на биполярных транзисторах [1-12]. На их основе реализуется новый класс устройств преобразования и усиления сигналов [13-18].

В связи с особенностями архитектуры МОУ [13-18] в них подчеркивается влияние нестабильности коэффициента усиления по току базы транзисторов (β) на напряжение смещения нуля (Uсм), что отрицательно сказывается на прецизионности МОУ.

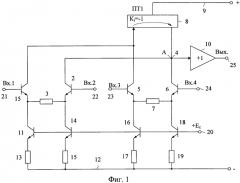

Наиболее близким по сущности к заявляемому техническому решению является классическая схема МОУ фиг. 1, представленная в Каталоге разработок Российско-Белорусского центра аналоговой микросхемотехники / редкол.: Н.Н. Прокопенко, С.Г. Крутчинский, Е.И. Старченко [и др.]; под ред. Н.Н. Прокопенко. - Шахты: ГОУ ВПО «ЮРГУЭС», 2010. - С.134. 1435-stat-2010-05, которая также присутствует в других источниках [15].

Существенный недостаток известного МОУ фиг. 1 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), зависящей от температурного и радиационного дрейфа коэффициента усиления по току базы (β) транзисторов.

Основная задача предлагаемого изобретения состоит в уменьшении абсолютного значения Uсм, а также его температурных и радиационных изменений, обусловленных дрейфом β транзисторов.

Поставленная задача достигается тем, что в мультидифференциальном операционном усилителе фиг. 1, содержащем первый 1, второй 2 входные транзисторы, между эмиттерами которых включен первый 3 масштабирующий резистор, высокоимпедансный узел 4, третий 5 и четвертый 6 входные транзисторы, между эмиттерами которых включен второй 7 масштабирующий резистор, токовое зеркало 8, согласованное с первой 9 шиной источника питания, вход которого связан с коллекторами первого 1 и третьего 5 входных транзисторов, а выход подключен ко входу буферного усилителя 10 и объединенным коллекторам второго 2 и четверного 6 входных транзисторов, первый 11 вспомогательный транзистор, эмиттер которого связан со второй 12 шиной источника питания через первый 13 вспомогательный токостабилизирующий двухполюсник, а коллектор соединен с эмиттером первого 1 входного транзистора, второй 14 вспомогательный транзистор, эмиттер которого связан со второй 12 шиной источника питания через второй 15 вспомогательный токостабилизирующий двухполюсник, а коллектор соединен с эмиттером второго 2 входного транзистора, причем базы первого 11 и второго 14 вспомогательных транзисторов соединены друг с другом, третий 16 вспомогательный транзистор, эмиттер которого связан со второй 12 шиной источника питания через третий 17 вспомогательный токостабилизирующий двухполюсник, а коллектор соединен с эмиттером третьего 5 входного транзистора, четвертый 18 вспомогательный транзистор, эмиттер которого связан со второй 12 шиной источника питания через четвертый 19 вспомогательный токостабилизирующий двухполюсник, а коллектор соединен с эмиттером четвертого 6 входного транзистора, причем, базы третьего 16 и четвертого 18 вспомогательных транзисторов подключены к источнику напряжения смещения 20, предусмотрены новые элементы и связи - базы первого 11 и второго 14 вспомогательных транзисторов соединены с эмиттером третьего 16 вспомогательного транзистора.

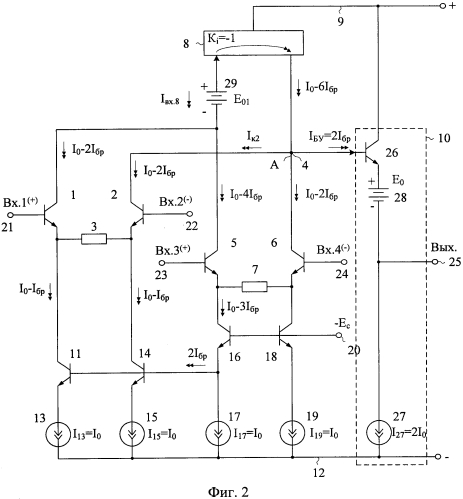

Схема усилителя-прототипа показана на чертеже фиг. 1. На чертеже фиг. 2 представлена схема заявляемого устройства в соответствии с формулой изобретения.

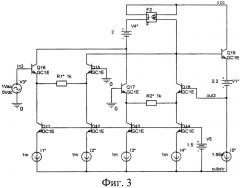

На чертеже фиг. 3 приведена схема МОУ-прототипа фиг. 1 в среде PSpice на моделях интегральных транзисторов НПО «Интеграл» (г. Минск).

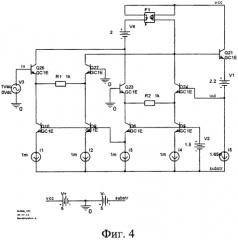

На чертеже фиг. 4 показана схема заявляемого МОУ фиг. 2 в среде PSpice на моделях интегральных транзисторов НПО «Интеграл» (г. Минск).

На чертеже фиг. 5 представлены зависимости напряжений смещения нуля МОУ фиг. 3 и фиг. 4 от температуры.

На чертеже фиг. 6 показаны зависимости напряжений смещения нуля заявляемого (фиг. 4) и известного (фиг. 3) МОУ от потока нейтронов (н/м2).

Мультидифференциальный операционный усилитель с малым напряжением смещения нуля (фиг. 2) содержит первый 1, второй 2 входные транзисторы, между эмиттерами которых включен первый 3 масштабирующий резистор, высокоимпедансный узел 4, в котором происходит суммирование токов транзисторов схемы, третий 5 и четвертый 6 входные транзисторы, между эмиттерами которых включен второй 7 масштабирующий резистор, токовое зеркало 8, согласованное с первой 9 шиной источника питания, вход которого связан с коллекторами первого 1 и третьего 5 входных транзисторов, а выход подключен ко входу буферного усилителя 10 и объединенным коллекторам второго 2 и четверного 6 входных транзисторов, первый 11 вспомогательный транзистор, эмиттер которого связан со второй 12 шиной источника питания через первый 13 вспомогательный токостабилизирующий двухполюсник, а коллектор соединен с эмиттером первого 1 входного транзистора, второй 14 вспомогательный транзистор, эмиттер которого связан со второй 12 шиной источника питания через второй 15 вспомогательный токостабилизирующий двухполюсник, а коллектор соединен с эмиттером второго 2 входного транзистора, причем, базы первого 11 и второго 14 вспомогательных транзисторов соединены друг с другом, третий 16 вспомогательный транзистор, эмиттер которого связан со второй 12 шиной источника питания через третий 17 вспомогательный токостабилизирующий двухполюсник, а коллектор соединен с эмиттером третьего 5 входного транзистора, четвертый 18 вспомогательный транзистор, эмиттер которого связан со второй 12 шиной источника питания через четвертый 19 вспомогательный токостабилизирующий двухполюсник, а коллектор соединен с эмиттером четвертого 6 входного транзистора, причем базы третьего 16 и четвертого 18 вспомогательных транзисторов подключены к источнику напряжения смещения 20. Базы первого 11 и второго 14 вспомогательных транзисторов соединены с эмиттером третьего 16 вспомогательного транзистора. Входами 21 и 22 первого дифференциального каскада МОУ (транзисторы 1 и 2) являются базы соответствующих входных транзисторов. Входами 23 и 24 второго дифференциального каскада МОУ (транзисторы 5 и 6) являются базы соответствующих входных транзисторов 5 и 6. Выходом буферного усилителя 10 является узел 25, а его схема содержит (в частном случае) элементы 26, 27, 28. Двухполюсник 29 симметрирует статический режим МОУ и способствует дальнейшей минимизации Uсм.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля Uсм в схеме фиг. 2, т.е. зависящие от схемотехники МОУ.

Если токи токостабилизирующих двухполюсников 13, 15, 17, 19 одинаковы и равны некоторой величине Ι0, а двухполюсника 27 - величине 2I0, то токи эмиттеров и коллекторов транзисторов схемы:

где Iб.i.=Iэ.i/βi - ток базы n-p-n (Iб.р) транзисторов схемы при эмиттерном токе Iэ.i=I0;

βi - коэффициент усиления по току базы идентичных транзисторов схемы;

Iвх.8=Iвых.8 - входной и выходной токи токового зеркала 8.

Поэтому разность токов в узле «A» при его коротком замыкании на эквипотенциальную общую шину

где IБУ=2Iб.р - ток базы n-p-n транзистора 26 (входной ток буфера 10).

Таким образом, в заявляемом устройстве при выполнении условия (5) уменьшается систематическая составляющая Uсм, обусловленная конечной величиной β транзисторов и его радиационной (или температурной) зависимостью. Как следствие, это уменьшает Uсм, так как разностный ток Ip в узле «A» (4) создает Uсм, зависящее от крутизны S преобразования входного дифференциального напряжения uвх МОУ в выходной ток узла «A»:

где rэi - сопротивление эмиттерного перехода i-го входного транзистора 1, 2 (5, 6) входных дифференциальных каскадов. Поэтому для схемы фиг. 2 с учетом уравнения (5)

В МОУ-прототипе Ιρ≠0, поэтому здесь систематическая составляющая Uсм получается как минимум на порядок больше, чем в заявляемой схеме.

Компьютерное моделирование схем фиг. 3 и фиг. 4 подтверждает (фиг. 5, фиг. 6) данные теоретические выводы.

Несмотря на существенное уменьшение β транзисторов (на 70-90%) вследствие радиационных воздействий, а также низких температур предлагаемый МОУ и в этих условиях имеет меньшее напряжение смещения нуля, чем МОУ-прототип.

Замечательная особенность предлагаемой схемы - низкая чувствительность напряжения смещения нуля (Uсм) к одновременному изменению под действием температуры или радиации токов двухполюсников 13, 15, 17, 19, 27, устанавливающих статический режим транзисторов МОУ.

Включение двухполюсника 29 (фиг. 2) способствует симметрированию режимов работы входных дифференциальных каскадов (транзисторы 1, 2; 5, 6) по напряжению коллектор-база.

Амплитуда отрицательной полуволны выходного напряжения МОУ фиг. 2 определяется падением напряжения Е0 в статическом режиме на двухполюснике 28:

Однако для низковольтных применений допускается иметь Е0=0.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока и может использоваться в качестве IP-модулей современных систем на кристалле.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патентная заявка US 2008/0186091 fig. 4

2. Патент US №5.148.721

3. Патент US №5.237.526

4. Патент US №5.729.161 fig. 2

5. Патентная заявка US 2008/0032648 fig. 3

6. Патент US №5.045.804 fig. 5

7. Патент WO 03/043281 fig. 6

8. Патентная заявка US 2003/0184377

9. Ав.св. СССР 543946

10. Патент US №3.916.215

11. Патент US №4.599.572 fig. 2

12. Патент RU 2513489

13. Прокопенко Н.Н., Будяков А.С., Хорунжий А.В. Нелинейные режимы в мультидифференциальных операционных усилителях // Проблемы разработки перспективных микро- и наноэлектронных систем - 2008. Сборник научных трудов / под общ. ред. А.Л. Стемпковского. М.: ИППМ РАН, 2008. С. 340-343.

14. Прокопенко Н.Н., Манжула В.Г., Белич С.С. Мультидифференциальный операционный усилитель с малым напряжением смещения нуля в условиях температурных и радиационных воздействий // Научно-технические ведомости СПбГПУ. Информатика, Телекоммуникации. Управление. СПб: Изд-во СПбГПУ, 2010. №3 (101). - С. 204-206.

15. Крутчинский С.Г., Старченко Е.И. Мультидифференциальные усилители и прецизионная схемотехника // Электроника и связь, №21, том 9, 2004, Киев. - С.101-107.

16. Прокопенко Н.Н., Бутырлагин Н.В., Пахомов И.В. Основные параметры и уравнения базовых схем включения мультидифференциальных операционных усилителей с высокоимпедансным узлом // Проблемы разработки перспективных микро- и наноэлектронных систем - 2014. Сборник трудов. Часть 3 /под общ. ред. академика РАН А.Л. Стемпковского. - М.: ИППМ РАН, 2014. - С.111-116.

17. Prokopenko N.N., Dvornikov O.V., Butyrlagin N.V., Bugakova A.V. The main connection circuits of the radiation-hardened differential difference amplifier based on the bipolar and field effect technological process //2014 12th International conference on actual problems of electronic instrument engineering (APEIE - 2014) proceedings in 7 Volumes; Novosibirsk, October 2-4, 2014. - Novosibirsk: State Technical University. - Vol.1. - P. 29-34.

18. Прокопенко H.H., Будяков П.С., Бутырлагин H.B. Сверхвысокочастотные мультидифференциальные операционные усилители и основные схемы их включения (Circuit and connection design of microwave differential difference amplifiers) // 11-я Международная научно-техническая конференция «Актуальные проблемы электронного приборостроения»: Саратов, 25-26 сентября 2014 г.: материалы конф. в 2 т. - Саратов: Саратовский государственный технический университет имени Гагарина Ю.А., 2014. - Т. 2. - С. 100-107.

Мультидифференциальный операционный усилитель с малым напряжением смещения нуля, содержащий первый 1, второй 2 входные транзисторы, между эмиттерами которых включен первый 3 масштабирующий резистор, высокоимпедансный узел 4, третий 5 и четвертый 6 входные транзисторы, между эмиттерами которых включен второй 7 масштабирующий резистор, токовое зеркало 8, согласованное в первой 9 шиной источника питания, вход которого связан с коллекторами первого 1 и третьего 5 входных транзисторов, а выход подключен ко входу буферного усилителя 10 и объединенным коллекторам второго 2 и четвертого 6 входных транзисторов, первый 11 вспомогательный транзистор эмиттер которого связан со второй 12 шиной источника питания через первый 13 вспомогательный токостабилизирующий двухполюсник, а коллектор соединен с эмиттером первого 1 входного транзистора, второй 14 вспомогательный транзистор, эмиттер которого связан со второй 12 шиной источника питания через второй 15 вспомогательный токостабилизирующий двухполюсник, а коллектор соединен с эмиттером второго 2 входного транзистора, причем базы первого 11 и второго 14 вспомогательных транзисторов соединены друг с другом, третий 16 вспомогательный транзистор, эмиттер которого связан со второй 12 шиной источника питания через третий 17 вспомогательный токостабилизирующий двухполюсник, а коллектор соединен с эмиттером третьего 5 входного транзистора, четвертый 18 вспомогательный транзистор, эмиттер которого связан со второй 12 шиной источника питания через четвертый 19 вспомогательный токостабилизирующий двухполюсник, а коллектор соединен с эмиттером четвертого 6 входного транзистора, причем базы третьего 16 и четвертого 18 вспомогательных транзисторов подключены к источнику напряжения смещения 20, отличающийся тем, что базы первого 11 и второго 14 вспомогательных транзисторов соединены с эмиттером третьего 16 вспомогательного транзистора.